O 引言

隨著我國(guó)航空航天事業(yè)的迅猛發(fā)展,衛(wèi)星的應(yīng)用越來(lái)越廣泛。然而,太空環(huán)境復(fù)雜多變,其中存在著各種宇宙射線與高能帶電粒子,它們對(duì)運(yùn)行于其中的電子器件會(huì)產(chǎn)生各種輻射效應(yīng)。輻射效應(yīng)對(duì)電子器件的影響不可忽視,因?yàn)檩椛鋾?huì)使器件的性能參數(shù)發(fā)生退化,以至失效,從而影響衛(wèi)星的可靠運(yùn)行,縮短衛(wèi)星的使用壽命。輻射效應(yīng)對(duì)電子器件的影響很多,其中最主要的有總劑量效應(yīng)(TID)和單粒子效應(yīng)(S-EE)。SEE按產(chǎn)生的影響主要包括單粒子翻轉(zhuǎn)(SEU)、單粒子閂鎖(SEL)和單粒子燒毀(SEB)等三種類(lèi)型,其中以SEU最為常見(jiàn)。在各種輻射效應(yīng)當(dāng)中,存儲(chǔ)器對(duì)SEU最為敏感,所以,對(duì)存儲(chǔ)器的抗輻射設(shè)計(jì)首先要考慮的就是抗SEU設(shè)計(jì)。

事實(shí)上,不同的空間環(huán)境和應(yīng)用需求,對(duì)存儲(chǔ)器的數(shù)量與質(zhì)量也有不同的要求。例如:在上傳指令與下載星載儀器儀表的狀態(tài)時(shí),要求數(shù)據(jù)有很高的可靠性,此時(shí)對(duì)內(nèi)存容量則沒(méi)有特別的要求;而在處理某些用途的圖像數(shù)據(jù)時(shí),對(duì)數(shù)據(jù)可靠性的要求則相應(yīng)較低,此時(shí)則需要較大的內(nèi)存容量。所以在采用具體的抗SEU方法時(shí),也要因其不同情況而做出適合的選擇。

本文將采用擴(kuò)展?jié)h明碼編碼(Extended Hamming Code)與三模冗余(Triple Modular Redundancy,TMR)相結(jié)合的方法,并利用二者檢錯(cuò)糾錯(cuò)的不同特點(diǎn),來(lái)對(duì)SRAM進(jìn)行檢錯(cuò)糾錯(cuò)模式可調(diào)的抗SEU設(shè)計(jì)。這樣既可實(shí)現(xiàn)存儲(chǔ)器的抗SEU設(shè)計(jì)。又可滿足對(duì)存儲(chǔ)器使用靈活性的要求。

1 擴(kuò)展?jié)h明碼與TMR檢錯(cuò)糾錯(cuò)原理

1.1 擴(kuò)展?jié)h明碼檢錯(cuò)糾錯(cuò)原理

擴(kuò)展?jié)h明碼是一種常用的能檢測(cè)兩位錯(cuò)同時(shí)能糾正一位錯(cuò)的編碼方法。它是在漢明碼的基礎(chǔ)上.在碼字上再加入一個(gè)對(duì)所有碼元都進(jìn)行校驗(yàn)的校驗(yàn)位而得到的,故稱(chēng)為擴(kuò)展?jié)h明碼。

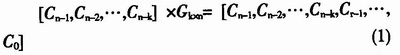

擴(kuò)展?jié)h明碼是線性分組碼的一種,其信息位和監(jiān)督位的關(guān)聯(lián)可由一組線性代數(shù)方程組表示。(n,k)線性分組碼的編碼就是去建立由r(其中r=n-k)個(gè)生成冗余位的方程式構(gòu)成的方程組,再由此方程組轉(zhuǎn)化為kxn的生成矩陣G。編碼時(shí),可將信息位向量(k維)乘以生成矩陣G,從而得到碼字向量(n維),如下式所示:

將式(1)表示的方程組作移位變換,可以得到式(2),通常稱(chēng)H為監(jiān)督矩陣。

解碼時(shí),通過(guò)監(jiān)督矩陣H與讀出的碼字向量C的乘積結(jié)果可判斷該碼字是否出錯(cuò)。若讀出的碼字向量C乘上監(jiān)督矩陣H后得到一個(gè)零向量,則表示沒(méi)有出錯(cuò);否則表示碼字在存儲(chǔ)之后受到了單粒子效應(yīng)的影響,有錯(cuò)誤發(fā)生。通常將監(jiān)督矩陣與讀出的碼字向量C的乘積記作S,稱(chēng)為校驗(yàn)子。當(dāng)碼字中某一位發(fā)生錯(cuò)誤時(shí),就會(huì)得到唯一的S向量,該向量只與碼字出錯(cuò)的位置有關(guān),而與碼字C無(wú)關(guān)。通過(guò)S向量可以定位出錯(cuò)的位置,并對(duì)出錯(cuò)數(shù)據(jù)進(jìn)行改正。

作為線性分組碼的一種,擴(kuò)展?jié)h明碼的分組編碼總長(zhǎng)為2r位,信息位長(zhǎng)度為2r-1-r位,即(2r,2r-l-r)擴(kuò)展?jié)h明碼。本設(shè)計(jì)采用了16位RAM存儲(chǔ)器,所以對(duì)應(yīng)使用(22,16)擴(kuò)展?jié)h明碼。

1.2 TMR檢錯(cuò)糾錯(cuò)原理

TMR是一種常見(jiàn)的硬件冗余技術(shù)。它的原理是在相同的一組硬件單元上同時(shí)發(fā)生錯(cuò)誤的概率要比在單一硬件單元上發(fā)生錯(cuò)誤的概率小。它的基本方法是將所需容錯(cuò)的硬件單元增加到三倍或更多,并將各個(gè)單元的輸出連接到一個(gè)表決器上,由表決器選擇所有硬件單元中的絕大多數(shù)輸出值作為整體的輸出值。圖1所示為三模冗余系統(tǒng)結(jié)構(gòu)圖。

圖1中,A1、A2、A3三個(gè)模塊同時(shí)執(zhí)行同樣的操作,并將其輸出送給表決器,然后由表決器對(duì)接收到的三路數(shù)據(jù)進(jìn)行比較。如果三個(gè)模塊同時(shí)給出三個(gè)相同的輸出,則表決器輸出任何一路作為正確輸出。如果其中任一模塊出錯(cuò),其輸出不同于其它兩個(gè)模塊,則表決器依然輸出正確結(jié)果。如果有兩個(gè)模塊同時(shí)出錯(cuò),且變成相同的狀態(tài),表決器則會(huì)誤認(rèn)為這是正確的結(jié)果并輸出,不過(guò)這種情況的出現(xiàn)雖然可能,但概率非常小。當(dāng)然,如果這兩個(gè)模塊同時(shí)出錯(cuò),但出錯(cuò)狀態(tài)不同,則表決器此時(shí)將無(wú)法做出選擇,但可以產(chǎn)生中斷。

2 內(nèi)存配置方案

通過(guò)上面對(duì)擴(kuò)展?jié)h明碼與TMR兩種檢錯(cuò)糾錯(cuò)方式的介紹,可以發(fā)現(xiàn)其二者各有優(yōu)勢(shì),分別適用于不同的環(huán)境條件和應(yīng)用需求。但是,這兩種方案對(duì)于內(nèi)存配置的要求是不同的,所以在對(duì)整個(gè)電路的設(shè)計(jì)之前,首先要對(duì)內(nèi)存作如下配置。

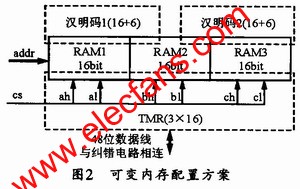

本設(shè)計(jì)中使用了3片16bit的SRAM。并分別采用(22,16)漢明碼和TMR兩種檢錯(cuò)糾錯(cuò)方法。對(duì)于(22,16),一般采用(16+8)位的存儲(chǔ)器來(lái)實(shí)現(xiàn),而TMR,則采用16位的存儲(chǔ)器來(lái)實(shí)現(xiàn)。若要支持這兩種方法,則必須首先為存儲(chǔ)器設(shè)計(jì)一種特別的內(nèi)存配置方式。本設(shè)計(jì)采用如圖2所示的內(nèi)存配置方案。

對(duì)于圖2所示的內(nèi)存配置方案,當(dāng)系統(tǒng)工作在TMR模式時(shí),所有的片選信號(hào)都被相同的信號(hào)驅(qū)動(dòng),這樣就構(gòu)成了TMR需要的3個(gè)16位內(nèi)存空間;而當(dāng)系統(tǒng)工作在漢明碼模式時(shí),它們則ah、al、bh為一組,bl、ch、cl為另一組,并分別被相同的片選信號(hào)驅(qū)動(dòng),從而構(gòu)成了兩個(gè)獨(dú)立的(16+8)位的內(nèi)存空間。本設(shè)計(jì)采用了3片128 K×16bit的SRAM,如果設(shè)置每片SRAM的低4K×16bit空間工作在TMR模式,則從圖中可以看出,該SRAM芯片組中還有兩個(gè)124 K×(16+8) bit的空間可以工作于擴(kuò)展?jié)h明碼模式。

3 電路設(shè)計(jì)

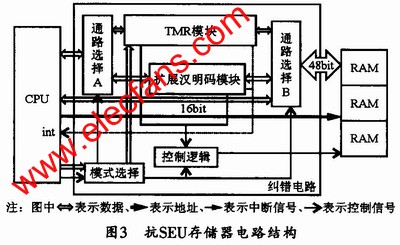

基于上述內(nèi)存配置方案,本文設(shè)計(jì)了如圖3所示的抗SEU存儲(chǔ)器電路。該電路包含了4個(gè)功能模塊。

3.1 TMR模塊

在TMR工作模式下可完成數(shù)據(jù)的寫(xiě)入操作和讀取操作中的冗余判決。如果在讀取過(guò)程中發(fā)現(xiàn)有一片RAM中的數(shù)據(jù)與其它三片不同,則對(duì)該片RAM進(jìn)行正確數(shù)據(jù)的回寫(xiě);如果發(fā)現(xiàn)三片RAM中的數(shù)據(jù)都不相同,則產(chǎn)生中斷信號(hào)。

3.2 擴(kuò)展?jié)h明碼模塊

在擴(kuò)展?jié)h明碼工作模式下,當(dāng)寫(xiě)入數(shù)據(jù)時(shí),則對(duì)其進(jìn)行編碼;當(dāng)讀取數(shù)據(jù)時(shí),則對(duì)其進(jìn)行相應(yīng)的解碼,并判斷數(shù)據(jù)是否出錯(cuò)。如果一位錯(cuò)則自動(dòng)回寫(xiě)正確值,如果兩位以上的錯(cuò)誤,則產(chǎn)生中斷信號(hào)。

3.3 模式選擇模塊

在該模塊內(nèi)部設(shè)置有一個(gè)32位的模式配置寄存器。通過(guò)給模式配置寄存器的低18位進(jìn)行預(yù)先置數(shù),可以設(shè)置檢錯(cuò)糾錯(cuò)電路的工作模式,同時(shí)也就設(shè)置了RAM的內(nèi)存配置情況。根據(jù)CPU的不同應(yīng)用要求,模式控制模塊可以讓檢錯(cuò)糾錯(cuò)電路在擴(kuò)展?jié)h明碼方式與TMR方式二者之間進(jìn)行靈活的切換。

3.4 控制邏輯模塊

該電路模塊可根據(jù)電路所處的檢錯(cuò)糾錯(cuò)模式來(lái)控制相應(yīng)的讀寫(xiě)信號(hào)和內(nèi)存片選信號(hào),以便正確訪問(wèn)RAM內(nèi)容。

4 FPGA的編程與實(shí)現(xiàn)

接下來(lái)對(duì)每個(gè)模塊在設(shè)計(jì)過(guò)程的具體考慮進(jìn)行重點(diǎn)介紹。

4.1 TMR模塊

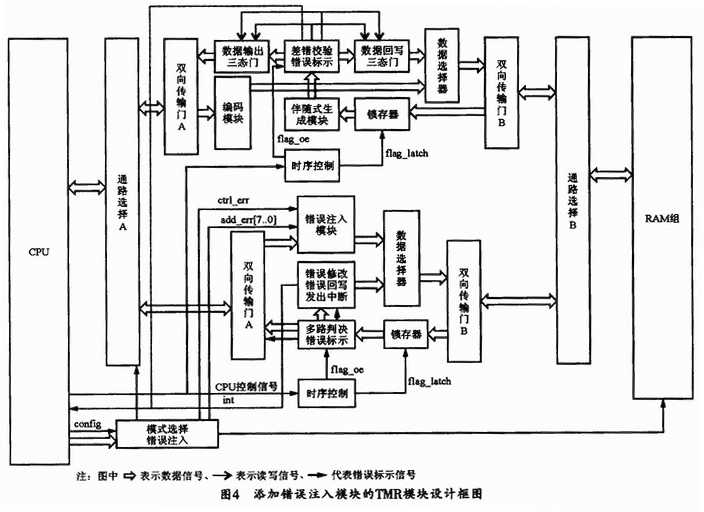

對(duì)于TMR模塊的設(shè)計(jì)較為簡(jiǎn)單。需要特別指出的是,考慮到對(duì)電路有效性的驗(yàn)證,在寫(xiě)通道上另外添加了錯(cuò)誤注入模塊。圖4所示是其設(shè)計(jì)框圖,圖中,ctrl_err為錯(cuò)誤注入控制信號(hào),當(dāng)ctrl_err為0時(shí),表示不注入錯(cuò)誤;當(dāng)ctrl_err為1時(shí),表示注入錯(cuò)誤。這樣可以通過(guò)對(duì)ct-rl_err信號(hào)的控制來(lái)實(shí)現(xiàn)對(duì)SEU效應(yīng)的模擬。add_err[7..0]為注錯(cuò)數(shù)據(jù)信號(hào)。將add_err的低四位用0000~1111表示,可用于表示給數(shù)據(jù)添加錯(cuò)誤的位置,它的高四位甩XX01~XX11表示,則可分別表示要給RAM組中的某個(gè)RAM添加錯(cuò)誤。

4.2 擴(kuò)展?jié)h明碼模塊

擴(kuò)展?jié)h明碼模塊的設(shè)計(jì)主要包括編碼模塊、伴隨式生成模塊以及差錯(cuò)校驗(yàn)?zāi)K等。編碼模塊可使用式(1)進(jìn)行編碼,可生成r個(gè)校驗(yàn)位。并將它們依次添加到碼元序列的第2i-1(其中i=0,…,r-1)個(gè)位置上。伴隨式生成模塊使用式(2)進(jìn)行解碼,可對(duì)應(yīng)生成校驗(yàn)子S。差錯(cuò)控制模塊可根據(jù)生成的校驗(yàn)子S來(lái)判斷數(shù)據(jù)是否出錯(cuò),以及出錯(cuò)的位數(shù),并用sef與def表示。如果數(shù)據(jù)沒(méi)有出現(xiàn)錯(cuò)誤,則直接送出;如果數(shù)據(jù)中有一位出現(xiàn)錯(cuò)誤,則對(duì)其進(jìn)行回寫(xiě),同時(shí)將修正的數(shù)據(jù)送出;如果兩位出現(xiàn)錯(cuò)誤,則輸出中斷信號(hào)int。

需要注意的是,擴(kuò)展?jié)h明碼模式下的地址信號(hào)需要進(jìn)行額外的處理。由于本設(shè)計(jì)采用了128K×16bit的SRAM芯片,它有17位地址信號(hào)。但是,正如上面提到過(guò)的,SRAM芯片組中將有4KB的存儲(chǔ)空間工作于TMR模式,還有248KB的存儲(chǔ)空間將工作于擴(kuò)展?jié)h明碼模式,而248KB的空間需要18位地址信號(hào),這就要求有一個(gè)對(duì)地址信號(hào)進(jìn)行變換的模塊。當(dāng)?shù)刂沸∮?KB 時(shí),電路工作于TMR模式下而無(wú)需對(duì)地址進(jìn)行變換;當(dāng)?shù)刂反笥诘扔? KB同時(shí)小于128 KB時(shí),電路工作于擴(kuò)展?jié)h明碼模式,地址信號(hào)會(huì)選中第一個(gè)124 Kx(16+8)bit的空間,此時(shí)也無(wú)需地址變換;而當(dāng)?shù)刂反笥诘扔?28 KB,電路也工作于擴(kuò)展?jié)h明碼模式下,此時(shí)地址信號(hào)應(yīng)選中第二個(gè)124 Kx(16+81bit的空間,此時(shí)則應(yīng)將地址值加上4KB,然后取新的地址的低17位加到第二個(gè)124 Kx (16+8) bit的存儲(chǔ)空間上即可。

在上述TMR和擴(kuò)展?jié)h明碼模塊的設(shè)計(jì)中,對(duì)出錯(cuò)數(shù)據(jù)的回寫(xiě)是設(shè)計(jì)中的重點(diǎn)和難點(diǎn),主要應(yīng)考慮是否回寫(xiě)和何時(shí)回寫(xiě)兩個(gè)問(wèn)題。這兩個(gè)問(wèn)題可由時(shí)序控制模塊來(lái)解決。它主要根據(jù)CPU的控制信號(hào),適時(shí)的發(fā)出錯(cuò)誤標(biāo)示輸出使能信號(hào)flag_oe,從而改變CPU對(duì)RAM的讀寫(xiě)狀態(tài),完成

修正數(shù)據(jù)的正確回寫(xiě)。

另外,電路中的錯(cuò)誤標(biāo)示信號(hào)對(duì)整體設(shè)計(jì)的穩(wěn)定性至關(guān)重要。為了保證錯(cuò)誤標(biāo)示信號(hào)的穩(wěn)定,可在雙向傳輸門(mén)B的讀入端加一個(gè)鎖存器,鎖存器的鎖存使能端也可由時(shí)序控制模塊的flag_latch來(lái)控制。

4.3 模式選擇模塊

模式選擇模塊用于接收來(lái)自CPU的配置信號(hào)config和片選信號(hào)cs_fpga,以便將32位的配置數(shù)據(jù)寫(xiě)入配置寄存器。該寄存器的低18位數(shù)據(jù)為模式配置數(shù)據(jù),地址信號(hào)通過(guò)與該數(shù)據(jù)進(jìn)行比較,可使小于該地址的存儲(chǔ)器空間工作于TMR模式,大于該地址的存儲(chǔ)空間工作于擴(kuò)展?jié)h明碼模式。

本電路采用軟件故障注入法來(lái)進(jìn)行電路的有效性驗(yàn)證,所以,在電路設(shè)計(jì)中,可將模式配置寄存器的其余14位用于注入外部干擾數(shù)據(jù),并將其連接到ctrl_err與add_err信號(hào),以用來(lái)進(jìn)行軟件故障的注入,模擬SEU對(duì)電路的影響。

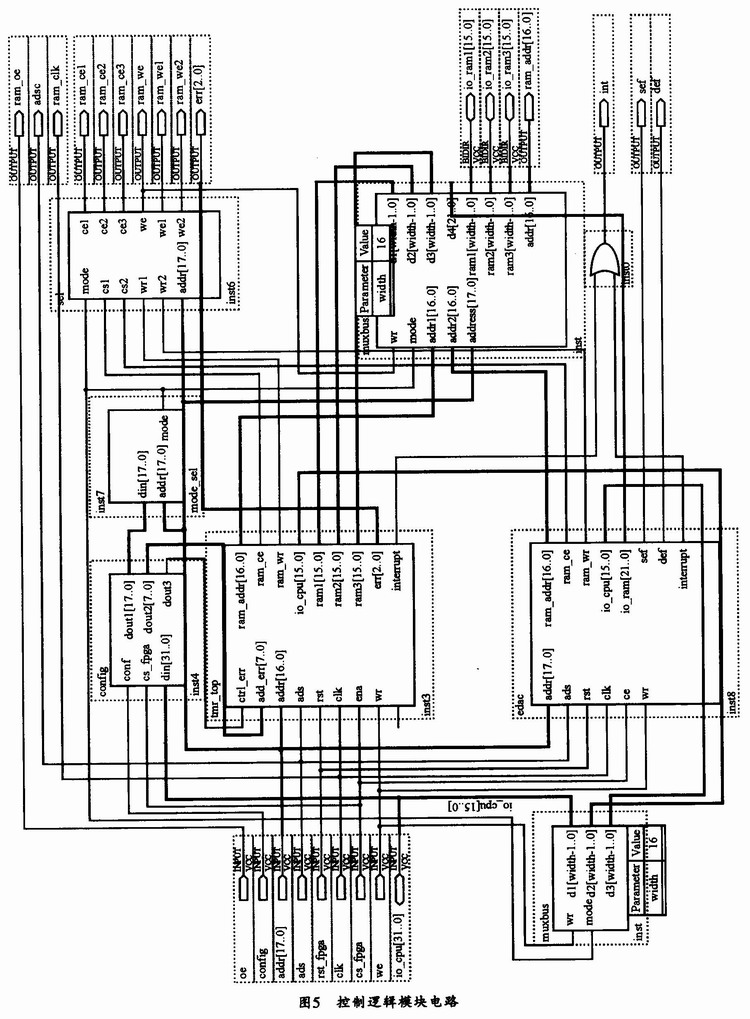

4.4 控制邏輯模塊

該模塊可接收模式選擇模塊的模式信號(hào)mode,以對(duì)TMR模塊和擴(kuò)展?jié)h明碼模塊輸出的讀寫(xiě)信號(hào)和片選信號(hào)進(jìn)行選擇,然后輸出到RAM芯片的引腳上去,從而實(shí)現(xiàn)CPU對(duì)RAM的正確訪問(wèn)。尤其是當(dāng)電路工作于擴(kuò)展?jié)h明碼模式時(shí),還需根據(jù)地址信號(hào)判斷當(dāng)前對(duì)哪個(gè)124 Kx (16+8)bit的存儲(chǔ)空間片選有效。其具體電路如圖5所示。

5 結(jié)束語(yǔ)

本設(shè)計(jì)中的抗SEU存儲(chǔ)器的設(shè)計(jì)可通過(guò)ACTEL的ProAsic系列A3P400 FPGA實(shí)現(xiàn),并可使用與其配套的Libero8.5 EDA工具進(jìn)行代碼的編輯和原理圖的繪制,并進(jìn)行功能仿真與電路的綜合。通過(guò)仿真可以看到,本設(shè)計(jì)可以達(dá)到預(yù)期的目的,它既可實(shí)現(xiàn)存儲(chǔ)器的抗SEU設(shè)計(jì),又可以滿足對(duì)存儲(chǔ)器使用靈活性的要求,而且具有功能完善、適應(yīng)性強(qiáng)、電路簡(jiǎn)單等特點(diǎn),非常適用于星載RAM的抗輻射電路設(shè)計(jì)。