1.引言

在工業(yè)現(xiàn)場(chǎng),、國(guó)防軍事,、航空航天等領(lǐng)域需要利用電路自身資源進(jìn)行快速的故障診斷,,即要求電路具有自測(cè)試功能,。為了使復(fù)雜的電路具有自測(cè)試功能必須進(jìn)行專門的可測(cè)性分析與設(shè)計(jì)[1],。而通過(guò)建立故障診斷模型來(lái)研究復(fù)雜系統(tǒng)的可測(cè)性是一種準(zhǔn)確并有效的方法,。利用層次性依賴模型,設(shè)計(jì)者能將各個(gè)子系統(tǒng)整合成一個(gè)具有層次結(jié)構(gòu)的完整體系,。在這一完整系統(tǒng)模型框架下,,進(jìn)行系統(tǒng)的可測(cè)性分析,并確定整個(gè)系統(tǒng)可測(cè)性設(shè)計(jì)與故障診斷方案[2-3] ,。

多信號(hào)模型從信號(hào)的多維屬性著手,,改進(jìn)了依賴性模型結(jié)構(gòu)中的故障影響關(guān)系分析不完整的不足,同時(shí)兼顧結(jié)構(gòu)化模型建模簡(jiǎn)單快速的優(yōu)點(diǎn),,在大型復(fù)雜系統(tǒng)中得到了成功應(yīng)用[4-7] ,。多信號(hào)為模型區(qū)分故障對(duì)系統(tǒng)功能的影響效果定義了功能故障和完全故障。多信號(hào)模型解決結(jié)構(gòu)性失真的辦法是找出組件影響的信號(hào)與測(cè)試點(diǎn)所能檢測(cè)到的信號(hào)的因果關(guān)系[8-10] ,。

高速數(shù)據(jù)采集器由FPGA,、DSP 等大規(guī)模集成電路組成,是典型的板級(jí)電路,。廣泛地應(yīng)用于工業(yè),、農(nóng)業(yè)及國(guó)防領(lǐng)域領(lǐng)域。本文采用多信號(hào)模型對(duì)數(shù)據(jù)采集器進(jìn)行了可測(cè)性分析與可測(cè)性設(shè)計(jì),,使高速數(shù)據(jù)采集具有自測(cè)試功能,,提高其故障檢測(cè)率及故障隔離率,,解決現(xiàn)場(chǎng)對(duì)板級(jí)電路要求快速進(jìn)行故障診斷及故障定位的要求。

2.高速數(shù)據(jù)采集器的多信號(hào)流建模

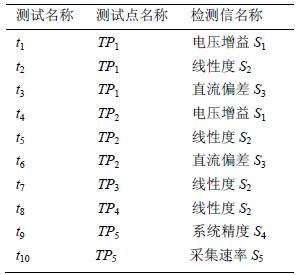

原數(shù)據(jù)采集系統(tǒng)未考慮可測(cè)性,,系統(tǒng)本身可以提供的測(cè)試信息有限,,大量重要測(cè)試數(shù)據(jù)和關(guān)鍵參數(shù)無(wú)法獲取。一些參數(shù)可以測(cè)到但無(wú)法實(shí)現(xiàn)板級(jí)自測(cè)試,,而一些參數(shù)無(wú)法測(cè)得,。所以原始采集器的可用信號(hào)有5 個(gè),用字母S 表示:S1-增益,、S2-線性度,、S3-直流偏差、S4-系統(tǒng)精度,,S5-采集速率,。數(shù)據(jù)采集器共有9 個(gè)模塊,每個(gè)模塊有功能故障(符號(hào)為F)和完全故障(符號(hào)為G)兩個(gè)故障,,共18 個(gè)故障,,找出組成單元與信號(hào)的影響關(guān)系,如表1 所示,。

表1 元件與信號(hào)關(guān)聯(lián)關(guān)系

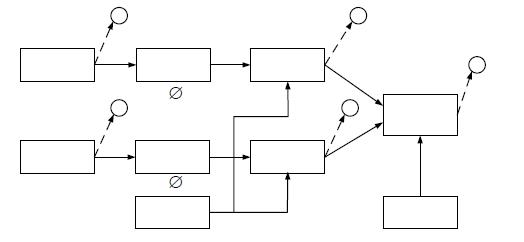

制定的電路功能測(cè)試診斷方案,,設(shè)置測(cè)試點(diǎn)和測(cè)試,內(nèi)容見(jiàn)表2,。由此可以建立數(shù)據(jù)采集器的多信號(hào)模型[11],,如圖1 所示。

表2 測(cè)試名稱,、位置和檢測(cè)信號(hào)名稱

模型的形式化定義如下。

系統(tǒng)組成單元集C={放大電路1,、放大電路2,、濾波電路1、濾波電路2,、上路AD 轉(zhuǎn)換模塊,,下路AD 轉(zhuǎn)換模塊、鎖相環(huán)模塊,、DSP 模塊和FPGA 模塊},。

信號(hào)集S = {S1,S2,,S3,,S4,S5};測(cè)試點(diǎn)TP = { TP1,、TP2,、TP3,、TP4、TP5};

測(cè)試集T = {t1,,t2,,t3,t4,,t5,,t6,t7,,t8,,t9,t10};

元件信號(hào)集SC(ci) ={};

測(cè)試點(diǎn)包含測(cè)試集SP={SP(TP1),,SP(TP2),,SP(TP3),SP(TP4),,SP(TP5)};

測(cè)試信號(hào)集ST={ ST(t1),,ST(t2),…,,ST(t10)};

圖1 數(shù)據(jù)采集器的多信號(hào)模型

3.高速數(shù)據(jù)采集器可測(cè)性

設(shè)計(jì)多信號(hào)模型的分析結(jié)果可以指導(dǎo)可測(cè)性設(shè)計(jì),,為設(shè)計(jì)人員指出系統(tǒng)難于測(cè)試的硬件缺陷,測(cè)試點(diǎn)和測(cè)試選擇的不合理之處,。通過(guò)模型分析也可以判斷系統(tǒng)的模塊和功能劃分是否合理,。基于多信號(hào)模型的可測(cè)性分析可以解決如下幾個(gè)系統(tǒng)設(shè)計(jì)問(wèn)題,,直接指明可測(cè)性設(shè)計(jì)的具體方向,。

(1)模型劃分的合理性。多信號(hào)模型的模塊劃分方案可以作為系統(tǒng)實(shí)際設(shè)計(jì)的劃分方案,。合理的功能和結(jié)構(gòu)劃分是提高硬件自身的測(cè)試特性的重要手段,。劃分是要從產(chǎn)品層次、結(jié)構(gòu)和電氣等角度把復(fù)雜系統(tǒng)劃分為較簡(jiǎn)單,、可單獨(dú)測(cè)試的單元容易進(jìn)行,。

(2)信號(hào)選擇的局限性。特征信號(hào)的多樣性給板級(jí)電路測(cè)試帶來(lái)難度,。由于設(shè)計(jì)者在功能設(shè)計(jì)時(shí)未對(duì)關(guān)鍵信號(hào)的檢測(cè)給予硬件支持,,使得系統(tǒng)的固有測(cè)試特性降低。無(wú)論怎樣設(shè)計(jì)診斷策略都無(wú)法隔離所有故障,。建模時(shí)進(jìn)行的信號(hào)定義和依賴性分析提出了若干備選信號(hào),,其中有相當(dāng)一部分是無(wú)法在缺少板級(jí)測(cè)試設(shè)備的情況下檢測(cè)的。此時(shí),,以部分信號(hào)來(lái)達(dá)到隔離全部故障的目的顯然是不現(xiàn)實(shí)的,。而多信號(hào)模型在信號(hào)分析時(shí)能夠指明系統(tǒng)現(xiàn)有信號(hào)集與完整信號(hào)集的差集,。設(shè)計(jì)者可以根據(jù)差集中的信號(hào)設(shè)計(jì)檢測(cè)電路并提供測(cè)試通道。

(3)測(cè)試施加的有效性,。存在冗余測(cè)試說(shuō)明測(cè)試的選擇過(guò)多,,造成了測(cè)試資源的浪費(fèi)。根本原因是多余的測(cè)試未能提供新的故障信息,,無(wú)助于故障的隔離,。這表明單純?cè)黾訙y(cè)試點(diǎn)和測(cè)試并無(wú)宜于改善可測(cè)性,應(yīng)該使得新增測(cè)試所檢測(cè)的故障信息與現(xiàn)有測(cè)試檢測(cè)到的故障信息既有交集又不完全相同,。

本文根據(jù)多信號(hào)模型的可測(cè)性分析結(jié)果進(jìn)行可測(cè)性設(shè)計(jì)過(guò)程如下,。

(1)原數(shù)據(jù)采集器器根據(jù)實(shí)際功能劃分,即分為信號(hào)調(diào)理,、模數(shù)轉(zhuǎn)換,、等周期采樣和總體控制四個(gè)主要模塊。物理劃分方面上,,各模塊之間留有足夠空間以方便各模塊測(cè)試激勵(lì)的引入和被檢測(cè)信息的傳遞,。

(2)根據(jù)信號(hào)定義發(fā)現(xiàn)現(xiàn)有信號(hào)集有5 個(gè)元素。造成原數(shù)據(jù)采集器的可測(cè)性指標(biāo)較低的一個(gè)原因就是可用信號(hào)數(shù)量少,。這是受系統(tǒng)結(jié)構(gòu)所限,。對(duì)于板級(jí)系統(tǒng),某些指標(biāo)由于缺少檢測(cè)設(shè)備而無(wú)法測(cè)試;有些指標(biāo)由于缺少測(cè)試通道使得測(cè)試數(shù)據(jù)無(wú)法采集;有些指標(biāo)由于與系統(tǒng)正常功能無(wú)關(guān)而被設(shè)計(jì)者忽略了,?;诖耍瑢?duì)數(shù)據(jù)采集器重新設(shè)計(jì)以增加可用信號(hào),,改善可測(cè)性,。

①在FPGA 內(nèi)設(shè)計(jì)可調(diào)節(jié)輸入信號(hào)產(chǎn)生電路DSP 模塊控制,。

?、诮刂诡l率測(cè)試電路,通過(guò)輸入方波采集輸出平均電壓的方式,,獲取濾波器的截止頻率。

?、塾蒁SP 控制專用邊界掃描芯片完成具有邊界掃描結(jié)構(gòu)芯片的測(cè)試,。主要實(shí)現(xiàn)FPGA 內(nèi)核邏輯的測(cè)試。

?、馨袴PGA 內(nèi)的邏輯電路依據(jù)功能進(jìn)行分塊設(shè)計(jì),,原則就是要盡可能減少邏輯電路模塊之間的信號(hào)聯(lián)系,使模塊電路的輸入信號(hào)數(shù)目減少,。

?、軫PGA 內(nèi)部設(shè)計(jì)數(shù)據(jù)采集器獲取鎖相環(huán)輸出頻率,。

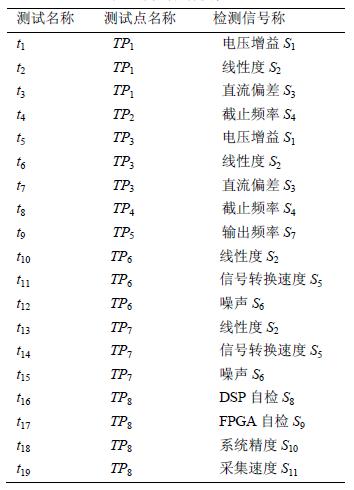

通過(guò)重新設(shè)計(jì)使得原數(shù)據(jù)采集器不能測(cè)試的參數(shù)都可以作為信號(hào)了。現(xiàn)在增加6 個(gè)信號(hào):截止頻率,、轉(zhuǎn)換速度,、噪聲、PLL 輸出頻率,、DSP 自檢指標(biāo)和FPGA 自檢指標(biāo),。所以現(xiàn)在選取的信號(hào)有11 個(gè),重新編號(hào)后顯示如下,。S1-增益,、S2-線性度、S3-直流偏差,、S4-截止頻率,,S5-轉(zhuǎn)換速度,S6-轉(zhuǎn)換噪聲,,S7- PLL 輸出頻率,,S8-轉(zhuǎn)換速度,S9- FPGA 自檢指標(biāo),,S10-系統(tǒng)精度,,S11-采集速率。新的信號(hào)與元件依賴關(guān)系見(jiàn)表3,。

表3 元件與信號(hào)關(guān)聯(lián)關(guān)系

(3)新信號(hào)的加入使得系統(tǒng)必須增加新的測(cè)試點(diǎn)和新的測(cè)試項(xiàng)目,。新的測(cè)試方案增加了4 個(gè)測(cè)試點(diǎn),為檢測(cè)所有信號(hào)使得測(cè)試增加到了19 個(gè),,對(duì)新模型重新進(jìn)行可測(cè)性分析后發(fā)現(xiàn)有4 個(gè)冗余測(cè)試,。所以新測(cè)試方案含有15 個(gè)測(cè)試項(xiàng)目。具體測(cè)試項(xiàng)目的名稱,、測(cè)試內(nèi)容和測(cè)試位置見(jiàn)表4,。

進(jìn)可測(cè)性設(shè)計(jì)后,原來(lái)未檢測(cè)故障已能檢測(cè)到,,故障檢測(cè)率有原來(lái)的1.72% 提高到100% ;并且所有未隔離故障均以隔離到一個(gè)模塊,,使得所有故障全部區(qū)分開(kāi),即故障隔離率有設(shè)計(jì)前的12.97% 提高到100% ,??蓽y(cè)性設(shè)計(jì)后的數(shù)據(jù)采集器的可測(cè)性分析結(jié)果與原數(shù)據(jù)采集的分析結(jié)果列于表5,由此表可以看出可測(cè)性提高效果,。

4. 結(jié)論

本文通過(guò)建立高速數(shù)據(jù)采集器的多信號(hào)流模型,,對(duì)數(shù)據(jù)采集器進(jìn)行了可測(cè)性分析與可測(cè)性設(shè)計(jì),通過(guò)可測(cè)性設(shè)計(jì)其故障檢測(cè)率和故障隔離率均達(dá)到100% ,,在此基礎(chǔ)上可以通過(guò)DSP 完成整個(gè)電路的自測(cè)試,。本文的研究成果為提高電路的自測(cè)試能力奠定基礎(chǔ),,可適應(yīng)現(xiàn)場(chǎng)快速故障診斷和故障定位的需要。本文作者創(chuàng)新點(diǎn):提出了一種板級(jí)電路內(nèi)建自測(cè)試建模技術(shù),,針對(duì)原有電子系統(tǒng)增加內(nèi)建自測(cè)試的可測(cè)性技術(shù),,并采用多信號(hào)流作為評(píng)估方法,通過(guò)實(shí)際系統(tǒng)驗(yàn)證了所提出方法的可行性和實(shí)際價(jià)值,。

表4 測(cè)試名稱及位置

表5 可測(cè)性改善對(duì)比表