摘 要: 提出了一種利用FIR濾波器系數(shù)對(duì)稱性、CSD編碼和數(shù)據(jù)選擇器" title="數(shù)據(jù)選擇器">數(shù)據(jù)選擇器簡(jiǎn)化MQAM調(diào)制器設(shè)計(jì)的新方法。用該方法在FPGA上實(shí)現(xiàn)4、16、64、256QAM調(diào)制器。實(shí)驗(yàn)證明該方法在硬件資源消耗和工作時(shí)鐘頻率方面都有較大的改善。

關(guān)鍵詞: 多電平正交振幅調(diào)制(MQAM) FIR CSD

隨著移動(dòng)用戶數(shù)量的不斷增加和人們對(duì)圖像等多媒體信息的通信要求,傳統(tǒng)通信系統(tǒng)的容量已經(jīng)越來(lái)越不能滿足要求,而可用頻譜資源有限,也不能靠無(wú)限增加頻道數(shù)目來(lái)解決系統(tǒng)容量問(wèn)題。確定一種高頻譜利用率的調(diào)制方案能在很大程度上解決這一問(wèn)題。多電平正交振幅調(diào)制(Multilevel Quadrature Amplitude Modulation)是一種具有高頻譜利用率的調(diào)制技木[1]。在無(wú)線通信中,它可以根據(jù)信道的衰落程度、信道流量等參數(shù)動(dòng)態(tài)改變調(diào)制方式,提高信道利用率和信息傳輸速率。這種高效的數(shù)據(jù)傳輸方式實(shí)現(xiàn)的關(guān)鍵是FIR(Finite Impulse Response)濾波器和數(shù)字混頻器" title="混頻器">混頻器的設(shè)計(jì),它們通常限制了調(diào)制器的速率。本文采用基于CSD(Canonic Signed Digit)編碼的FIR濾波器,并利用FIR濾波器系數(shù)對(duì)稱性、數(shù)據(jù)選擇器實(shí)現(xiàn)模塊重用,簡(jiǎn)化MQAM調(diào)制器設(shè)計(jì),既節(jié)約了硬件資源又提高了器件的工作頻率" title="工作頻率">工作頻率。

1 MQAM調(diào)制器設(shè)計(jì)

MQAM調(diào)制框圖[2]如圖1所示。

MQAM和調(diào)制器由串并轉(zhuǎn)換" title="串并轉(zhuǎn)換">串并轉(zhuǎn)換、IQ分路、脈沖形成和調(diào)制混頻單元組成。串并轉(zhuǎn)換單元將串行的數(shù)據(jù)流轉(zhuǎn)化為并行的數(shù)據(jù)流;IQ分路單元根據(jù)不同的調(diào)制星座要求,將輸入的信號(hào)分解成同相和正交分量(I路和Q路信號(hào)分量);脈沖形成濾波器對(duì)I、Q兩路信號(hào)進(jìn)行波形形成;調(diào)制混頻單元對(duì)I、Q兩路信號(hào)進(jìn)行混頻、合成,形成調(diào)制信號(hào)輸出。

1.1 串并轉(zhuǎn)換

串并轉(zhuǎn)換通過(guò)log2 M級(jí)移位寄存器實(shí)現(xiàn),調(diào)制方式控制字控制串并轉(zhuǎn)換單元的工作時(shí)鐘頻率。若數(shù)據(jù)輸入的速率為f,則串并轉(zhuǎn)換單元的工作頻率是f/log2 M。輸入數(shù)據(jù)按log2 M個(gè)比特一組起作用,輸入的二進(jìn)制數(shù)據(jù)分別進(jìn)入log2 M個(gè)信道,每個(gè)信道的比特率等于輸入比特速率的1/log2 M,log2 M比特串行輸入比特分離器,然后同時(shí)并行輸出,信號(hào)進(jìn)入IQ分路單元。

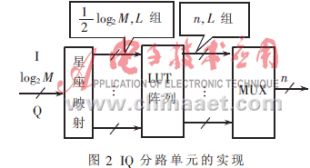

1.2 IQ分路單元

圖2是IQ分路的實(shí)現(xiàn)框圖。L為輸入和輸出查找表" title="查找表">查找表的數(shù)據(jù)線組數(shù),數(shù)值上等于MQAM調(diào)制器的調(diào)制方式種數(shù),如實(shí)現(xiàn)4、16、64、256QAM調(diào)制器,則L=4。寬度為log2 M的數(shù)據(jù)輸入星座映射模塊,根據(jù)調(diào)制方式控制字,星座映射的L組輸出線中,相應(yīng)的一組起作用,輸入數(shù)據(jù)被映射為寬度為![]() log2 M的數(shù)據(jù)輸出,作為查找表陣列中對(duì)應(yīng)查找表的地址輸入。查找表中存儲(chǔ)的是與調(diào)制方式對(duì)應(yīng)的數(shù)據(jù),位寬n根據(jù)需要的精度設(shè)定。由于I、Q兩路查找表數(shù)據(jù)一樣,可以控制在不同的時(shí)刻使星座映射單元映射輸出不同的地址,使I、Q兩路使用同一個(gè)查找表,這樣星座映射單元輸出數(shù)據(jù)的頻率為2f/log2 M,I、Q兩路的輸出相差一個(gè)查找表的工作時(shí)鐘。最后,數(shù)據(jù)選擇器根據(jù)控制字選擇一組作為IQ分路單元的輸出。

log2 M的數(shù)據(jù)輸出,作為查找表陣列中對(duì)應(yīng)查找表的地址輸入。查找表中存儲(chǔ)的是與調(diào)制方式對(duì)應(yīng)的數(shù)據(jù),位寬n根據(jù)需要的精度設(shè)定。由于I、Q兩路查找表數(shù)據(jù)一樣,可以控制在不同的時(shí)刻使星座映射單元映射輸出不同的地址,使I、Q兩路使用同一個(gè)查找表,這樣星座映射單元輸出數(shù)據(jù)的頻率為2f/log2 M,I、Q兩路的輸出相差一個(gè)查找表的工作時(shí)鐘。最后,數(shù)據(jù)選擇器根據(jù)控制字選擇一組作為IQ分路單元的輸出。

1.3 脈沖形成濾波器

脈沖形成濾波器采用FIR濾波器,F(xiàn)IR濾波器公式[3]:

FIR濾波器的系數(shù)是偶對(duì)稱或者奇對(duì)稱,即有:

h(n)=h(N-1-n)(偶對(duì)稱)或者h(yuǎn)(n)=-h(N-1-n)(奇對(duì)稱) (2)

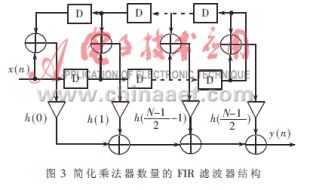

利用系數(shù)對(duì)稱性減少乘法器數(shù)量的FIR濾波器結(jié)構(gòu)如圖3所示。

在濾波器參數(shù)確定后,系數(shù)是一個(gè)固定值,所以濾波器的所有乘法都是固定系數(shù)乘法。實(shí)現(xiàn)固定系數(shù)乘法就可以用移位、加/減來(lái)代替并行乘法。任何濾波器系數(shù)都可表示成CSD碼[4~5]的形式,這樣加減法的次數(shù)就可以達(dá)到最少,對(duì)理想濾波器的系數(shù)進(jìn)行CSD量化可簡(jiǎn)化硬件實(shí)現(xiàn)時(shí)乘法器部分的結(jié)構(gòu)。

二進(jìn)制補(bǔ)碼與CSD編碼的轉(zhuǎn)換方法如下:

一個(gè)數(shù)X=x(n-1)x(n-2)…x(0),如果對(duì)于所有i=0,1,...,n-1,x(i) =0,1,或-1,且對(duì)于所有i=1,…,n-1,滿足x(i)x(i-1)=0,則X=x(n-1)x(n-2)…x(0)稱為X的CSD編碼表示。

一個(gè)數(shù)的CSD表示中的非0比特位總是不相鄰的,用一個(gè)2bit的二進(jìn)制數(shù)表示一個(gè)CSD碼中的非0比特?cái)?shù),01代表+1,11代表-1(最高位通過(guò)符號(hào)位擴(kuò)展實(shí)現(xiàn)),則可以將一個(gè)數(shù)的CSD編碼表示轉(zhuǎn)換為二進(jìn)制CSD編碼(BCSD)表示。二者具有一一對(duì)應(yīng)關(guān)系。根據(jù)上述原理,一種將二進(jìn)制補(bǔ)碼數(shù)變換得到其CSD編碼表示的過(guò)程描述為:首先將二進(jìn)制補(bǔ)碼表示轉(zhuǎn)換為稱為BCSD編碼的表示,然后按照01代表+1,11代表-1相反的過(guò)程轉(zhuǎn)換BCSD編碼得到數(shù)的CSD編碼表示。一種將二進(jìn)制補(bǔ)碼數(shù)轉(zhuǎn)換得到BCSD編碼的算法描述如下:

(1)初始化:輸入X=x(n-1)x(n-2)…x(0);符號(hào)擴(kuò)展x(n)=x(n-1);計(jì)數(shù)器置0(i=0);標(biāo)志位置0(f=0)。

(2)循環(huán)執(zhí)行下列語(yǔ)句:如果i>n-1,則跳轉(zhuǎn)到(3),否則繼續(xù)執(zhí)行下列語(yǔ)句:

①如果f=0:如果x(i+1)x(i)=11,則f=1,i=i+2;如果x(i+1)x(i)=01,則f=0,i=i+2;否則,f=0,i=i+1。

②如果f=1:如果x(i+1)x(i)=00,則f=0,x(i)=1,i=i+2;如果x(i+1)x(i)=10,則f=1,x(i)=1,i=i+2;否則,f=0,x(i)=0,i=i+1。

③返回到(2)。

(3)如果f=1,則x(i)=!x(i);否則,x(i)=x(i)。

(4)結(jié)束。

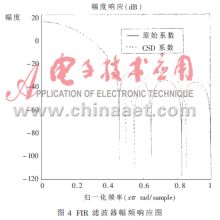

本文采用12抽頭hamming形式的低通濾波器,截止頻率為0.15。為了便于CSD量化,將最大濾波器系數(shù)歸一化,其余各系數(shù)也乘以相應(yīng)的常數(shù),濾波器特性沒(méi)有改變。表1是濾波器系數(shù),圖4是原始系數(shù)與CSD編碼系數(shù)FIR濾波器幅頻響應(yīng)圖。

1.4 調(diào)制混頻器的設(shè)計(jì)

混頻器輸出信號(hào)[6]為:

s(k)=I(k)cos(2πkfc/fd)+Q(k)sin(2πkfc/fd) (3)

其中,fd為DDS的工作頻率,當(dāng)fd=4 fc時(shí),得到:

s(k)=I(k)cos(πk/2)+Q(k)sin(πk/2) (4)

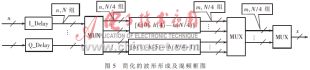

以上兩式中,1≤k≤∞,cos(πk/2)可以表示為1,0,-1,0…的序列,sin(πk/2)可以表示為0,1,0,-1...的序列。設(shè)同相路I(f)的樣本序列I(k)為I1,I2,I3…,正交路Q(f)的樣本序列Q(k)為Q1,Q2,Q3…,則S(k)的樣本序列為I1,Q2,-I3,-Q4,I5,Q6…。這樣,正交調(diào)制就可以簡(jiǎn)化成子濾波器和數(shù)據(jù)選擇器構(gòu)成。如圖5所示,輸出由每一個(gè)時(shí)刻使能不同的子濾波器得到。這種結(jié)構(gòu)適合高速設(shè)計(jì),而且占用硬件資源少,輸出時(shí)鐘是子濾波器時(shí)鐘的2倍。

其中,N為濾波器的抽頭數(shù),又由上面的分析可以知道輸出序列可以表示為:

h(0)x(n)+h(4)x(n-4)+h(8)x(n-8)+…(5)

h(1)x(n-1)+h(5)x(n-5)+h(9)x(n-9)+…(6)

-h(2)x(n-2)-h(6)x(n-6)-h(10)x(n-10)-…(7)

-h(3)x(n-3)-h(7)x(n-7)-h(11)x(n-11)-… (8)

綜合(2)(5)(6)(7)(8)可以看出,(5)(8)可以用同一組濾波器實(shí)現(xiàn),(6)(7)可以用同一組濾波器實(shí)現(xiàn),濾波器組的輸入是N/4組寬度為n的數(shù)據(jù),輸出是 N/4組寬度為m的數(shù)據(jù),m與查找表和濾波器系數(shù)的位寬有關(guān),利用數(shù)據(jù)選擇器選擇一組濾波器組輸出送到加法器,最后即為調(diào)制混頻輸出,位寬x根據(jù)需要確定。

2 MQAM調(diào)制器各部分工作時(shí)鐘

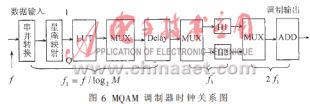

MQAM調(diào)制器各模塊工作時(shí)鐘關(guān)系如圖6所示。

輸入速率為f的串行數(shù)據(jù)流,經(jīng)過(guò)工作時(shí)鐘為f1=f/log2 M的串并轉(zhuǎn)換單元,得到速率為f1的并行數(shù)據(jù)流,經(jīng)過(guò)查找表LUT、數(shù)據(jù)選擇器MUX和延時(shí)單元Delay之后的數(shù)據(jù)選擇器以f1的時(shí)鐘頻率工作,輸出數(shù)據(jù)分別進(jìn)入兩個(gè)濾波器組,以2 f1時(shí)鐘工作的數(shù)據(jù)選擇器交替把濾波器組的輸出送給后級(jí)加法器單元,完成整個(gè)調(diào)制過(guò)程。

3 驗(yàn)證與實(shí)現(xiàn)

根據(jù)以上設(shè)計(jì),用Altera公司的StratixII系列器件EP2S30F484C3實(shí)現(xiàn)4、16、64、256QAM調(diào)制器。將本文的MQAM調(diào)制器設(shè)計(jì)方法和傳統(tǒng)方法在硬件資源消耗和最高工作頻率等方面進(jìn)行比較,結(jié)果如表2所示。

由表2可以看出,本文結(jié)構(gòu)較之傳統(tǒng)結(jié)構(gòu)在硬件資源消耗和最大工作頻率方面有較大的改善。

本文討論了MQAM調(diào)制器在FPGA上的一種簡(jiǎn)化高效的實(shí)現(xiàn)方法。其中,主要是系數(shù)對(duì)稱的CSD編碼濾波器和簡(jiǎn)化混頻器的設(shè)計(jì),使得系統(tǒng)中不需要乘法器,而且實(shí)現(xiàn)模塊復(fù)用。仿真實(shí)驗(yàn)表明,該方法可以提高系統(tǒng)的工作頻率,而且消耗資源少,是較理想的MQAM調(diào)制器設(shè)計(jì)方法。

參考文獻(xiàn)

1 臧道華. 無(wú)線信道中信號(hào)傳輸?shù)淖赃m應(yīng)調(diào)制技術(shù). 南京理工大學(xué)學(xué)報(bào),2001;(12):22~35

2 Yongbin Wu, Shayan, Y.R. ′Implementation of high-peed multi-level QAM modems based on Xilinx Virtex-II FPGA′.Electrical and Computer Engineering, 2003. IEEE CCECE 2003. Canadian Conference on, 2003;1(4~5):195~198

3 Zhangwen Tang, Jie Zhang, Hao Min. A high-speed, pro-grammable, CSD coefficient FIR filter. Consumer Electronics,IEEE Transactions on,2002;48(4):834~837

4 Soderstrand, M.A.′CSD multipliers for FPGA DSP applica-tions′ Circuits and Systems, 2003. ISCAS ′03. Proceedings of the 2003 International Symposium on,2003;5(25~28) V-469~V-472

5 Kei-Yong Khoo, Kwentus, A. Willson, A.N., Jr. A progr-ammable FIR digital filter using CSD coefficients′.Solid-State Circuits, IEEE Journal of,1996;31:(6)869~874

6 孟利民,楊楊,仇佩亮.基于DSP技術(shù)的自適應(yīng)調(diào)制器的設(shè)計(jì).浙江工業(yè)大學(xué)學(xué)報(bào),2001;29(4):323~327