摘要:通過分析920T核ARM 處理器的高速片上系統(tǒng)總線AHB時(shí)序及其靜態(tài)存儲控制器SMC接口模型,研究IBM PC/AT和IEEE PC/104總線規(guī)范,提出一種在ARM 平臺上實(shí)現(xiàn)兼容PC/104總線的方案.深入探討兩種平臺體系在存儲器結(jié)構(gòu)、指令系統(tǒng)及總線時(shí)序等方面的巨大差異,給出了克服這些差異并實(shí)現(xiàn)總線功能兼容的方法.該兼容總線解決了在ARM 平臺上無法使用標(biāo)準(zhǔn)PC/104模板的難題,采用該方案有利于在嵌入式系統(tǒng)的設(shè)計(jì)中兼取ARM 處理器和PC/AT體系的優(yōu)勢.

引 言

PC/104 是一種專門為嵌入式應(yīng)用而定義的工業(yè)控制總線規(guī)范.以IBM PC/AT總線規(guī)范為基礎(chǔ)的個(gè)人計(jì)算機(jī)及其外圍設(shè)備在應(yīng)用上取得了巨大的成就,IEEE一996稱之為ISA(工業(yè)標(biāo)準(zhǔn)架構(gòu):Industry Standard Architecture)總線.PC/104是ISA標(biāo)準(zhǔn)的延伸,定義在IEEE-P996.1中,稱為兼容PC嵌入式模塊標(biāo)準(zhǔn).PC/104實(shí)質(zhì)上是一種緊湊型的ISA,其信號定義和Pc/AT基本一致,但電氣和機(jī)械規(guī)范卻完全不同,是一種優(yōu)化、小型、堆疊式結(jié)構(gòu)的嵌入式總線系統(tǒng).PC/104總線來自于實(shí)踐發(fā)展的需要,同時(shí)得益于PC技術(shù)的迅速發(fā)展,由于其開發(fā)環(huán)境友好、兼容芯片豐富、標(biāo)準(zhǔn)支持廣泛等優(yōu)勢,受到了眾多從事嵌入式產(chǎn)品生產(chǎn)商和系統(tǒng)集成商的歡迎,盡管現(xiàn)在ISA設(shè)備已不常見,但PC/104在嵌入式系統(tǒng)領(lǐng)域卻仍是通行的標(biāo)準(zhǔn).

ARM是當(dāng)前嵌入式系統(tǒng)應(yīng)用中的熱門技術(shù).由于ARM處理器的卓越性能、較低的價(jià)格以及業(yè)內(nèi)半導(dǎo)體廠商的廣泛支持,在嵌入式環(huán)境中有廣泛的應(yīng)用.ARM 公司創(chuàng)造了CHIPLESS模式,該公司通過將高效的ARM 內(nèi)核授權(quán)給半導(dǎo)體公司,由半導(dǎo)體公司根據(jù)實(shí)際的應(yīng)用情況加上各種外圍的功能電路來構(gòu)成一塊完整的芯片,這種模式使半導(dǎo)體廠商得以有能力生產(chǎn)功能強(qiáng)大的各種專用處理器芯片.AR M在設(shè)計(jì)上基于SoC思想,優(yōu)先考慮對每一個(gè)具體應(yīng)用使用最大可能集成周邊設(shè)備的單一芯片,但在板極擴(kuò)展方面仍然缺乏能被廣泛接受的新工業(yè)標(biāo)準(zhǔn).

1 PC/AT模型和PC/104總線

1.1 總線信號

PC/104_4 ]是一種16位總線,但可向前兼容8位XT模式,典型總線時(shí)鐘為8 MHz,4個(gè)時(shí)鐘脈沖可完成一次完整的總線訪問,必要時(shí)可插入一個(gè)額外的等待周期以適應(yīng)低速外設(shè).在嵌入式系統(tǒng)開發(fā)中常用以下信號.

1.1.1 地址和數(shù)據(jù)信號線

BALE總線地址鎖存使能信號線,由平臺CPU驅(qū)動(dòng).當(dāng)ISA擴(kuò)展卡或DMA控制器占用總線時(shí),它也被置為邏輯1.

SA~19:O>:低2O根地址信號線,由當(dāng)前總線的擁用者驅(qū)動(dòng).

LAd 23:17> :鎖存地址信號線,用來訪問16MB的存儲器地址空間.由當(dāng)前總線擁有者或DMA控制器驅(qū)動(dòng).

SD<15:0> :數(shù)據(jù)信號線.

1.1.2 總線周期控制信號線

MEMR#:存儲器讀信號線.

MEMW #:存儲器寫信號線.

IOR#:I/O I/O讀信號線.

IOW #:I/O I/O寫信號線.

1.1.3 中斷和DMA(Direct Memory Access)信號線

IRQx:中斷請求信號線.

DRQx:DMA請求信號線.

DACKx#:DMA應(yīng)答信號線.

1.2 地址空間

PC/AT系統(tǒng)使用不同的指令訪問存儲器空間和IO端I:1空間,訪問存儲器空間時(shí)PC/104總線驅(qū)動(dòng)MEMR#和MEMW#信號,訪問存儲器空間時(shí)PC/104總線驅(qū)動(dòng)IOR#和IOW #信號.兩個(gè)空間使用同一套地址線,但是由于端口空間只有64K有效,所以進(jìn)行IO 端口訪問時(shí)地址線上只有SA<15:O>是有效的.

PC/AT系統(tǒng)有專門的端口訪問指令用于實(shí)現(xiàn)端口訪問,Linux用戶程序只需以root權(quán)限調(diào)用ioperm()指定需操作的端口地址范圍,之后即可自由訪問這些端口.由于用于訪問端口的一組宏實(shí)際上直接對應(yīng)CPU的端口訪問指令,所以存取效率很高.

1.3 PC/104總線周期

PC/104總線周期分為CPU驅(qū)動(dòng)和DMA控制器驅(qū)動(dòng)兩大類,在嵌入式應(yīng)用中較常用的是CPU驅(qū)動(dòng)的IO讀/IO寫周期.

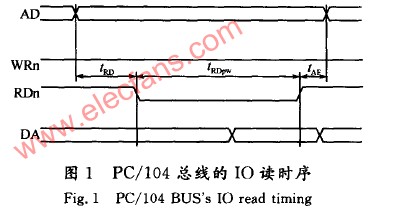

圖1中采用8 MHz時(shí)鐘的標(biāo)準(zhǔn)PC/104總線£Rd大于300 ns,tAF應(yīng)大于250 ns,tRDpw約為500 ns。

2 EP9315(ARM920T)體系

2.1 存儲器結(jié)構(gòu)和地址空間

EP9315是Cirrus Logic公司生產(chǎn)的典型ARM 920 TDM I(Thumb,Debug,M ultiply,Em—bedded ICE macrocel1)32位哈佛結(jié)構(gòu)處理器.EP9315有一個(gè)通用存儲器訪問接口,支持SDRAM,SRAM,ROM,及FLASH(包括N0R FLASH)等不同形式的存儲器,各種存儲器訪問均共享數(shù)據(jù)總線DA[3l:O]和地址總線AD[Z5:o],使用統(tǒng)一的訪問控制邏輯 。

與X86模型不同,ARM 平臺只實(shí)現(xiàn)一個(gè)物理地址空間,在Bo0T成功后只擁有一個(gè)唯一的虛地址空間,CPU不設(shè)立專門的外設(shè)I/O指令,訪問外設(shè)I/O端口和內(nèi)存單元使用相同的指令.

引腳CSn[7:6]和CSn[3:O]用于存儲器芯片的選通,除發(fā)生時(shí)間略有差異之外(圖2),基本上可視為地址總線的高位線.

2.2 AHB總線時(shí)序和SRAM 接口

AHB(Advanced High-Speed Bus)是EP93 1 5內(nèi)部920T核與存儲器、DMA,存儲器等設(shè)備實(shí)現(xiàn)高速互聯(lián)的系統(tǒng)總線.EP9315的AHB具有完善的多主控沖突仲裁能力,其典型工作頻率可達(dá)100 MH。

靜態(tài)存儲控制器SMC(Static Memory Controller)與920T核心通過AHB互聯(lián),支持存儲器的8/16/32位訪問方式.SMC最多可提供8個(gè)組,每個(gè)組均可支持SRAM,ROM,F(xiàn)LASH EPROM 等存儲器的訪問,各組可以對數(shù)據(jù)總線寬度和速度等參數(shù)獨(dú)立配置.圖2描述了SRAM 讀操作時(shí)序.

圖中f刪為CSn到RDn的延遲,最大值為3 ns;tDAs是RDn無效前的數(shù)據(jù)總線建立時(shí)間,最小值為12+tHcI tRDD 是RDn有效時(shí)間,典型值為t HcI K×(W ST1+ 2)。

HCLK是AHB總線的工作頻率,該頻率的高低直接影響系統(tǒng)全局性能,因此通常配置為上限100 MHz,此時(shí)相應(yīng)周期£脅 為10 ns.WSTI用于控制sMc對SRAM/R0M 的訪問速度,寄存器SMCBCR0—3, SMCBCR6-7 (地址0x80080000—0x8008001C)的第5-9位分別為相應(yīng)各組的WST1.WST1的默認(rèn)值為0xlF,即默認(rèn)情況下SMC使用

最低的訪問速度,顯然fRDD 為330 ns,小于PC/104總線中的500 ns(圖1).

3 PC/104總線實(shí)現(xiàn)

3.1 總線驅(qū)動(dòng)

在EP9315支持的各類總線接口邏輯中,SMC提供的SRAM/ROM 時(shí)序與PC/104總線最為接近.將外部設(shè)備所需的PC端口空間和存儲器空間均映射至統(tǒng)一的虛擬空間中即可實(shí)現(xiàn)訪問.

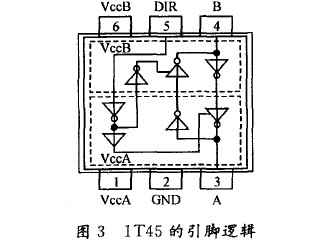

注意到PC/104總線使用標(biāo)準(zhǔn)TTL邏輯電平,而EP9315的處理器是3.3 V器件,在極端負(fù)載情況下無法保證系統(tǒng)穩(wěn)定工作.TI的雙電源總線收發(fā)器1T45,2T45,16T245等可用于實(shí)現(xiàn)電平轉(zhuǎn)換,圖3是1T45的引腳邏輯圖.

地址總線及訪問控制信號均由CPU驅(qū)動(dòng),外部設(shè)備始終處于被動(dòng)接收狀態(tài),正確設(shè)定數(shù)據(jù)流向即可.

數(shù)據(jù)總線信號是時(shí)分雙向傳輸?shù)模瑸楸槊獬霈F(xiàn)總線沖突,必須保證除非CPU 透過該收發(fā)器對外設(shè)進(jìn)行讀訪問,否則收發(fā)器的CPU 側(cè)應(yīng)始終處于高阻狀態(tài).為此,16T245等具有輸出使能端的器件只需使輸出無效即可,而對于無使能端的收發(fā)器則應(yīng)使CPU側(cè)處于輸入狀態(tài)(高阻).

確認(rèn)CPU 已向兼容PC/104總線發(fā)起讀操作的有效方法是檢查RDn的下降沿是否發(fā)生.一旦RDn下降,應(yīng)立即將收發(fā)器置成從外設(shè)流向CPU方向,且輸出使能有效,并至少保持至RDn上升沿之后,以保證可靠讀取.

3.2 端口映射

SMC的存儲器分組片選信號CSn可作為高位地址線參加這址譯碼.任取CSi和CSj組用于兼容總線,即可分別實(shí)現(xiàn)O-0x3FFFFFF的獨(dú)立存儲器地址和IO端口地址.可用地址數(shù)量已經(jīng)遠(yuǎn)超出XT系統(tǒng)中的1 M(存儲器)和1 K(IO端口).

在Linux系統(tǒng)中,io.h文件中聲明了函數(shù)iore—map(),用于將兼容總線上外部資源的物理地址映射到核心虛地址空間中.iounmap()函數(shù)用于取消ioremap()所做的映射.上述操作都應(yīng)在設(shè)備驅(qū)動(dòng)程序中執(zhí)行.在外部資源成功映射到核心虛地址后,使用指向核心虛地址的指針就可訪問相應(yīng)設(shè)備資源,但顯然這種訪問方式與在X86平臺下差異較大.

將兼容總線視為一個(gè)獨(dú)立的字符設(shè)備,為其編寫驅(qū)動(dòng)程序,實(shí)現(xiàn)對指定偏移地址的讀寫函數(shù),此處的偏移地址即對應(yīng)PC/104總線中的物理地址 .

對inb(),outb()等X86平臺下的常見的底層端口操作函數(shù),可用宏替換的方式轉(zhuǎn)由驅(qū)動(dòng)中的相應(yīng)讀寫函數(shù)實(shí)現(xiàn).

3.3 總線時(shí)序控制

綜合前文所述,盡管SMC的SRAM 訪問時(shí)序非常接近PC/lO4總線,但是要實(shí)現(xiàn)高兼容性的PC/lO4,仍有兩方面問題需要解決,一是SMC驅(qū)動(dòng)的SRAM 讀寫速度遠(yuǎn)高于PC/104總線,二是為解決電平兼容問題引入的總線收發(fā)器,其數(shù)據(jù)流向和輸出使能需要適當(dāng)?shù)目刂疲?/p>

以下VHDL代碼根據(jù)SMC輸出的RDn和WRn設(shè)置EIOR和EIOW 時(shí)序,并適時(shí)輸出信號EXIDR,EXOE控制收發(fā)器數(shù)據(jù)流向和輸出使能.

ECLK是頻率為27 MHz是時(shí)鐘脈沖.

If ECLK’EVENT and ECLK一‘1’then

if(? )then __地址無效

EXoE< 一:1’;

EXDlR< 一‘1’;

EIOR< 一‘1’;

rdreg< 一0;

else

if rdreg< 1 l then

rdreg< 一rdreg+ 1;

EXOE< 一‘0’;

else

rdreg< 一0;

EXDIR< 一‘1’;

EXoE< 一‘1’;

end if;

if rdreg< 2 or rdreg> 6 then

EIOR< 一‘1’;

EIOW < 一‘1’;

elsif rdreg一2 or rdreg= 3 then

if RDn一‘1’then

EIOR< 一‘1’;

EXDIR< 一‘1’;

elsif W Rn一‘1’then

EIOW < 一‘0’;

EXDIR< 一‘1’;

end if;

end if;

上述代碼適當(dāng)延遲了關(guān)閉雙電源收發(fā)器的輸出使能和數(shù)據(jù)流向重設(shè)時(shí)間,保證數(shù)據(jù)總線穩(wěn)定,使CPU 和外設(shè)有足夠的時(shí)間進(jìn)行輸入輸出操作.

圖4中曲線2是兼容PC/104地址空間內(nèi)任意地址信號經(jīng)收發(fā)器緩沖后的譯碼結(jié)果,曲線1和曲線3是對該地址進(jìn)行讀操作時(shí)的RDn和IOR信號.

圖4中RDn由EP9315直接驅(qū)動(dòng),原始邏輯電平為3.3 V,實(shí)驗(yàn)電路對該信號電平進(jìn)行了無時(shí)延的處理.

目前主流元器件在速度上都已能兼容PCI總線,因此盡管SMC驅(qū)動(dòng)的SRAM 讀寫速度高于標(biāo)準(zhǔn)PC/104總線,但只要保證各控制信號問關(guān)系清晰(圖4b),是不會造成總線訪問失敗的.

4 結(jié)束語

利用ARM 系統(tǒng)成本較低,功耗更小,啟動(dòng)速度快,指令效率高的的特點(diǎn),兼取PC/AT系統(tǒng)和PC/104總線設(shè)備在產(chǎn)業(yè)化基礎(chǔ)方面的優(yōu)勢,在ARM平臺上構(gòu)建PC/104總線,有助于利用現(xiàn)有資源,保護(hù)已有投資.由于ARM 與PC/AT模型在處理器架構(gòu)上有本質(zhì)性的差異,在ARM 平臺上構(gòu)建的PC/104總線在所有的具體應(yīng)用中要做到與標(biāo)準(zhǔn)PC/104規(guī)范完全兼容幾乎是不可能,但是在特定的應(yīng)用需求及確定的操作系統(tǒng)下這種努力是完全可行并且有效的。對于特定的應(yīng)用而言,通常只需顧及PC/104總線時(shí)序的一個(gè)子集,這就大大降低了系統(tǒng)現(xiàn)實(shí)的難度。兼容PC/104總線在使用遵守ISAPnP(Plug and Play)規(guī)范的設(shè)備時(shí)有較多的困難。另外在使用包含中斷請求和DMA需求的設(shè)備時(shí)也需要專門的考慮。