功能強大的可編程邏輯平臺使得Prisma Engineering公司能夠針對所有蜂窩網(wǎng)絡提供可重配置無線測試設備。長期演進(LTE)是移動寬帶的最3GPP標準,它打破了現(xiàn)有蜂窩網(wǎng)絡的固有模式。LTE與前代UMTS和GSM標準相比,除采用高頻譜效率的射頻技術外,其架構還得到了大幅簡化。LTE系統(tǒng)的無線接入部分Node-B,是連接無線電和整個互聯(lián)網(wǎng)協(xié)議核心網(wǎng)絡之間的邊緣設備。這種架構無法監(jiān)測和測試等效于UMTS中間鏈路上的元件。必須通過無線電接口,才能有效地測試LTE網(wǎng)絡元件。

這正是Prisma Engineering公司線路服務器單元(LSU)UeSIM LTE項目的設計組要解決的問題。該仿真器是針對所有LTE測試需求的全面解決方案,可幫助網(wǎng)絡設備設計人員對空中接口和核心網(wǎng)絡進行測試和監(jiān)控。單個這種硬件平臺即可在每個扇區(qū)模擬出多達1 024個用戶設備。無線電接口的載荷-應力測試和功能測試覆蓋了完整LTE協(xié)議棧及其應用。射頻前端采用本地多輸入多輸出(MIMO)設計,可支持5MHz、10MHz、15MHz和20MHz多種不同帶寬。

這個仿真器中心采用三個賽靈思Virtex®-5 FPGA(XC5VSX50T),可支持高級軟件無線電重配置。總部設位于意大利米蘭的Prisma Engineering公司的設計組很快認識到,我們需要功能強大、可重編程的架構,以便能夠用同一開發(fā)板靈活應對多種無線接入標準。現(xiàn)有兩種用戶測試工具:LTE Test Manager(主要針對LTE設備廠商提供)和Quick GUI(主要針對LTE網(wǎng)絡營運商提供)。Quick GUI提供通過/未通過測試方案,而Test Manager則可進行更為復雜的分析。

LSU UeSIM LTE架構

LSU UeSIM LTE仿真器采用由協(xié)議處理單元(PPU)模板、軟件無線電(SDR)模板和支持MIMO操作的兩個無線電模塊共同構成的CompactPCI標準架構。

采用Intel技術的PPU模板是一種主處理器卡,能夠對多個SDR模板進行管理,改善載荷-應力性能。軟件無線電模板專為擴展我們先前的LSU系統(tǒng)在無線電接口的運行性能而設計。CompactPCI無線電夾層卡負責提供各個不同標準射頻帶寬的射頻發(fā)送/接收功能:GSM(850 MHz和900MHz;1.8和1.9GHz)、LTE(700MHz,2.1 GHz、2.3 GHz、2.5 GHz和2.6GHz)和WiMAX(2.4GHz、3.5GHz和5GHz)。

SDR卡架構

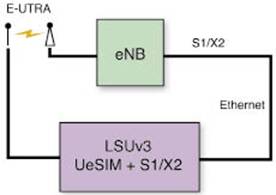

SDR卡是一種集成在LSU軟/硬件環(huán)境中的高性能平臺,用于提高系統(tǒng)與基帶(CPRI/OBSAI)、無線電接口或者兩者之間的連接功能。該卡使用工作在特定頻帶內的不同外部無線電模塊,可支持各種無線標準,比如GSM/EDGE、UMTS、HSPA、WiMAX和LTE等。圖1為在LTE測試場景中,仿真器或取代無線電扇區(qū),或為核心網(wǎng)絡提供測試接口。

圖1 LTE測試場景

我們采用三個德州儀器的1GHz DSP(我們選用了TMS320C6455)和Analog Devices公司的模數(shù)轉換器(AD9640)與數(shù)模轉換器(AD9779),完成了基于賽靈思FPGA的SDR卡設計。時鐘網(wǎng)絡采用Analog Devices公司的AD9549,能夠為轉換和數(shù)字信號處理器件(FPGA、DSP)提供極高的靈活時基。

LTE加工數(shù)據(jù)通路

Prisma把LTE加工數(shù)據(jù)通路分為兩大部分,一是在FPGA內實現(xiàn)的射頻前端。二是在DSP內實現(xiàn)的物理資源分配以及數(shù)據(jù)通道與控制通道端接。

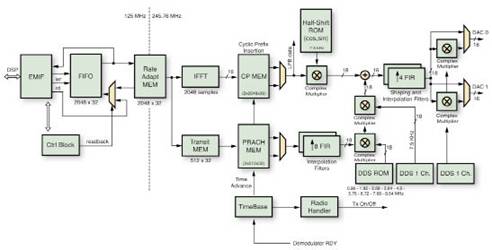

在上行鏈路方向,由一個DSP負責處理MAC層到物理層的交換以及物理層某些功能的操作。它負責為編碼、交織、加擾、符號映射和子載波分配提供參考信號(導頻)、源數(shù)據(jù)和控制通道。離散傅立葉轉換(DFT)函數(shù)負責根據(jù)SC-FDMA標準完成來自不同終端的數(shù)據(jù)轉換。該系統(tǒng)通過EMIF接口把每個OFDM符號都發(fā)送到上行鏈路FPGA。圖2為LSU軟件無線電卡上的賽靈思Virtex-5 FPGA和TI DSP。

圖2 LSU軟件無線電卡

該FPGA將數(shù)據(jù)速率從125MHz(DSP EMIF接口時鐘)提升到245.76MHz(FPGA加工速率)。然后FPGA將執(zhí)行一系列其他操作:2048點反向快速傅立葉轉換、循環(huán)前綴插入、PRACH數(shù)據(jù)通道插入、7.5kHz頻率下轉換OFDM符號頻譜的半移位函數(shù)、信道整形與內插濾波以及24MHz頻率下的中頻(IF)轉換。隨后該器件以122.88MHz的時鐘頻率把中頻數(shù)據(jù)發(fā)送到DAC。同時射頻卡將模擬信號轉換為射頻信號,發(fā)送至發(fā)射器放大器。下行鏈路方向上,在LNA放大、可編程增益和轉換階段完成后,射頻卡將把接收到的中頻數(shù)據(jù)發(fā)送到SDR卡(140MHz)。ADC將以122.88MHz的頻率對模擬數(shù)據(jù)進行二次采樣,而FPGA則負責處理最終到基帶的17.12MHz頻率轉換。該數(shù)據(jù)可以與兩個單輸入、單輸出通道關聯(lián),也可以與一個MIMO通道關聯(lián)。

中頻數(shù)據(jù)隨后進入下行鏈路FPGA,由該FPGA將其轉換為基帶并進行過濾。即便芯片速率保持在245.76MHz,多相抽取濾波器仍能以30.72MHz的符號率進行奈奎斯特FIR濾波、頻譜鏡像抑制和數(shù)據(jù)率降低等操作。

FPGA輸入數(shù)據(jù)流看上去像數(shù)據(jù)流,而非一系列的OFDM符號。同步函數(shù)對數(shù)據(jù)流進行適當?shù)那蟹郑瑥亩枥L出OFDM符號。(要實現(xiàn)這一點,同步線路必須使用多個相關器在深度抽取的輸入數(shù)據(jù)中檢測出Zadoff-Chu主同步信號,隨即才能獲取OFDM符號。)最后,在刪除循環(huán)前綴后,以FFT轉換獲得的最終數(shù)據(jù)則通過EMIF接口傳遞到另一個DSP。下行鏈路包含兩個以串行RapidIO接口連接在一起的DSP。這兩個DSP的作用是進行頻率校正、信道估計、均衡和MIMO解碼。然后由這兩個DSP在MAC層互連之前,進行數(shù)據(jù)通道和控制通道抽取、Viterbi和Turbo解碼、去交織和解擾。

在上行鏈路側,由第三個FPGA負責上行鏈路和下行鏈路FPGA之間的回送測試,確保SDR模板符合CPRI/OBSAI標準。

我們的設計小組廣泛使用賽靈思Core GeneratorTM IP核來生成濾波器、DDS、FFT、Block RMA、FIFO 和MACC功能,把DSP48E和DCM用于設計中的時鐘去歪斜部分。這種大規(guī)模例化方法在縮短開發(fā)時間的同時,還能夠提供緊湊設計方案。圖3為“上行鏈路FPGA”實現(xiàn)反向FFT、循環(huán)前綴插入、濾波、IF上變頻轉換以及其他時分雙工和PRACH處理所需的操作。該系統(tǒng)將同一信號發(fā)送至兩個DAC以備冗余。

因為這個項目的市場投放時間要求非常緊迫,我們對其功能劃分進行了精心分析。FPGA應該容納甚至更多的LTE功能,不過我們的設計目標在于尋求系統(tǒng)中FPGA與DSP部分間的平衡。

FPGA設計策略

該項目的市場投放時間要求非常緊迫,因此我們對FPGA和DSP之間的功能劃分進行了精心的分析。值得注意的是,F(xiàn)PGA應能夠支持更多的LTE功能,不過我們的設計目標之一是尋求系統(tǒng)中FPGA與DSP部分間的平衡。

圖3 “上行鏈路FPGA”

FPGA時鐘頻率是設計中較為困難的一環(huán)。在像調制系統(tǒng)這樣的大型設計中采用245.76MHz的時鐘速率是項艱巨的任務。我們設計小組需要考慮許多問題,比如功耗、設計約束、布局布線等。盡管如此,由于ISE®設計套件可提供各個設計迭代的穩(wěn)定高質量結果,過采樣因子(FPGA時鐘頻率與OFDM符號頻率之比)為8,能夠讓諸如濾波器和FFT轉換這樣的設計項目在盡量少的條件下滿足所需的LTE功能。ISE軟件也幫助我們實現(xiàn)了合適的同步電路面積。我們設計的關鍵在于在上行鏈路中采用射頻卡架構(而非存在I/Q不平衡缺點的直接轉換法)來接收來自中頻的FPGA數(shù)據(jù)。通過使用賽靈思直接數(shù)字頻率合成器(direct digital synthesizer),18位正弦/余弦波可用作復雜調制工作的理想載波,并可用在傳輸無線電信號上測得的誤差矢量幅度予以確認。由于采用了賽靈思Virtex-5 FPGA和TI的DSP技術,LSU UeSIM LTE仿真器已經(jīng)成為蜂窩網(wǎng)絡最先進的載荷-應力解決方案測試設備,能為SDR系統(tǒng)提供強大、靈活和可擴展的解決方案。

圖4為前端“下行鏈路FPGA”進行IF下變頻轉換、多相抽取濾波、同步、循環(huán)前綴刪除和直接FFT等操作。該系統(tǒng)使用了兩個鏈路來支持TDD和FDD模式的MIMO操作。

圖4 前端“下行鏈路FPGA”