摘要:以Altera公司的FPGA芯片EP2C20Q208C8為例,詳細介紹了在QuartusII 7.2的環(huán)境下,用SOPC Builder構(gòu)建Nios軟核時,自定義FIFO接口元件的方法。通過將采集到的電壓信號,在數(shù)碼管上顯示的實驗,實現(xiàn)FIFO寄存器與Nios CPU之間的通信。

關(guān)鍵詞:現(xiàn)場可編程門陣列FPGA;Nios;先進先出;可編程片上系統(tǒng)Builder

0 引言

隨著微電子技術(shù)和半導體工業(yè)的不斷發(fā)展,數(shù)字技術(shù)已進入片上系統(tǒng)時代。從而又發(fā)展了SOPC(可編程片上系統(tǒng)),SOPC是Altera 公司提供的片上可編程系統(tǒng)解決方案。Nios嵌入式處理器是Altera公司推出的軟核CPU,提供給用戶,并在Altera的FPGA上實現(xiàn)優(yōu)化,用于 SOPC集成

并在FPGA上實現(xiàn),提高了系統(tǒng)的靈活性和擴大范圍。

自定義外設(shè)是SOPC系統(tǒng)靈活性的重要體現(xiàn),是SOPC系統(tǒng)中極其重要的一種設(shè)計方法。在大量的數(shù)據(jù)常需要處理時,利用自定義外設(shè)由具體的硬件來實現(xiàn),可以極大程度地提高系統(tǒng)運行的速度,同時便于系統(tǒng)的模塊化與集成化,是SOPC系統(tǒng)設(shè)計的重中之重。定制的用戶外設(shè)能夠以“硬件加速器”的形式實現(xiàn)各種各樣用戶要求的功能。

1 定制Avalon總線型FIFO接口元件

由于選用的AD采樣速率非常高,并且只由時鐘控制端控制,因此設(shè)計時在AD采集模塊和Nios CPU之間加一個FIFO存儲器,從系統(tǒng)外部接口送來的數(shù)據(jù)先在FIFO中緩存,然后將數(shù)據(jù)讀入SDRAM,在片上進行數(shù)據(jù)處理。整個流程在FPGA平臺上采用SOPC方法實現(xiàn)。在SOPC Builder中只有廠商提供的片上FIFO接口控制器,沒有外部使用的FIFO接口控制器核,因此需要用戶自定義FIFO接口控制器,這樣才能滿足系統(tǒng)外圍電路的應用要求。文中采用創(chuàng)建元件配置向?qū)Фㄖ艶IFO接口元件的方法。

2 用戶自定義IP核的開發(fā)流程

自定義外設(shè)作為NiosII軟核處理器超強靈活性的體現(xiàn),它的開發(fā)要遵循一定的規(guī)律。一個用戶自定義外設(shè)必須用硬件描述語言來描述硬件的邏輯。用戶自定義IP按照對Avalon總線操作的不同可分為Avalon Master、Avalon Slaver和Avalon Streaming外設(shè)。由于Avalon Master和Avalon Streaming外設(shè)的開發(fā)比Avalon Slave外設(shè)要復雜,所以用戶開發(fā)的外設(shè)大部分為Avalon Slave外設(shè),但是開發(fā)流程是一樣的。典型的Avalon外設(shè)的開發(fā)步驟如下:

(1)規(guī)劃元件的硬件功能。若采用微控制器控制該元件,則規(guī)劃訪問該硬件的應用程序接口(API);

(2)在硬件和軟件要求的基礎(chǔ)上,定義一個恰當?shù)慕涌?一般為Avalon Slave端口);

(3)使用硬件描述語言描述硬件邏輯。一個典型元件的硬件架構(gòu)一般由接口模塊、寄存器文件模塊和行為模塊3部分組成。接口模塊作為頂層模塊,定義總線接口信號;寄存器文件模塊完成該元件與外部信號的通信,提供訪問與控制元件的邏輯界面;行為模塊實現(xiàn)元件的硬件功能。片上總線Avalon從端口的信號都不是必須的,一個典型的Avalon從端口所包含的信號如表1所示。

(4)單獨驗證元件的硬件功能;

(5)寫用于描述寄存器的C頭文件為軟件定義硬件寄存器映像;

(6)寫元件的驅(qū)動軟件;

(7)把通過測試的源代碼使用元件編輯器封裝硬件HDL和軟件文件,完成元件定制。

3 自定義FIFO接口的開發(fā)

3.1 硬件構(gòu)建

3.1.1 接口模塊的設(shè)計

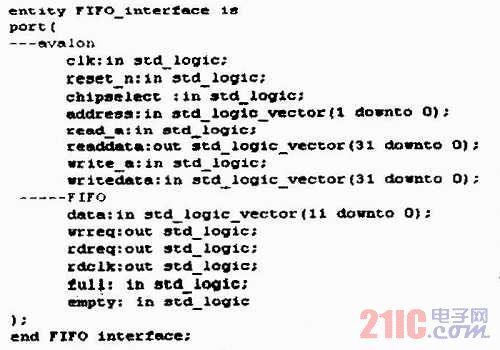

根據(jù)FIFO的功能需要,該模塊所需的Avalon總線輸入信號為clk、reset n、data、full、empty信號,而模塊輸出則為rdclk、rdreq、wrreq信號。該接口模塊定義了總線接口信號,作為頂層模塊。

Avalon總線接口設(shè)計文件的端口說明部分如下:

3.1.2 寄存器文件模塊

寄存器文件模塊實現(xiàn)與外部信號的通信,提供了訪問與控制元件界面。在寄存器文件中,Avalon總線的地址信號有兩位,00表示讀取數(shù)據(jù)寄存器,O1表示讀取狀態(tài)寄存器,10表示寫控制寄存器,address的11保留。在片選和讀信號的控制下,分別讀數(shù)據(jù)寄存器和狀態(tài)寄存器。在片選和寫信號的控制下,向控制寄存器寫入數(shù)據(jù)。

3.1.3 行為模塊

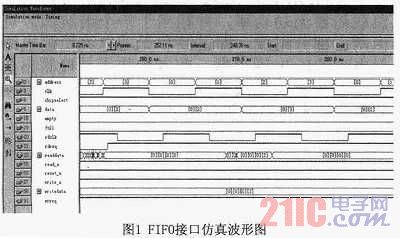

行為模塊實現(xiàn)元件的硬件功能,當寫請求(wrreq)信號有效時,向數(shù)據(jù)寄存器中寫入數(shù)據(jù),當讀請求(rdreq)信號有效時,讀取數(shù)據(jù)寄存器中的數(shù)據(jù)。在QuartusⅡ7.2環(huán)境下,基于EP2C20Q240C8器件的FIFO接口的仿真波形如圖1所示。

3.2 FIFO接口模塊的添加

在Quartus II工程中打開SOPC Builder,在SOPC Builder界面的左欄中點擊Create new component打開創(chuàng)建元件向?qū)В瑥棾鯟omponent Editor,在HDL Files選項卡中添加HDL文件(FIFO interface.vhd),并將其設(shè)置為頂層模塊。在Signals選項卡中出現(xiàn)FIFO interface中定義的信號。若出現(xiàn)紅色字體表示錯誤,需要將其接口類型修改一下,如reset n被指定為clock類型,傳輸方向為input,數(shù)據(jù)寬度為1,read-data被指定為avalon_slave類型,傳輸方向為output,數(shù)據(jù)寬度為32,data被指定為export類型,傳輸方向為export,數(shù)據(jù)寬度為32,等等。修改完之后,F(xiàn)IFO的地址對齊方式選擇動態(tài)地址對齊"Mermory(use dynamic bussizing)"。時序設(shè)置也很重要,設(shè)置不當會造成數(shù)據(jù)的錯誤傳輸。系統(tǒng)FIFO的讀寫時鐘為50MHz,周期為20ns,設(shè)定建立時間為 1ns,將所有設(shè)置設(shè)置完之后進行保存。保存完之后在該工程目錄下會出現(xiàn)FIFO_interface_hw.tcl文件,F(xiàn)IFO控制器接口就出現(xiàn)在左欄中,若想在其它工程中使用該控制器,最簡單的方法是將FIFO_inter-face.vhd、FIFO interface hw.tcl在FIFO interface hw.tcl~放在一個文件夾里,并將此文件夾放在QuartusⅡ的安裝目錄的ip文件夾中。

3.3 Nios CPU模塊

搭建好SOPC框架之后,生成CPU原理圖模塊如圖2所示。其中第二部分就是FIFO接口文件生成的模塊圖,包括輸入信號(data、 empty、full)和輸出信號(rdclk、rdreq、wrreq)。兩個PIO接口con和seg,分別用作數(shù)碼管的位選通和段選通。

4 軟件設(shè)計

軟件設(shè)計包括寄存器頭文件、驅(qū)動軟件及測試程序的設(shè)計。寄存器頭文件FIFO reg.h定義了對FIFO進行讀寫操作的宏。IORD和IOWR是硬件抽象層提供的兩個訪問寄存器的C語言宏。下面代碼是對FIFO的數(shù)據(jù)寄存器、狀態(tài)寄存器和控制寄存器進行讀寫操作的宏。

驅(qū)動軟件包括FIFO.h和FIFO.c文件。FIFO.h定義了驅(qū)動函數(shù)的原型和常量,F(xiàn)IFO.c則實現(xiàn)驅(qū)動函數(shù)的功能。FIFO.c中定義了一個函數(shù),實現(xiàn)將采集到的數(shù)據(jù)在數(shù)碼管上顯示的功能。例如采集到電壓值為5V電壓時,數(shù)碼管上顯示5.00。

5 結(jié)束語

本文通過介紹基于SOPC的自定義FIFO接口的詳細過程,用戶可以在SOPC設(shè)計環(huán)境下自定義任意接口控制器。定制元件是SOPC Builder靈活性的重要體現(xiàn),大大擴展了NiosⅡ系統(tǒng)的應用范圍。本設(shè)計采用VHDL語言編寫SOPC用戶自定義邏輯模塊,實現(xiàn)FIFO接口控制器的設(shè)計,此模塊已經(jīng)成功地在FFGA上實現(xiàn)數(shù)據(jù)采集模塊與Nios CPU之間的通信。通過創(chuàng)建元件配置向?qū)Фㄖ艶IFO接口元件的方法,對定制元件的設(shè)計具有較好的借鑒作用。