擴(kuò)頻通信因其很好的保密性、隱蔽性,、抗干擾性以及抗多徑效應(yīng)等優(yōu)勢得到了快速發(fā)展和廣泛應(yīng)用,。因此,許多公司推出了各種型號的擴(kuò)頻集成電路,典型的有STEL-2000A,,該芯片因外圍電路簡單而得到了廣泛應(yīng)用,。

然而,由于該芯片是基于專用集成電路(ASIC)技術(shù),,其內(nèi)部電路和大部分功能已經(jīng)固化,,對不同的場合缺乏靈活性,對以后系統(tǒng)升級也造成很大困難,。而現(xiàn)場可編程門陣列(FPGA)內(nèi)部資源豐富,,功能強(qiáng)大,并且可重復(fù)編程,,現(xiàn)場可修改設(shè)計(jì),,加之其相應(yīng)的EDA軟件功能完善,仿真能力好,,有豐富的IP核資源,,在成本和靈活性等方面都有很大優(yōu)勢,使得利用FPGA進(jìn)行復(fù)雜數(shù)字系統(tǒng)的設(shè)計(jì)已成為主流,。

近幾年來國內(nèi)外有許多學(xué)者利用FPGA對擴(kuò)頻通信系統(tǒng)中的某一個(gè)模塊進(jìn)行設(shè)計(jì),,如:數(shù)控振蕩器、PN碼發(fā)生器,、匹配濾波器,。也有學(xué)者嘗試對整個(gè)系統(tǒng)進(jìn)行設(shè)計(jì),但這些努力大多僅限于軟件上的功能仿真,,并且對一些關(guān)鍵模塊缺乏清晰的描述,。

本文對擴(kuò)頻芯片關(guān)鍵模塊的實(shí)現(xiàn)方法進(jìn)行了闡述,并推導(dǎo)出詳細(xì)參數(shù),,基于ISE 10.1實(shí)現(xiàn)了整個(gè)系統(tǒng),,最后下載到FPGA芯片中調(diào)試成功。

1 STEL-2000A系統(tǒng)的整體框架

1.1 發(fā)射子系統(tǒng)

在發(fā)射子系統(tǒng)中,,如圖1所示,,輸入的串行二進(jìn)制數(shù)據(jù)序列首先進(jìn)行串并轉(zhuǎn)換,分成兩路(I路和Q路)速率減半的序列,,由于采用QPSK調(diào)制方式,,為了避免相位模糊問題,在串并轉(zhuǎn)換后進(jìn)行差分編碼,,然后將差分編碼器的輸出序列與PN碼生成器輸出的偽隨機(jī)序列進(jìn)行異或運(yùn)算,,完成信號的頻譜擴(kuò)展,再將擴(kuò)頻輸出的兩路數(shù)據(jù)分別與數(shù)控振蕩器(NumericallyContmlkd Oscillator,,NCO)的兩路正交載波輸出各自相乘,,最后將相乘后的結(jié)果相加,,這樣就實(shí)現(xiàn)了DQPSK調(diào)制,輸出的是數(shù)字化的已調(diào)信號,。

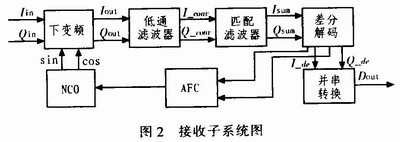

1.2 接收子系統(tǒng)

接收系統(tǒng)要完成數(shù)字中頻信號到基帶信號的轉(zhuǎn)換,、信號的捕獲、同步,、解擴(kuò),、差分解調(diào)以及并串轉(zhuǎn)換等功能,如圖2所示,。進(jìn)入接收系統(tǒng)的是經(jīng)正交采樣(Quadraturc Samping)后的數(shù)字中頻信號,,經(jīng)下變頻器生成基帶信號,,再將其輸出送入匹配濾波器,。在匹配濾波器中,主要實(shí)現(xiàn)信號的同步與解擴(kuò),。解擴(kuò)后的數(shù)據(jù)進(jìn)行差分解調(diào),,差分解調(diào)過程中的中間結(jié)果送入自動(dòng)頻率控制(Automatic Frequency Control,AF-C)模塊以生成校正信號來自動(dòng)調(diào)整NCO的輸出頻率,,最后將解調(diào)輸出數(shù)據(jù)經(jīng)并串轉(zhuǎn)換便得到原始數(shù)據(jù)序列,。

2 關(guān)鍵模塊分析與實(shí)現(xiàn)

2.1 NCO模塊

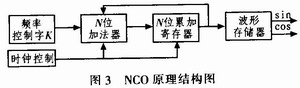

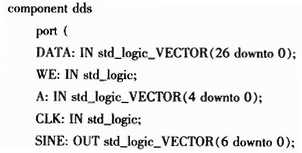

NCO采用Xilinx公司提供的直接數(shù)字式頻率合成器(Direct Digital Synthesizer,DDS)IP核,,DDS的工作原理如圖3所示,,在參考時(shí)鐘的驅(qū)動(dòng)下,N位加法器對頻率控制字K和N位累加寄存器中的值進(jìn)行相加,,相加后的結(jié)果存入累加寄存器中,,以累加寄存器中的值為地址將波形存儲(chǔ)器里相應(yīng)地址的數(shù)據(jù)讀出,即輸出正弦或余弦信號的幅度值,。

累加寄存器長度為N,,則波形存儲(chǔ)器2N用個(gè)樣點(diǎn)來表示正弦波的一個(gè)周期,地址每次累加K相當(dāng)于每隔K個(gè)點(diǎn)輸出一次,,輸出一個(gè)完整的正弦波需要時(shí)間![]() ,,則DDS的輸出頻率fout滿足關(guān)系式

,,則DDS的輸出頻率fout滿足關(guān)系式![]() 。當(dāng)K取1時(shí)輸出頻率為最大頻率分辨率

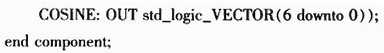

。當(dāng)K取1時(shí)輸出頻率為最大頻率分辨率![]() ,。參數(shù)設(shè)置主時(shí)鐘為100 MHz,,△f=1.0 Hz,可得N=27,,由于要求的輸出頻率為2 MHz,,可得:K=2 684 355。據(jù)此對DDS IP核進(jìn)行元件例化程序如下:

,。參數(shù)設(shè)置主時(shí)鐘為100 MHz,,△f=1.0 Hz,可得N=27,,由于要求的輸出頻率為2 MHz,,可得:K=2 684 355。據(jù)此對DDS IP核進(jìn)行元件例化程序如下:

2.2 下變頻模塊

下變頻模塊主要是將輸入的數(shù)字中頻信號進(jìn)行數(shù)字式下變頻,,從而產(chǎn)生基帶信號,,即待解擴(kuò)的信號,。設(shè)輸入信號是經(jīng)正交采樣后的數(shù)字中頻信號:

![]()

式中,I_PN和Q_PN為擴(kuò)頻后的信號,,ω為本地NCO產(chǎn)生的正弦和余弦信號的角頻率,。

讓輸入信號與本地NCO產(chǎn)生的正弦與余弦信號進(jìn)行相乘,即:

這里需要4個(gè)乘法器和2個(gè)加法器,,由于對乘法器的速度要求較高,,本系統(tǒng)調(diào)用了Virtex-II Pro開發(fā)板上FPGA芯片XC2VP30的硬核乘法器。將Iout和Qout進(jìn)行低通濾波就得到基帶信號,。

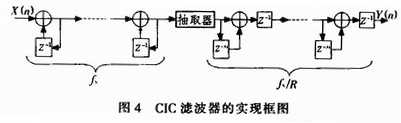

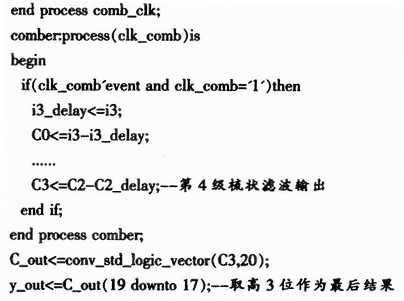

對于低通濾波器的實(shí)現(xiàn),,STEL-2000A使用了積分清洗濾波器(Integrate and Dump Filter,I&D),。本系統(tǒng)采用比較成熟且實(shí)現(xiàn)方便的級聯(lián)積分梳狀(CIC)濾波器來實(shí)現(xiàn)低通濾波的功能,。該濾波器由加法器、反相器和延時(shí)器構(gòu)成,,不需要乘法器,,這比一般的FIR和IIR節(jié)省很多FPGA資源。實(shí)現(xiàn)框圖如圖4所示,,fs為采樣頻率,。

系統(tǒng)中CIC濾波器參數(shù)的設(shè)置為:M=1,N=4,,R=20,。為了保證運(yùn)算不發(fā)生溢出,可以根據(jù)公式:![]() ,,計(jì)算出內(nèi)部需要的最大信號線寬度,。在本系統(tǒng)中輸入信號線寬度B=3,則取BMAX=20,。為減少后端匹配濾波器的運(yùn)算量,,取CIC濾波器輸出的高三位近似。

,,計(jì)算出內(nèi)部需要的最大信號線寬度,。在本系統(tǒng)中輸入信號線寬度B=3,則取BMAX=20,。為減少后端匹配濾波器的運(yùn)算量,,取CIC濾波器輸出的高三位近似。

CIC濾波器部分設(shè)計(jì)程序如下:

2.3 匹配濾波器模塊

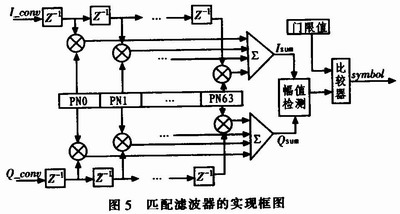

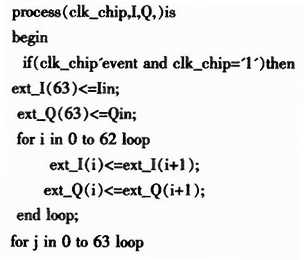

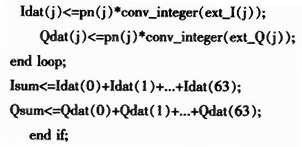

匹配濾波器實(shí)現(xiàn)信號的同步與解擴(kuò),,CIC濾波器的輸出I_conv,、Q_conv分別經(jīng)過兩組延時(shí)器,然后與本地PN碼序列相乘,,將所有相乘的結(jié)果相加,。理論上講下變頻送來的基帶擴(kuò)頻信號經(jīng)匹配濾波器后在給定的觀測時(shí)刻相關(guān)峰值為:Isum=Acosψk(t),Qsum=Asinψk(t),,ψk(t)為在給定觀測t時(shí)刻第k個(gè)符號的載波相位,。

相關(guān)峰幅值![]() ,在STEL-2000A中作如下近似:

,在STEL-2000A中作如下近似:

![]()

得到相關(guān)峰幅值后,,與一個(gè)預(yù)設(shè)好的門限值進(jìn)行比較,,當(dāng)峰值大于門限值時(shí),,表示發(fā)送的序列與PN碼寄存器里的偽隨機(jī)序列對齊,此時(shí)輸出一個(gè)定位脈沖sybmol,,其實(shí)現(xiàn)框圖如圖5所示,。

匹配濾波器部分設(shè)計(jì)程序如下:

2.4 差分解調(diào)模塊

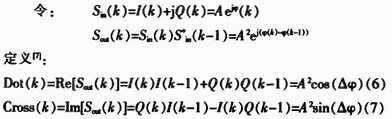

當(dāng)檢測到定位脈沖時(shí)(即檢測到相關(guān)峰最大幅值),將此時(shí)Isum和Qsum的值送入寄存器以供差分解調(diào)使用,。對于DQPSK的解調(diào),,關(guān)鍵是判斷第k位和第k-1位符號之間的相位差△ψ,STEL-2000A中引入點(diǎn)積Dot和叉積Cross來判斷△ω,。

信號經(jīng)匹配濾波器后,,基帶信號可為:I(k)=Acosψ(k),Q(k)=Asinψ(k),。ψ(k)為第k個(gè)符號的載波相位,。

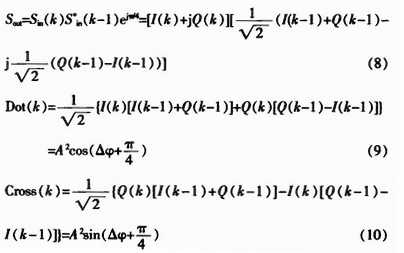

由于本系統(tǒng)采用DQPSK調(diào)制方式,所以△ψ的取值有0,,π/2,,π和3π/2四種,sin(△ψ)和cos(△ψ)的取值有0,,+1,-1三種,,在進(jìn)行最佳判決接收時(shí)相對較難實(shí)現(xiàn),。本系統(tǒng)引入了π/4的固定相移。給出簡單的推導(dǎo)如下:

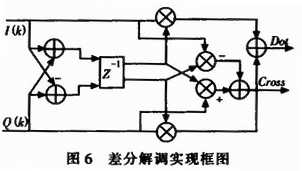

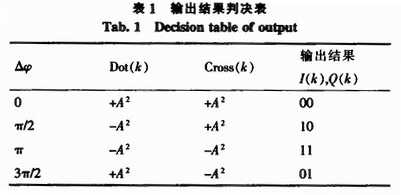

從式(9),、式(10)可以發(fā)現(xiàn)只需要在延時(shí)之前對兩路信號進(jìn)行簡單的算術(shù)組合即可得到π/4的固定相移,,差分解調(diào)器實(shí)現(xiàn)框圖如圖6所示。輸出的Dot(k)和Cross(k)值查表1,,即可得到最后的差分解調(diào)結(jié)果,。

3 測試結(jié)果

測試系統(tǒng)為FPGA產(chǎn)生輸入信號“01011001”的周期循環(huán)序列,輸入信號經(jīng)過發(fā)射模塊后的數(shù)字信號輸出直接進(jìn)入接收模塊,,輸入信號產(chǎn)生模塊,、發(fā)射模塊和接收模塊都在同一塊FPGA芯片內(nèi)。系統(tǒng)的參數(shù)設(shè)置為:主時(shí)鐘為100 MHz,,數(shù)據(jù)最大速率為31.25 Kb/s,,工作時(shí)鐘為31.25 kHz,PN碼長為64位,,速率為1 Mchip/s,,NCO的工作時(shí)鐘為100 MHz,輸出的數(shù)字正弦和余弦信號頻率為2 MHz,。

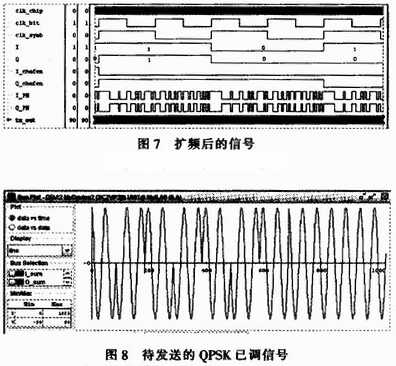

通過在線分析儀ChipScope Pro,,可以看到經(jīng)QPSK調(diào)制后待輸出的信號(圖7,,8),其中圖7的I和Q是串并轉(zhuǎn)換后的信號,,此時(shí)的輸入信號為“10110010”,,I_chafen和Q_chafen是差分編碼后的信號,I_PN和Q_PN信號是經(jīng)過擴(kuò)頻后的信號,,tx_out是最后的已調(diào)信號,。將已調(diào)信號繪制成曲線如圖8所示。

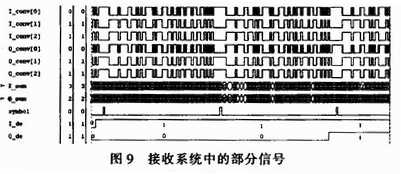

在接收部分,,利用ChipScope Pro可以觀察到下變頻器的輸出信號I_conv和Q_conv,,匹配濾波器的輸出信號,Isum,、和Qsum定位脈沖sym-bol(圖9),,I_de和Q_de為差分解調(diào)后的信號,圖中顯示此時(shí)的解調(diào)結(jié)果為“00101011”,,相對于輸入信號而言只是有一段時(shí)延,,從而驗(yàn)證該系統(tǒng)實(shí)現(xiàn)了STEL-2000A的核心功能。

4 結(jié)論

通過對擴(kuò)頻芯片STEL-2000A的功能研究,,詳細(xì)分析了其關(guān)鍵模塊的基本原理,。在此基礎(chǔ)上,利用FPGA實(shí)現(xiàn)了整個(gè)系統(tǒng)的功能,,并對其進(jìn)行了測試,。測試結(jié)果表明該系統(tǒng)功能的正確性。另外,,由于FPGA的靈活性,,系統(tǒng)可以根據(jù)不同場合改變其中的參數(shù),比如改變PN碼的長度,、改變CIC濾波器的級數(shù)和抽取系數(shù),、調(diào)整匹配濾波器的門限值等以適應(yīng)其在不同應(yīng)用場合的需要。