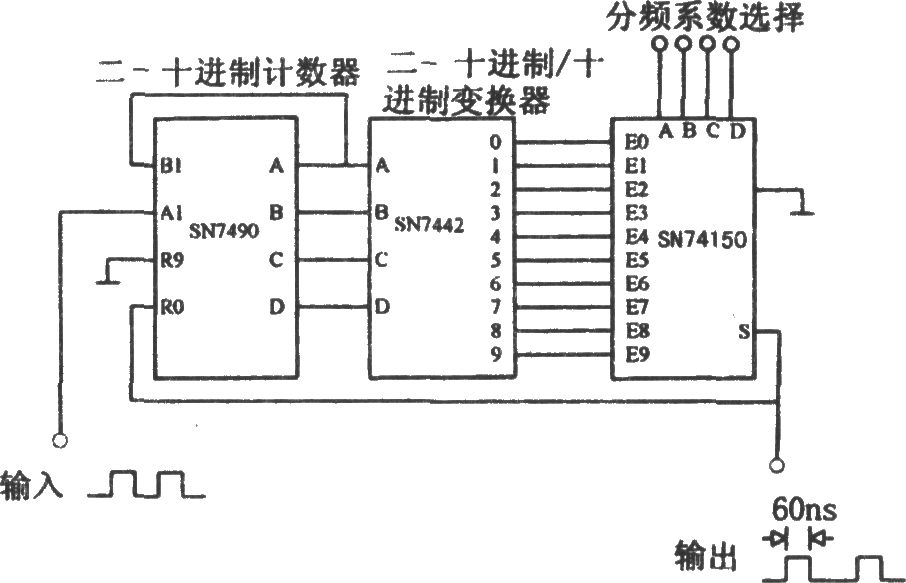

如圖所示為數(shù)字分頻電路。該電路由3塊集成電路構(gòu)成,分頻系數(shù)可以從1~9變化。計(jì)數(shù)器SN7490輸出的二-十進(jìn)制數(shù)送至譯碼器SN7442,譯碼器輸出為十進(jìn)制數(shù)。分頻系數(shù)由數(shù)據(jù)選擇器SN74150確定。數(shù)據(jù)選擇器的輸出反饋到SN7490的復(fù)位輸入端,即每次計(jì)數(shù)周期結(jié)束時(shí)輸出一個(gè)脈沖,該脈沖同時(shí)使計(jì)數(shù)器SN7490復(fù)位。輸出脈沖寬度為60ns,它由電路的傳輸延遲時(shí)間決定。用這種非頻器級(jí)聯(lián),可以構(gòu)成更大分頻系數(shù)的分頻器。

如圖所示為數(shù)字分頻電路。該電路由3塊集成電路構(gòu)成,分頻系數(shù)可以從1~9變化。計(jì)數(shù)器SN7490輸出的二-十進(jìn)制數(shù)送至譯碼器SN7442,譯碼器輸出為十進(jìn)制數(shù)。分頻系數(shù)由數(shù)據(jù)選擇器SN74150確定。數(shù)據(jù)選擇器的輸出反饋到SN7490的復(fù)位輸入端,即每次計(jì)數(shù)周期結(jié)束時(shí)輸出一個(gè)脈沖,該脈沖同時(shí)使計(jì)數(shù)器SN7490復(fù)位。輸出脈沖寬度為60ns,它由電路的傳輸延遲時(shí)間決定。用這種非頻器級(jí)聯(lián),可以構(gòu)成更大分頻系數(shù)的分頻器。