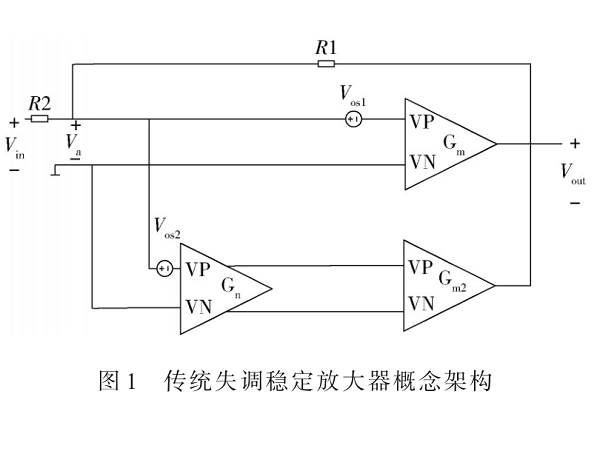

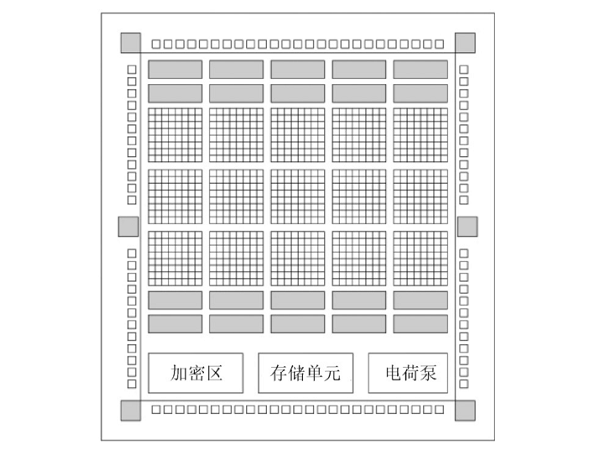

一種應(yīng)用于電流檢測的低失調(diào)運算放大器設(shè)計[模擬設(shè)計][工業(yè)自動化]

發(fā)表于:5/14/2025 3:24:23 PM

數(shù)字經(jīng)濟下跨境避稅與反避稅規(guī)則研究[其他][其他]

發(fā)表于:4/28/2025 2:55:14 PM

司法自動化決策的紓困原理與算法解釋權(quán)路徑展開[其他][其他]

發(fā)表于:4/28/2025 2:15:06 PM

藏文網(wǎng)絡(luò)敏感信息檢測研究[人工智能][信息安全]

發(fā)表于:4/28/2025 1:58:03 PM

醫(yī)療人工智能領(lǐng)域同意規(guī)則的困境與出路[人工智能][信息安全]

發(fā)表于:4/27/2025 5:07:31 PM

元宇宙環(huán)境中版權(quán)保護的邏輯轉(zhuǎn)型與規(guī)則發(fā)展[其他][其他]

發(fā)表于:4/27/2025 4:56:31 PM

數(shù)據(jù)分級分類授權(quán)確權(quán)的空間治理之道——基于國內(nèi)外數(shù)據(jù)管理實踐展開[其他][其他]

發(fā)表于:4/27/2025 4:44:29 PM

基于數(shù)據(jù)中臺的地理信息要素融合治理的構(gòu)想與實踐[其他][數(shù)據(jù)中心]

發(fā)表于:4/27/2025 4:28:36 PM