盡管晶體管的延遲時間會隨著晶體管溝道長度尺寸的縮小而縮短,但與此同時互聯(lián)電路部分的延遲則會提升。舉例而言,90nm制程晶體管的延遲時間大約在 1.6ps左右,而此時互聯(lián)電路中每1mm長度尺寸的互聯(lián)線路,其延遲時間會增加500ps左右;根據(jù)ITRS技術(shù)發(fā)展路線圖的預(yù)計,到22nm制程節(jié)點,晶體管的延遲時間會達到0.4ps水平,而互聯(lián)線路的延遲則會增加到1萬ps水平。

對晶體管而言,晶體管的尺寸越小則運行速度也越快,但與此同時,互聯(lián)層線路的電阻則會隨著線路截面積的縮小而增大。表面散射現(xiàn)象,晶界散射現(xiàn)象,和擴散勢壘層(這里指防止互聯(lián)層金屬材料相互擴散而制成的擴散阻擋層)電阻值的不斷增加,是導(dǎo)致互聯(lián)層RC延遲增加的主要原因。雖然3D集成(3-D integration)技術(shù)的顯見優(yōu)點之一是可以減小互聯(lián)線的長度,但是同時這種技術(shù)的應(yīng)用能否對減小板級,或線路極互聯(lián)線長度起到積極作用也是應(yīng)該考慮的。

以TSV為核心的3D集成技術(shù):

以TSV穿硅互聯(lián)技術(shù)為核心的3D集成技術(shù)主要影響的是芯片之間的互聯(lián)結(jié)構(gòu),因此這種技術(shù)主要減小的是芯片間互聯(lián)需用的電路板面積。這種技術(shù)一般是采用將多塊存儲或邏輯功能芯片垂直堆疊在一起,并將堆疊結(jié)構(gòu)中上一層芯中制出的TSV連接在下層芯片頂部的焊墊(Bond pad)上的方式來實現(xiàn)。不過此時堆疊結(jié)構(gòu)中的每一層芯片都采用獨自的設(shè)計,仍為傳統(tǒng)的二維結(jié)構(gòu),因此每一層芯片內(nèi)部的電路級互聯(lián)仍為傳統(tǒng)的二維設(shè)計。

單片型3D堆疊技術(shù):(MonolithIC 3D)

相比之下,單片型3D技術(shù)中,芯片內(nèi)部互聯(lián)層的3D化則更加徹底,因此人們通常稱這種技術(shù)為“真3D集成設(shè)計”。此時芯片堆疊結(jié)構(gòu)中每一層芯片均作為整體中的一個功能單元來設(shè)計,這樣堆疊結(jié)構(gòu)中各層芯片(此時應(yīng)當稱之為功能單元可能較為合適些)內(nèi)部都可以采用同樣的互聯(lián)結(jié)構(gòu)(不論是垂直方向,還是水平方向的互聯(lián)),因此這種設(shè)計可以讓互聯(lián)線的長度進一步降低。而且由于采用統(tǒng)一化設(shè)計,信號中繼電路等所占用的面積也更小,因此芯片的總體占地面積可以更小。根據(jù)華盛頓大學Lili Zhou等人在ICCD2007會議上發(fā)表的論文,這種真3D集成設(shè)計可以令芯片的尺寸減半,互聯(lián)線總長度則可減小2/3.

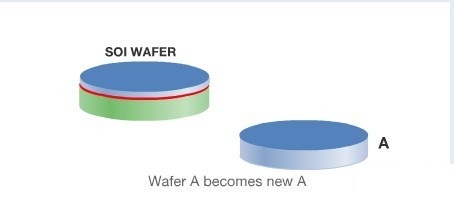

SOI晶圓廠商Soitec的SMARTCUT技術(shù)

單片型3D技術(shù)實現(xiàn)的關(guān)鍵在于如何將各層功能單元轉(zhuǎn)換到單片3D堆疊結(jié)構(gòu)之中去,其采用的方法非常類似于Soitec在制作SOI晶圓時所采用的SMARTCUT技術(shù)。由于單片3D堆疊芯片中的過孔只需要從各層功能單元的有源層(Active layer:簡單說就是晶體管中覆蓋在柵絕緣層之下的部分)部分穿過,因此其尺寸要比常規(guī)的TSV小得多,僅比2D芯片頂部互聯(lián)層的尺寸大3倍左右。據(jù)研發(fā)這種技術(shù)的公司宣稱,在許多應(yīng)用中,這種技術(shù)可實現(xiàn)的芯片微縮程度可相當于進步了一個制程級別的水平,而且同時還不需要研發(fā)特別的制程技術(shù)或者購買昂貴的專用制造設(shè)備。

表面上看,單片型3D技術(shù)的特性是非常引人入勝的,但是由于目前這項技術(shù)還未能完全實現(xiàn),因此現(xiàn)在要評估這項技術(shù)的未來發(fā)展狀況難度極大。