在任何一個(gè)設(shè)計(jì)人員的工具箱里,集成電路放大器都是最基本的構(gòu)件模塊之一,它也是目前市面上最全能的產(chǎn)品之一。放大器具有多項(xiàng)功能,比如驅(qū)動ADC,驅(qū)動多個(gè)視頻負(fù)載,作為視頻或其他類型濾波器而工作,驅(qū)動高速儀器信號等等。它們還可以作為振蕩器,不過,實(shí)際中這種方案的確存在一些問題,因?yàn)榉糯笃鲬?yīng)該只在設(shè)計(jì)人員需要的時(shí)候才振蕩。而如果電路板設(shè)計(jì)不正確,放大器卻會自行其是,隨意振蕩。那么,設(shè)計(jì)人員應(yīng)該怎么做才能避免這種有害的振蕩呢?試回憶一下我們以前在電子課程里學(xué)過的知識,即振蕩與電容、電感和反饋相關(guān)。因此,關(guān)鍵在于精心設(shè)計(jì)電路板,確保減少或消除任何無關(guān)的電容性和電感性反饋路徑。對于較高速的放大器(大于50MHz),這尤其重要。

電路板、負(fù)載(尤其是電容性負(fù)載),以及/或版圖設(shè)計(jì),都會帶來無形的電容和電感。此外,流入電路板各處旁路電容的電流可能產(chǎn)生不同的路徑,導(dǎo)致失真。因此,有些號稱減少失真的技術(shù)其實(shí)是適得其反,與避免振蕩的設(shè)計(jì)規(guī)則背道而馳。(設(shè)計(jì)人員的工作從來非易事,的確如此)那么,在進(jìn)行放大器或視頻濾波器的版圖設(shè)計(jì)時(shí),為了保持全局平衡,減少失真和振蕩,需要考慮到哪些事項(xiàng)呢?

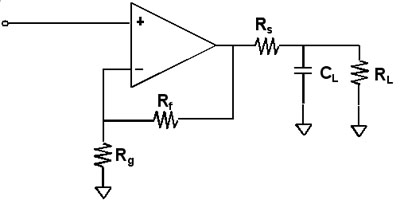

首先看看振蕩器,在利用放大器直接驅(qū)動電容性負(fù)載時(shí),負(fù)載會與放大器的輸出阻抗會產(chǎn)生相位滯后,而相位滯后將導(dǎo)致脈沖尖峰或振蕩。有些放大器能夠直接驅(qū)動電容性負(fù)載,但有些放大器則需要在放大器的輸出端增加一個(gè)小串聯(lián)電阻(Rs)來提高放大器的穩(wěn)定性和建立時(shí)間(settling time)性能。

圖1

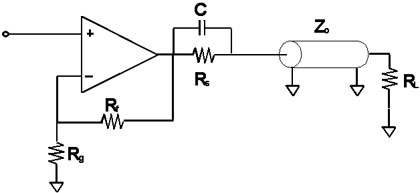

圖2給出了驅(qū)動傳輸電纜(如同軸電纜)的典型電路配置圖。電阻Rs和RL應(yīng)該等于電纜的特征阻抗(Zo),而電容C應(yīng)該可被用來在更大的頻率范圍對電纜進(jìn)行匹配,以對隨頻率提高而增加的放大器輸出阻抗進(jìn)行補(bǔ)償。

圖2:驅(qū)動電纜或傳輸線的典型電路圖

高頻放大器很容易受電路布局所致失真的影響,即使是低頻放大器,比如音頻放大器,也具有非常嚴(yán)格的失真要求。失真(THD)是音頻質(zhì)量的主要指標(biāo),因此,減少版圖引起的失真十分關(guān)鍵。

失真的一個(gè)重要原因是PCB中的接地電流效應(yīng)。這種效應(yīng)來自于流入每個(gè)電源和各電源旁路電容的電流,該電流與路徑的電導(dǎo)率成比例。各個(gè)不同路徑都存在不同的傳導(dǎo)性,從而導(dǎo)致失真。因?yàn)榧词筆CB本身的材料是線性的,電路板的行為也會表現(xiàn)出“空間非線性”特性。這是因?yàn)榕月冯娙莘植荚陔娐钒宓牟煌恢茫瑢?dǎo)致接地電流沿不同的路徑流入各個(gè)旁路電容。路徑不同導(dǎo)致接地電流流經(jīng)的接地電阻輸入一端的電壓受到影響,而另一端則不會。結(jié)果是輸入信號電壓被不均衡得調(diào)整,導(dǎo)致非線性的產(chǎn)生。在這種情況下,如果一個(gè)極性被調(diào)節(jié),而另一個(gè)卻沒有,就會造成二次諧波失真。換一句話說,如果只有正弦波的一個(gè)極性被調(diào)節(jié),結(jié)果將不再是正弦波,這種失真的影響是顯而易見的。為了避免失真,設(shè)計(jì)人員可以使用共有接地點(diǎn)并在輸出端采用接地旁路電容。

高頻電路板版圖設(shè)計(jì)的主要規(guī)則是使高頻旁路電容盡可能靠近封裝的電源引腳。不過,實(shí)驗(yàn)顯示,稍微延長高頻旁路電容的連接走線可以提高平坦度和差分增益,從而減少失真。設(shè)計(jì)規(guī)則當(dāng)然有益,而設(shè)計(jì)人員的實(shí)驗(yàn)經(jīng)驗(yàn)也十分有用,可以確保規(guī)則與實(shí)際的一致性。

在電路板上設(shè)計(jì)視頻濾波驅(qū)動器時(shí),很重要的一點(diǎn)是,應(yīng)該把輸入耦合電容和端接電阻靠近輸入引腳放置,以獲得最佳信號完整性。圖3所示為視頻濾波器/驅(qū)動器的一種典型AC耦合輸入配置。在這種配置中,采用0.1uF陶瓷電容來對輸入信號進(jìn)行AC耦合。如果輸入信號不低于接地電位,鉗位電路不激活;但若輸入信號低于接地電位,則鉗位電路會把同步端最低電壓設(shè)置為恰好低于接地電位。鉗位電路設(shè)置的輸入電平,結(jié)合內(nèi)部DC偏移量,將使輸出信號保持在可接受的范圍之內(nèi),大約在250mV左右。這種鉗位特性還允許參考電平為地的DAC輸出直接驅(qū)動直流耦合輸入。

圖3

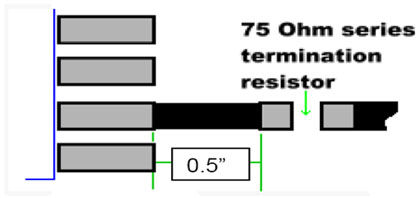

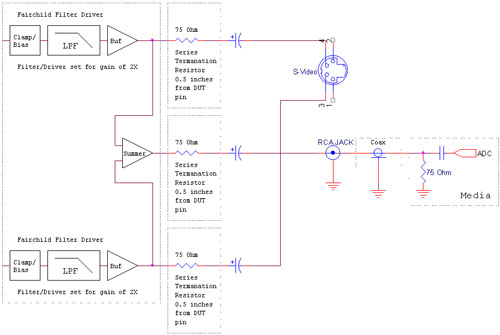

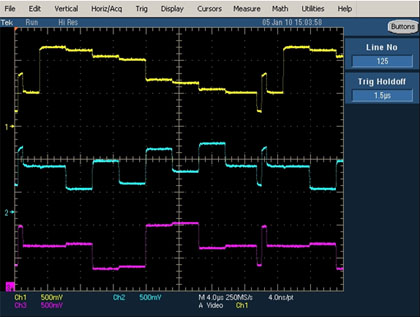

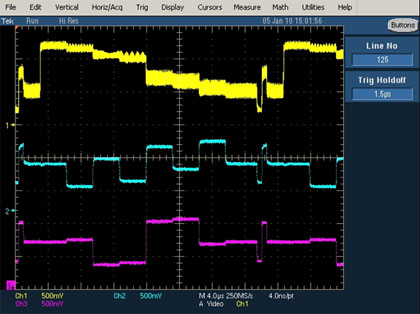

為了獲得最高的輸出信號質(zhì)量,串聯(lián)端接電阻必須盡可能靠近器件的輸出引腳放置。這將大大減少寄生電容和寄生電感對驅(qū)動器輸出的影響。從器件引腳到串聯(lián)端接電阻的距離不應(yīng)該超過0.5英寸(見圖4)。圖5是作為多媒體設(shè)備中作為輸出驅(qū)動器的視頻濾波器/驅(qū)動器的典型原理示意圖。在圖5所示的情況下,多媒體設(shè)備的復(fù)合視頻信號端子接多媒體設(shè)備,S視頻輸出端子開通。在這時(shí),讓串聯(lián)端接電阻靠近器件的輸出引腳非常關(guān)鍵,可以把寄生電容對濾波器輸出驅(qū)動器的影響降至最小,從而避免輸出端出現(xiàn)振蕩。圖6所示為飛兆半導(dǎo)體的FMS6346A視頻濾波驅(qū)動器驅(qū)動25pF 的負(fù)載,圖7所示為FMS6346A驅(qū)動47pF的電容性負(fù)載。這表明,電容越小,性能越好。

圖4

圖5 FMS6346A 視頻濾波器輸出到 S-視頻

圖6 FMS6346A 視頻濾波驅(qū)動器驅(qū)動25pF 的負(fù)載

圖7 FMS6346A 驅(qū)動 47pF 的電容性負(fù)載

那么,考慮到了電路布局對性能的所有可能的影響,設(shè)計(jì)人員可以做些什么來確保版圖避免振蕩、失真和總體信號質(zhì)量低下呢?下面的基本版圖和旁路電容設(shè)計(jì)指南“設(shè)計(jì)規(guī)則13條(Lucky 13)”可能頗有裨益:

“設(shè)計(jì)規(guī)則 13條”

1) RTM (仔細(xì)閱讀產(chǎn)品手冊)。放大器的數(shù)據(jù)手冊一般都會給出它的最小穩(wěn)定增益要求。該指標(biāo)至關(guān)重要,如果放大器的工作增益小于推薦的最小穩(wěn)定增益,就可能產(chǎn)生振蕩。

2)采用一個(gè)接地平面。這是為元件提供低感性接地連接的最好方法。

3) 去掉放大器下面和周圍的接地平面,去掉敏感引腳附近的接地平面。去掉高速放大器輸入輸出引腳附近的接地平面,可以減少雜散電容。同樣,去掉放大器下面和周圍的接地平面也很有幫助。

4) 采用表面貼裝元件。這類元件的引腳電感很小。

5) 盡可能縮短引腳長度。 縮短引腳長度可以減少放大器反相輸入端的串聯(lián)電感。

6) 避免使用插槽。避免使用插槽,或者最多使用嵌入式插槽 (flush-mount),以減少電感。

7) 采用推薦的反饋電阻值。在使用電流反饋放大器時(shí),這一點(diǎn)十分重要。

8) 不要在放大器的直接反饋回路中使用非線性元件 (如電容器) 。

9) 采用一個(gè)反饋電阻來實(shí)現(xiàn)單位增益配置。而不要使用標(biāo)準(zhǔn)的電壓跟隨(voltage-follower)電路。

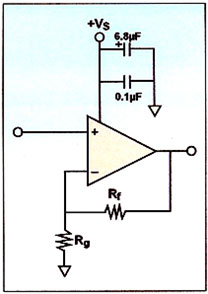

10) 使用旁路電容。在每個(gè)電源上增加一個(gè)旁路電容有助于降低電源引腳處的回流電流路徑阻抗,提高電源噪聲抑制能力,并對電源走線進(jìn)行高頻過濾。大多數(shù)廠商都推薦使用6.8uF鉭電容和0.1uF陶瓷電容。為獲得最佳性能,應(yīng)該按照以下規(guī)則放置電容:6.8uF電容距電源引腳不超過0.75英寸,0.1uF電容距電源引腳不超過0.1英寸。當(dāng)兩者的距離增加時(shí),由于走線電感增加,電容的濾波效果下降。不過,這也需要與失真考慮事項(xiàng)進(jìn)行權(quán)衡,因?yàn)閷?shí)驗(yàn)結(jié)果顯示,該距離延長一點(diǎn)點(diǎn)會改善失真性能。

圖8

圖8所示為一個(gè)單電源放大器示例。如果使用雙電源放大器,則只需在其它電源上增加相同的旁路電容即可。

11) 調(diào)整旁路電容,減小失真。當(dāng)單個(gè)運(yùn)算放大器因接地電流路徑而產(chǎn)生失真時(shí),可調(diào)整旁路元件,對接地電流進(jìn)行調(diào)節(jié),使其遠(yuǎn)離輸入元件。這十分簡單,只需調(diào)整旁路電容,使它的接地連接遠(yuǎn)離輸入即可。

12)對于視頻濾波器,使串聯(lián)端接電阻靠近輸出引腳放置。這樣做可以把寄生電容對濾波器輸出驅(qū)動器的影響減至最小,從而避免輸出端出現(xiàn)振蕩。

13) 輸入耦合電容和端接電阻靠近輸入引腳放置,以獲得最佳信號完整性。

電路板布局對系統(tǒng)性能的影響非常大,因此,在版圖設(shè)計(jì)階段,應(yīng)該謹(jǐn)慎監(jiān)測,避免失誤。當(dāng)有疑慮時(shí),請聯(lián)系放大器或視頻濾波器供應(yīng)商,他們會很樂意提供幫助。