雖然在較低頻率下可以較輕松地檢查一個(gè)簡單放大器的穩(wěn)定性,但評(píng)估一個(gè)較為復(fù)雜的電路是否穩(wěn)定,難度可能會(huì)大得多。本文使用常見的Pspice宏模型結(jié)合一些簡單的電路設(shè)計(jì)技巧來提高設(shè)計(jì)工程師的設(shè)計(jì)能力,以確保其設(shè)計(jì)的實(shí)用性與穩(wěn)定性。

導(dǎo)致放大器不穩(wěn)定的原因

在任何相關(guān)頻率下,只要環(huán)路增益不轉(zhuǎn)變?yōu)檎答仯瑒t閉環(huán)系統(tǒng)穩(wěn)定。環(huán)路增益是一個(gè)相量,因而具有幅度和相位特性。環(huán)路由理想的負(fù)反饋轉(zhuǎn)變?yōu)檎答佀鶐淼念~外相移即是最常見的不穩(wěn)定因素。環(huán)路增益相位的“相關(guān)”頻率,一般出現(xiàn)在環(huán)路增益大于或等于0dB之處。

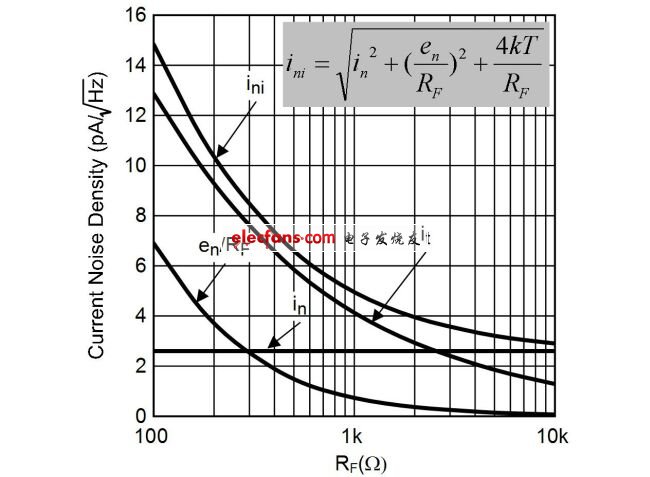

圖1:總等效噪聲密度-反饋電阻關(guān)系曲線。

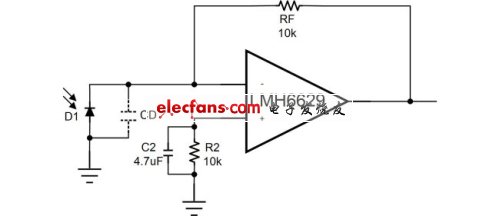

如圖2所示的放大器電路,通過斷開環(huán)路,測量信號(hào)在環(huán)路中傳播一次所產(chǎn)生的相移,即可推算出電路的穩(wěn)定情況。以下例子介紹的方法可利用仿真軟件,運(yùn)算放大器宏模型以及Pspice提供的理想元器件來實(shí)現(xiàn)。

圖2:跨阻抗放大器。

高速低噪聲跨阻放大器(TIA)穩(wěn)定性示例

我們以一個(gè)跨阻放大器(TIA)為例,通過分析其穩(wěn)定性來闡述我們將要推薦的技術(shù)。TIA廣泛應(yīng)用在工業(yè)領(lǐng)域和消費(fèi)領(lǐng)域,例如LIDAR(光探測和測距)、條形碼掃描儀、工廠自動(dòng)化等。設(shè)計(jì)工程師遇到的挑戰(zhàn)是,在不會(huì)造成衰減和老化的情況下,如何最大化信噪比(SNR),以及如何獲得足夠的速度/帶寬來傳遞所需的信號(hào)。圖2為采用了LMH6629的放大器示意圖,這款超高速(GBWP=4GHz)低噪聲(0.69nV/RtHz)器件具有+10V/V的最小穩(wěn)定增益(COMP引腳連至VCC)的。LMH6629的補(bǔ)償(COMP)輸入可以連至VEE,從而進(jìn)一步將最小穩(wěn)定增益降低到4V/V。

為獲得最大的轉(zhuǎn)換速率和帶寬(小信號(hào)和大信號(hào)),在這個(gè)例子中,COMP引腳被連接到VCC。可獲得的帶寬與放大器GBWP直接相關(guān),與跨阻增益(RF)和光電二極管內(nèi)的寄生電容成反比。確定一個(gè)給定放大器所使用的反饋電阻(RF)有一個(gè)簡單方便的辦法:在使用了LMH6629的情況下,總等效輸入電流噪聲密度“ini”與RF的關(guān)系如圖1中曲線所示。圖中的“in”是LMH6629的輸入噪聲電流,“en”是LMH6629的輸入噪聲電壓,“k”是波爾茲曼常數(shù),而“T”是用℃表示的絕對(duì)溫度。

由圖1可知,對(duì)于LMH6629而言,將RF設(shè)定為10k?確保了最小的總等效輸入電流噪聲密度ini,由此也可以得到最高的SNR。RF的進(jìn)一步增加會(huì)降低可獲取的最大速度,而SNR不會(huì)得到明顯改善。

是什么使得一個(gè)看起來很簡單的電路的穩(wěn)定性分析變得如此復(fù)雜呢?主要原因就是寄生元件的影響。在圖2的電路中,幾乎沒有跡象表明這個(gè)電路會(huì)是不穩(wěn)定的,圖中所示的寄生元件“CD”是光電二極管固有電容,其實(shí)際大小由光電二極管的面積和靈敏度來決定。R2用于消除LMH6629的輸入偏置電流產(chǎn)生的偏移誤差,同時(shí)C2消除了R2的噪聲。

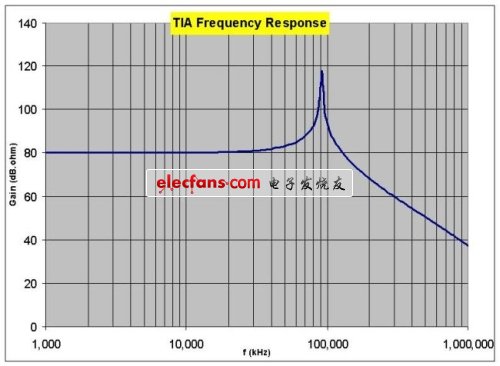

假設(shè)一個(gè)光電二極管標(biāo)稱電容(CD)為10pF,圖2中電路的仿真響應(yīng)如圖3所示,由此可以判斷出電路是不穩(wěn)定的:其頻率響應(yīng)曲線中大而尖的峰值即為證明。在頻域內(nèi),通過了解電路的相位裕度(PM)就可以確定電路的穩(wěn)定性。為便于仿真,可將光電二極管的電路簡化等效為一個(gè)電流源。

圖3:TIA頻率響應(yīng)示意電路的不穩(wěn)定性。

對(duì)于一個(gè)富有經(jīng)驗(yàn)的用戶來說,當(dāng)一個(gè)具有較大反饋電阻RF的系統(tǒng)不穩(wěn)定時(shí),意味著RF“尋找”運(yùn)算放大器反向輸入端的寄生電容,是產(chǎn)生振鈴和過沖的原因。在環(huán)路中,這種現(xiàn)象可稱為“過相移”。反向輸入寄生電容由光電二極管電容和LMH6629輸入電容組成。LMH6629的更高帶寬令問題進(jìn)一步惡化——總輸入電容的降低將足以引起過相移。對(duì)于這種情況,最有效的補(bǔ)救方法是在RF兩端并聯(lián)一個(gè)合適的電容(CF)。

為找出導(dǎo)致這一現(xiàn)象中低相位裕度的原因,除了全面的筆頭分析,設(shè)計(jì)人員只能反復(fù)試驗(yàn),通過選擇合適的補(bǔ)償元件來提高系統(tǒng)的穩(wěn)定性。一個(gè)更嚴(yán)密的辦法就是通過仿真來獲取對(duì)各種頻率下環(huán)路特性的更深入了解。這種辦法比起筆頭分析法要快得多,既不需要復(fù)雜的運(yùn)算,也不會(huì)帶來計(jì)算錯(cuò)誤的可能。設(shè)計(jì)人員要做的是在開環(huán)情況下觀察電路,以便了解環(huán)路增益(LG)的幅度和相位情況。仿真操作為用戶提供了能進(jìn)行高效分析的各種理想元件,從而使得上述分析成為可能。

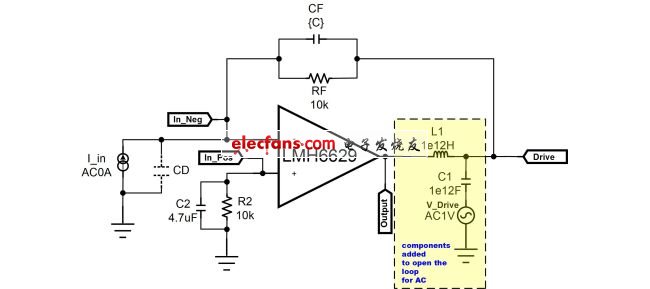

在圖4的仿真電路中,環(huán)路已在AC(與相位裕度有關(guān))處斷開,同時(shí)保留DC閉環(huán),以建立合適的操作點(diǎn)。在輸出處用一個(gè)大串聯(lián)電感(L1)和一個(gè)大并聯(lián)電容(C1)即可完成仿真。

圖4:為了進(jìn)行仿真,插入大“L”和“C”以斷開AC環(huán)路。

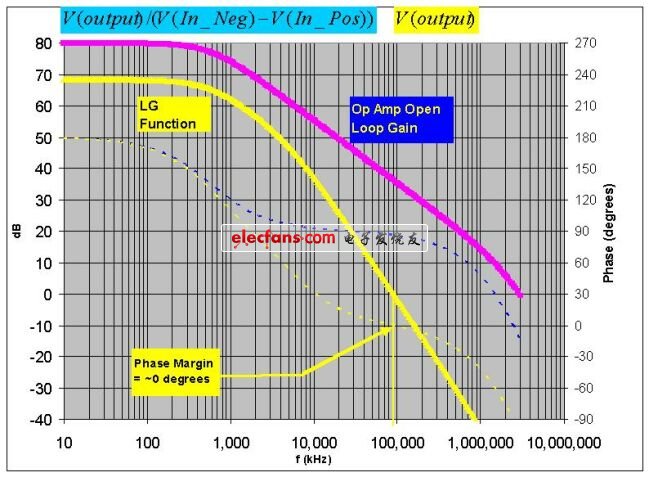

驅(qū)動(dòng)大電容(V_Drive)的交流電源可以設(shè)定為1V,在器件輸出端,仿真響應(yīng)如圖5中的LG函數(shù)所示。圖5中的0o低相位裕度印證了圖3中過高的閉環(huán)頻率響應(yīng)峰值。為確保電路的穩(wěn)定性,對(duì)應(yīng)的品質(zhì)因數(shù)即相位裕度應(yīng)大于45o。

圖5:開環(huán)曲線表明相位裕度不足。

請注意:在頻率響應(yīng)仿真開始之前,請確保將輸入電流源(取代光電二極管)設(shè)定為“AC 0”;顯示結(jié)果需將CF設(shè)為0pF;圖5中幅度用實(shí)線表示,相位角用虛線表示;當(dāng)相位裕度為0dB時(shí),相位裕度對(duì)應(yīng)LG函數(shù)的相位角。

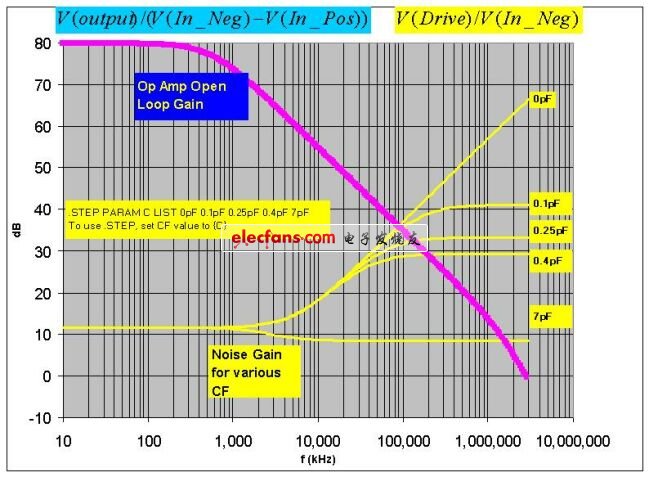

如圖6所示,為找到合適的補(bǔ)償電容值來改善相位裕度,我們可以將針對(duì)不同的CF值(圖4電路)的噪聲增益曲線和LMH6629開環(huán)增益曲線放在一起。噪聲增益為V(Drive)/V(In_Neg)。請注意LG的仿真低頻值要大于0dB,因?yàn)長MH6629的宏模型還包括了其差分輸入電阻。

圖6:CF最優(yōu)化噪聲增益曲線。

大部分Pspice仿真器都允許使用圖6所示的“.STEP PARAM”語句來進(jìn)行多級(jí)仿真并顯示迭加的結(jié)果。其它仿真器可能有專用命令來實(shí)現(xiàn)此類同步仿真功能。最優(yōu)CF值在噪聲增益函數(shù)與LMH6629的開環(huán)增益曲線相交頻率處給噪聲增益函數(shù)設(shè)置了一個(gè)極點(diǎn)。由圖6可知,在本例中,CF=0.25pF。

大于0.25pF的更高CF值將會(huì)帶來帶寬損失,相應(yīng)地,若CF低于0.25pF,相位裕度又將不足。如果CF足夠高(本例中是7pF),噪聲增益曲線有可能在低于20dB處與開環(huán)曲線相交。20dB是LMH6629的最小穩(wěn)定增益。這種情況下電路可能將不再穩(wěn)定或者放大器可能出現(xiàn)過高頻率響應(yīng)峰值。因此必須有一個(gè)穩(wěn)定范圍和最優(yōu)值。

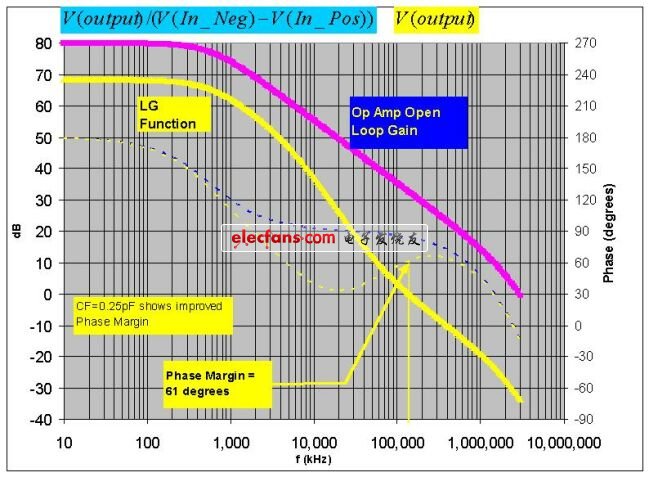

圖7所示的是當(dāng)CF=0.25pF時(shí),頻率函數(shù)LG的結(jié)果曲線。在沒有CF的情況下,相位裕度從原來的0o增加到61o。

圖7:開環(huán)曲線繪制驗(yàn)證CF令相位裕度得以改善。

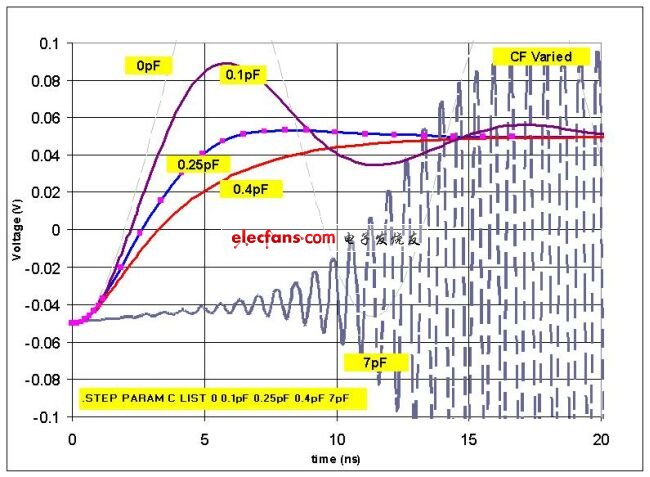

找到最優(yōu)CF值后,可以重新查看初始的閉環(huán)配置(沒有大電感和電容加入到LG和NG的研究中),在使用最優(yōu)CF值(此時(shí)是0.25pF)的情況下可以得到階躍響應(yīng)。圖8顯示了面向不同CF的響應(yīng)曲線,證實(shí)了CF值不論是偏大或是偏小,都會(huì)造成系統(tǒng)的不穩(wěn)定,或是振鈴時(shí)間和穩(wěn)定時(shí)間的延長;而最優(yōu)CF值可以在最小振鈴下實(shí)現(xiàn)非常好的階躍響應(yīng)。顯然,無論CF取值0pF還是7pF,電路都非常地不穩(wěn)定。這表明7pF時(shí)的振蕩頻率遠(yuǎn)高于0pF時(shí)的振蕩頻率,并不是因?yàn)樵肼曉鲆媾c放大器開環(huán)增益曲線的交接頻率較高(如圖6所預(yù)測的那樣)。

圖8:不同CF對(duì)應(yīng)的閉環(huán)階躍響應(yīng)。

實(shí)際考慮和實(shí)驗(yàn)結(jié)果比較

利用基于Pspice的分析方法來研究合適的補(bǔ)償值,并通過仿真找到最佳響應(yīng)時(shí)的參數(shù)值后,接下來就是在實(shí)驗(yàn)臺(tái)上驗(yàn)證仿真結(jié)果。圖9為一個(gè)實(shí)驗(yàn)臺(tái)的驗(yàn)證設(shè)置示意圖。

圖9:TIA補(bǔ)償實(shí)驗(yàn)臺(tái)驗(yàn)證設(shè)置。

以下是圖9實(shí)驗(yàn)臺(tái)設(shè)置的一些要點(diǎn)。

低電容值和實(shí)驗(yàn)臺(tái)優(yōu)化:為降低有效電容值,可以將RA、RB串在一起并與CF鄰接,這樣可以用一個(gè)市場上容易找到的電容(>1pF)來獲取皮法以下的電容值,而該值很難直接獲得。只要RB << RF,該電路即可將CF的等效電容值降低1+ RB/RA倍。該方法可以得到一個(gè)0.20pF的等效電容,選用這樣的設(shè)置是因?yàn)?.25pF的仿真值會(huì)產(chǎn)生過阻尼實(shí)驗(yàn)臺(tái)響應(yīng)。物理電路板會(huì)存在一定的寄生電感和電容,它們可以被最小化,但是不能完全降低到0。因此,人們希望通過實(shí)驗(yàn)臺(tái)測試來促進(jìn)對(duì)仿真結(jié)果的優(yōu)化,特別是在處理皮法級(jí)以下的標(biāo)稱值時(shí)。等效電容為0.20pF時(shí),檢測到的帶寬為70MHz;而當(dāng)?shù)刃щ娙轂?.25pF時(shí),帶寬下降至55MHz。

等效光電二極管實(shí)驗(yàn)臺(tái)設(shè)置:為便于測試,所示的(Rin, Cin以及CD)前端配置允許使用標(biāo)準(zhǔn)的50?實(shí)驗(yàn)室設(shè)備來模擬光電二極管的性能。這里CD(假設(shè)為光電二極管電容)被設(shè)定為10pF。

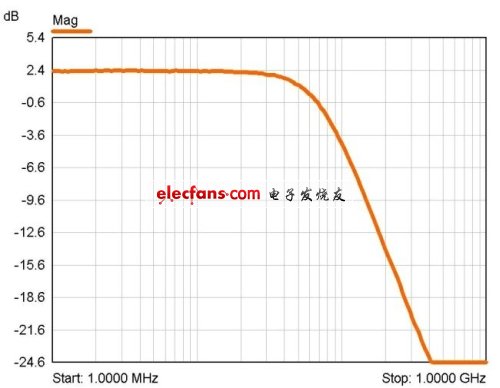

圖10:CF_eq=0.2pF時(shí)測定的頻率響應(yīng)。

圖10:CF_eq=0.2pF時(shí)測定的頻率響應(yīng)。

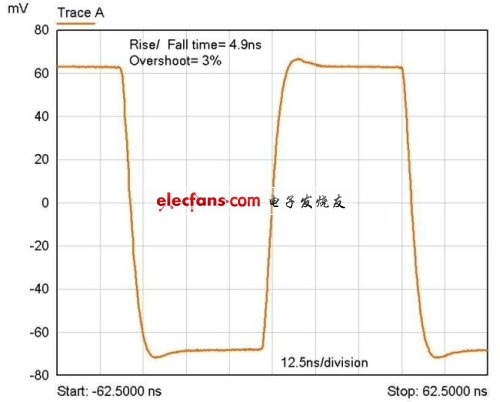

圖10和圖11分別顯示了使用50?源和輸出端負(fù)載得到的頻率響應(yīng)和階躍響應(yīng)結(jié)果。如圖所示,-3dB帶寬時(shí),頻率接近70MHz,沒有峰值。階躍響應(yīng)曲線在上升時(shí)間和下降時(shí)間與頻率響應(yīng)相匹配,圖中顯示了最小過沖值,沒有振鈴,從而可以確定電路已被正確地補(bǔ)償。為了對(duì)仿真作進(jìn)一步確認(rèn),實(shí)驗(yàn)臺(tái)測試驗(yàn)證了在沒有補(bǔ)償電容時(shí)出現(xiàn)的大峰值以及10pF電容跨接RF時(shí)所產(chǎn)生的全振蕩過程。

圖11:CF_eq=0.2pF時(shí)測定的階躍響應(yīng)。

測量結(jié)果被證實(shí)是可靠的,充分補(bǔ)償了70MHz的帶寬,符合方程式1中的理論值,該方程式中CIN為總反向輸入電容(包括二極管和運(yùn)算放大器)。

通過斷開環(huán)路,并借助Pspice的迭代函數(shù)(即階躍函數(shù)),人們就能在很短的時(shí)間內(nèi)更好地尋找最優(yōu)補(bǔ)償方法,實(shí)現(xiàn)環(huán)路的穩(wěn)定性。本文的例子充分說明了該方法的簡便和靈活性。當(dāng)然,本文所用的運(yùn)算放大器的宏模型必須對(duì)器件精確建模(包括輸入階段的寄生效應(yīng)),否則獲得的結(jié)果就有可能遠(yuǎn)遠(yuǎn)偏離實(shí)際值。這個(gè)例子所演示的技術(shù)并非僅適用于TIA電路(這只是選取出來的一個(gè)具有代表性的例子),實(shí)際上該技術(shù)也可應(yīng)用于大多數(shù)放大器電路上。