隨著數(shù)字信號處理器性能的不斷提高及其成本與售價(jià)的大幅下降,數(shù)字信號處理應(yīng)用領(lǐng)域飛速擴(kuò)展,信號處理進(jìn)入了一個(gè)新的發(fā)展時(shí)期。同時(shí)隨著計(jì)算機(jī)技術(shù)以及互聯(lián)網(wǎng)絡(luò)技術(shù)的不斷發(fā)展,越來越多的數(shù)據(jù)需要經(jīng)過計(jì)算機(jī)來進(jìn)行處理、存儲、傳輸籌操作。計(jì)算機(jī)的應(yīng)用已經(jīng)遍及我們生活的每一個(gè)角落。由于計(jì)算機(jī)本身的特點(diǎn),通用計(jì)算機(jī)通常僅負(fù)責(zé)沒有實(shí)時(shí)性要求的工作,而不適于進(jìn)行實(shí)時(shí)性要求很高的數(shù)字信號處理。將計(jì)算機(jī)和 DSP有機(jī)地結(jié)合起來,充分利用各自的優(yōu)點(diǎn),它們將會相得益彰,滿足現(xiàn)實(shí)應(yīng)用中對數(shù)據(jù)實(shí)時(shí)處理能力、數(shù)據(jù)傳輸能力以及數(shù)據(jù)管理能力提出的越來越高的要求。

PCI總線是先進(jìn)的高性能32/64位局部總線。可同時(shí)支持多組外圍設(shè)備,不受制于處理器,數(shù)據(jù)吞吐量大(32位時(shí)峰值高達(dá)132Mb/s),并能完全兼容現(xiàn)有的ISA/EISA/MAC等擴(kuò)展總線。連接到PCI總線上的設(shè)備主要分為:主控設(shè)備和目標(biāo)(從)設(shè)備兩類,接口設(shè)計(jì)成為PCI總線與設(shè)備進(jìn)行溝通的橋梁。但是PCI總線的規(guī)范十分復(fù)雜,其接口的實(shí)現(xiàn)比ISA等總線要困難得多。目前實(shí)現(xiàn)PCI接口的有效方案有兩種:使用可編程邏輯器件和使用專門接口芯片。本文中的采集系統(tǒng)就是運(yùn)用TI公司的TMS320C5410高速定點(diǎn)DSP和PLX公司的PCI9052 PCI總線接口芯片來搭建的。

1 系統(tǒng)功能概述

根據(jù)實(shí)際應(yīng)用析需要,系統(tǒng)的主要功能有:

(1)可以同時(shí)采集處理一條E1鏈路上所有32個(gè)時(shí)際的數(shù)據(jù);

(2)對數(shù)據(jù)進(jìn)行鏈路層協(xié)議解包后,重新打包茂特定的格式,交給上層系統(tǒng)(PC機(jī))保存或進(jìn)一步處理。對鏈路數(shù)據(jù)狀態(tài)和采集的統(tǒng)計(jì)信息進(jìn)行監(jiān)測,定時(shí)生成報(bào)表,交給上層系統(tǒng)實(shí)時(shí)顯示;

(3)系統(tǒng)應(yīng)具有盡量大的軟件升級功能和靈活性,便于系統(tǒng)提高性能或者應(yīng)用于其他通信業(yè)務(wù)數(shù)據(jù)的采集。

本系統(tǒng)的設(shè)計(jì)難點(diǎn)主要是如何實(shí)現(xiàn)DSP與PCI9052之間高效率的數(shù)據(jù)通信。在系統(tǒng)中PCI9052通過DSP上專門的高速主機(jī)通用接口(host port interface,以下簡稱HPI口)和DSP進(jìn)行通信。但是HPI口總線是一個(gè)非常特殊的總線,它采用訪問寄存器的方式來進(jìn)行DSP內(nèi)部數(shù)據(jù)的讀寫,HPI口單純映射到PCI的I/O空間或者存儲器空間,有不可避免的缺點(diǎn)。本文提出了一種雙映射方法,成功地解決了這一問題,實(shí)現(xiàn)了DSP與PCI9052之間方便、高速的數(shù)據(jù)通信。

2 系統(tǒng)的硬件設(shè)計(jì)

整個(gè)硬件系統(tǒng)主要由DSP、PCI總線接口芯片和鏈路數(shù)據(jù)采集芯片組成。

本系統(tǒng)采用TI公司的TMS320C5410(以下簡稱C5410)DSP,該芯片的特點(diǎn)有:

·處理能力可達(dá)到100MIPS;

·采用多總線技術(shù),一條指令可以同時(shí)訪問數(shù)據(jù)和程序空間,具有高度并行性;

·具有改進(jìn)型的8位HPI接口,主機(jī)通過HPI口可以訪問DSP系統(tǒng)的任何一個(gè)存儲器單元,而且外部訪問和DSP內(nèi)部操作相互獨(dú)立,互不干擾;

·軟件可編程的等待狀態(tài)發(fā)生器,可以靈活地用不同速度的器件組建系統(tǒng)。

數(shù)據(jù)采集芯片采用了PMC公司的PMC4351.它可以同時(shí)采集三個(gè)時(shí)隙上的數(shù)據(jù),可以通過編程選擇采集或輸出T1、E1數(shù)據(jù),支持HDLC協(xié)議,可以進(jìn)行去除CRC標(biāo)志、復(fù)幀標(biāo)志等預(yù)處理,為每小時(shí)隙提供128字節(jié)的發(fā)送FIFO和接收FIFO,有很完善的處理器接口。為了能夠同時(shí)采集一整條E1鏈路上的數(shù)據(jù),本系統(tǒng)采用了11片PMC4351組成鏈路數(shù)據(jù)接口單元。各個(gè)芯片之間的接口利用CPLD來完成,它的可編程性為各個(gè)組成部分之間的控制和通信提供了相當(dāng)大的靈活性,也省去了大量外部電路、保證了硬件的方便調(diào)試和穩(wěn)定工作。

具體的硬件框圖如圖1所示。

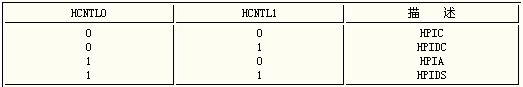

3 DSP的HPI接口與PCI9052的連接

C5410上的增強(qiáng)型8位HPI口為上層系統(tǒng)提供了一個(gè)靈活訪問DSP內(nèi)部存儲器的并行數(shù)據(jù)口。上層系統(tǒng)可以通過HPI口自由地讀寫DSP內(nèi)部存儲器中的任何一個(gè)單元。并且C5410為HPI口提供了專門的中斷線,這樣兩個(gè)系統(tǒng)可以通過中斷進(jìn)行控制信息交互。HPI為上層系統(tǒng)的訪問提供了四個(gè)端口,通過這四個(gè)端口上層系統(tǒng)可以讀寫HPI的地址寄存器(HPIA)和控制寄存器(HPIC);通過另外兩個(gè)端口HPIDC和HPIDS來分別連續(xù)和單個(gè)讀寫C5410存儲器中的數(shù)據(jù)。這四個(gè)端口由HCNTL0和HCNTL1來尋址,它們的地址分配如表1所示.

表1

本系統(tǒng)采用雙映射方式來完成C5410與PCI9052的連接。第一個(gè)映射是將HPI口的四個(gè)寄存器分別映射到PCI空間的四個(gè)16位I/O口上。上層系統(tǒng)可以通過訪問I/O端口的方式來訪問這四個(gè)寄存器,而依照HPI口的工作流程就可以間接地訪問C5410內(nèi)部存儲器。這四個(gè)寄存器和PCI9052本地I/O空間的對應(yīng)關(guān)系如下:

HPIC--100H

HPIDC--104H

HPIA--108H

HPIDS--10CH

在這種映射方式下,上層系統(tǒng)可通過PCI的I/O訪問方式直接訪問HPI口的四個(gè)寄存器,操作很直觀。由于I/O訪問無法進(jìn)行突發(fā)傳輸,從而限制了數(shù)據(jù)傳輸速度。

第二種映射方式是將HPIDC寄存器映射成PCI空間的一個(gè)長度為2000H的8位存儲器塊。上層系統(tǒng)對該地址空間內(nèi)任一單元的讀寫操作都會被映射成對HPIDC的讀寫訪問。寫入的情況也類似。可以看出,實(shí)際上這種模式形成了一個(gè)PCI存儲器空間和DSP內(nèi)部存儲空間之間一一對應(yīng)的直接映射。

本系統(tǒng)利用I/O映射來訪問控制、地址寄存器和單個(gè)數(shù)據(jù)口,并用存儲器映射來訪問連續(xù)數(shù)據(jù)口。

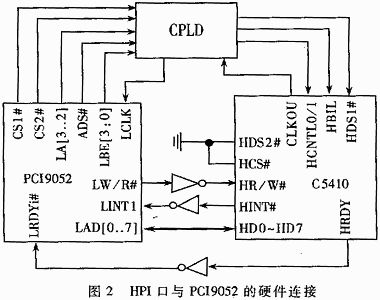

在這種配置方法下,PCI9052和HPI口之間的硬件連接,主要利用PCI9052的讀寫控制信號ADS#、LBE[30]#、LW/R#、LRDY#和部分地址信號LA[32]進(jìn)行簡單的時(shí)序和邏輯轉(zhuǎn)換后來生成HPI口的讀寫控制信號HBIL、HDS1#、HCNTL0/1、HR/W#.由于HPI口的訪問時(shí)鐘是C5410的外部頻率CLKOUT的5分頻,所以PCI9052的本地時(shí)鐘采用CLKOUT/5.

所有控制信號的接口邏輯和時(shí)序轉(zhuǎn)換都是由CPLD來完成,具體的連接方式如圖2所示。

4 系統(tǒng)的軟件設(shè)計(jì)

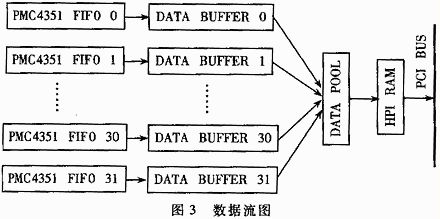

數(shù)據(jù)的采集與預(yù)處理需要在C5410數(shù)據(jù)存儲器中開辟三種存儲塊:一種是DATA BUFFER,它與PMC4351中各個(gè)時(shí)隙的FIFO一一對應(yīng),用于緩存每個(gè)時(shí)隙上采集到的消息數(shù)據(jù);第二是DATA POOL(大小為1000H字),這是一個(gè)消息數(shù)據(jù)地,消息數(shù)據(jù)在DATA BUFFER中存滿一整條消息后,加上一些TS包頭后,形成一個(gè)新的消息包,存入到DATA POOL中;另外還要再開辟一個(gè)大小為1000H字節(jié)的存儲塊HPI RAM,這樣就將DSP的數(shù)據(jù)采集部分與上層系統(tǒng)通信部分相互隔離開來,互不干擾。在DATA POOL中存滿數(shù)據(jù)后,形成一個(gè)大的數(shù)據(jù)包,交給HPI RAM,通過PCI總線交給上層系統(tǒng),進(jìn)行進(jìn)一步處理。整體的數(shù)據(jù)流圖如圖3所示。

由于DSP芯片的中斷引腳數(shù)目有限,而且中斷工作方式容易造成各個(gè)時(shí)隙數(shù)據(jù)采集不均勻的情況,本系統(tǒng)采用了輪詢的工作方式。軟件的具體流程如圖4所示。

圖4 軟件流程圖

本文提出的雙映射配置方法和DSP軟件工作策略,將C5410 DSP和PCI總線相互連接,接口具有邏輯簡單、操作方便、效率高等優(yōu)點(diǎn)。在C5410的CLOCKOUT配置成64MHz的前提下,兩者之間數(shù)據(jù)傳輸速率理論峰值可達(dá)12.8Mbps,實(shí)際系統(tǒng)實(shí)現(xiàn)的平均速率達(dá)到了10Mbps。采用高性能的采集芯片,可充分發(fā)揮HPI口與PCI9052之間的高速數(shù)據(jù)連接,同時(shí)系統(tǒng)也可以升級到同時(shí)采集10條E1鏈路。

本文實(shí)現(xiàn)的數(shù)據(jù)采集系統(tǒng)工作良好,并已經(jīng)在電信部門得到采用。該系統(tǒng)目前已經(jīng)不僅僅用于采集移動通信數(shù)據(jù),也開始應(yīng)用于采集V5、七號信號等協(xié)議的數(shù)據(jù),滿足了系統(tǒng)功能設(shè)計(jì)的要求。