摘 要: 介紹用FPGA實(shí)現(xiàn)數(shù)字通信中的交、解交織器的一種比較通用的方案,詳細(xì)說明了設(shè)計(jì)中的一些問題及解決辦法。還介紹了一種實(shí)現(xiàn)FPGA中信號延時(shí)的方法。

關(guān)鍵詞: 交織器與解交織器 FPGA技術(shù) 地址序列 最小時(shí)延 信號延時(shí)

在現(xiàn)代數(shù)字通信系統(tǒng)中,F(xiàn)PGA的應(yīng)用相當(dāng)廣泛。尤其是在對基帶信號的處理和整個(gè)系統(tǒng)的控制中,F(xiàn)PGA不但能大大縮減電路的體積,提高電路的穩(wěn)定性,而且先進(jìn)的開發(fā)工具使整個(gè)系統(tǒng)的設(shè)計(jì)調(diào)試周期大大縮短。

1 交織器與解交織器的原理

數(shù)字通信中經(jīng)常用信道編碼來提高數(shù)據(jù)傳輸?shù)目煽啃裕渲幸恍┬诺谰幋a加入了交織模塊,以進(jìn)一步提高抗干擾性能。交織器的主要作用就是將原始數(shù)據(jù)序列打亂,使得交織前后數(shù)據(jù)序列的相關(guān)性減弱,這樣做很突出的一個(gè)優(yōu)點(diǎn)便是大大降低了數(shù)據(jù)突發(fā)錯(cuò)誤的影響。在現(xiàn)代的高效編碼調(diào)制技術(shù)中,無論是級聯(lián)編碼還是Turbo編碼中都要使用交織器。

數(shù)字通信中常用的交織器按交織方式可分為分組交織器和隨機(jī)交織器兩種,按交織對象分可分為字節(jié)交織和位交織。本文所介紹的實(shí)現(xiàn)方案主要針對字節(jié)交織器。下面用一個(gè)模型來說明交織器的工作過程。設(shè)外碼RS碼字長度為n=7,交織器深度Id=4,相鄰碼字之間的交錯(cuò)字節(jié)數(shù)di=[![]() ]=Smallest Integer≥

]=Smallest Integer≥![]() =2,則交織器的功能如下圖1所示。

=2,則交織器的功能如下圖1所示。

輸入碼字按行排列,按列輸出,圖中“*”為無效數(shù)據(jù),即交織器輸出的前端有一些無效數(shù)據(jù)。

解交織器將交織器打亂的字節(jié)序列重新排列恢復(fù)原始碼字。如圖1,即將串行輸入的字節(jié)序列先按列方式讀入,再逐行將碼字讀出。從圖中可以看出,行與行的碼字間均有di字節(jié)交錯(cuò),這種斜交織方式的優(yōu)點(diǎn)可以減小系統(tǒng)時(shí)延。

2 交織器的實(shí)現(xiàn)

2.1 實(shí)現(xiàn)模型:

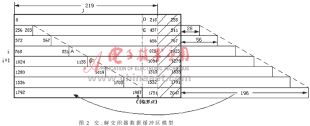

在本課題中,交織器的幾個(gè)參數(shù)分別為:n=219,Id=8,di=[![]() ]=28。圖2是實(shí)現(xiàn)交織器模型。

]=28。圖2是實(shí)現(xiàn)交織器模型。

圖中粗線內(nèi)的方塊區(qū)域?yàn)閷?shí)現(xiàn)交織器所必須的一塊數(shù)據(jù)緩沖區(qū)(存儲器),考慮到交織器的功能特性是須對此緩沖區(qū)同時(shí)讀寫,故選用雙口RAM實(shí)現(xiàn)最好,因?yàn)?024<219×8<2048,故容量用2Kbytes即可。模型中所標(biāo)識的數(shù)字是存儲器的地址,畫斜線的區(qū)域?yàn)榭臻e緩存區(qū),右邊存儲器外虛線下數(shù)據(jù)實(shí)際上是存儲在存儲器左下角的區(qū)域內(nèi)。交織器實(shí)際工作時(shí),一邊按寫地址序列向緩存區(qū)中寫入數(shù)據(jù),另一邊按讀地址序列讀出。圖2模型的寫地址序列為:0,1,2...218,284,285...437,256,257...283,568,569...656,512,513...567,852......,依次寫入每行,直到1987,下一字節(jié)再從0地址開始,循環(huán)寫入。讀地址序列為:0,256,512,768,1024...1792,1,257,513......,直到1751地址,再從0地址開始循環(huán)。

對于解交織器,讀地址序列正好是交織器的寫地址序列,寫地址序列是交織器的讀地址序列。

2.2 FPGA的選用及實(shí)現(xiàn)的原理框圖

目前主要的FPGA廠商有Xilinx、Altera、AMD、Lattice、Actel、Lucent及Atmel等。Altera公司生產(chǎn)的FLEX 10K系列的FPGA,具有規(guī)模覆蓋范圍廣、布線資源豐富、時(shí)間可預(yù)測性好的優(yōu)點(diǎn),故而在數(shù)字通信系統(tǒng)設(shè)計(jì)中得到了廣泛的應(yīng)用。此外,F(xiàn)LEX 10K系列芯片都具有EAB(Embeded Array Block),可以實(shí)現(xiàn)片內(nèi)存儲器功能,若用EAB做交織器、解交織器的數(shù)據(jù)緩存區(qū),就可以用單片F(xiàn)PGA完成交、解交織器的功能,從而大大減小電路的復(fù)雜度和體積。但實(shí)際應(yīng)用中,由于FLEX 10K芯片的片內(nèi)EAB資源有限,所以要完全實(shí)現(xiàn)交、解交織器,至少要選擇FLEX 10K130(內(nèi)部有13萬門左右的資源)以上規(guī)模的FPGA。可是實(shí)現(xiàn)交織器的時(shí)序控制邏輯并不復(fù)雜,大概需要一萬門左右的資源就夠了,再加上系統(tǒng)其它功能塊也不過幾萬門,若使用10K130芯片就會造成資源浪費(fèi),而且成本過高。綜合考慮,決定用外部雙口RAM(IDT 7132)當(dāng)作數(shù)據(jù)緩沖區(qū),F(xiàn)PGA選用FLEX 10K20芯片。

圖3即為用FPGA實(shí)現(xiàn)交織器的原理框圖,F(xiàn)PGA的內(nèi)部可由讀、寫地址序列發(fā)生器和時(shí)序控制器三部分組成。時(shí)序控制器主要產(chǎn)生雙口RAM讀寫控制信號,并決定讀、寫地址序列發(fā)生器何時(shí)啟動工作。因?yàn)榻饨豢椘鲀H是數(shù)據(jù)進(jìn)出雙口RAM的順序不同,故上原理圖中只須變換讀、寫地址序列發(fā)生器便可構(gòu)成解交織器。

3 實(shí)現(xiàn)中的若干問題

3.1 讀寫地址的產(chǎn)生問題

最一般的方案為查找表的方法。令輸入數(shù)據(jù)順序存入雙口RAM,即寫地址序列變?yōu)椋?,1,2,3...1750,1751,0......,對照模型找出對應(yīng)的讀地址序列。這樣重新編址的好處是使寫地址序列易于產(chǎn)生,可以由FPGA直接生成。將讀地址序列做成表順序存入E2PROM(或其它只讀存儲器,如Flash),需要讀雙口RAM時(shí),F(xiàn)PGA產(chǎn)生0,1,2...1751順序序列作地址送給E2PROM,映射出的數(shù)據(jù)送給雙口RAM作讀地址。這種查找表的方法具有很好的通用性,可以適用于各類字節(jié)交織器,但缺點(diǎn)是須額外附加存儲器,而且E2PROM的讀取速度一般較慢,在數(shù)據(jù)傳輸速率較高的情況下不適用。

本課題中的交織器在圖2所示的模型和編址方法下,讀、寫地址序列具有較強(qiáng)的規(guī)律性,可以用在FPGA中構(gòu)造計(jì)數(shù)器的方式來直接產(chǎn)生。下面介紹一下地址序列的產(chǎn)生方法。將11位地址分成兩部分:高3位和底8位,在物理實(shí)現(xiàn)上構(gòu)造3位和8位計(jì)數(shù)器各一個(gè),然后級聯(lián)起來。對于交織器的讀地址序列,具體實(shí)現(xiàn)時(shí),用數(shù)據(jù)輸入時(shí)鐘DataInClk驅(qū)動3位計(jì)數(shù)器計(jì)數(shù),3位計(jì)數(shù)器記滿同步清0時(shí)產(chǎn)生脈沖驅(qū)動8位計(jì)數(shù)器計(jì)數(shù),8位計(jì)數(shù)器計(jì)到218后同步清0。交織器的寫地址序列產(chǎn)生稍復(fù)雜,但同樣可用兩計(jì)數(shù)器的級聯(lián)產(chǎn)生。

3.2 交織、解交織器的最小時(shí)延問題

無論是交織器還是解交織器,數(shù)據(jù)緩沖區(qū)的讀相對于寫必須有一個(gè)延時(shí),這個(gè)延時(shí)即為交織器和解交織器的時(shí)延。為了盡量減小系統(tǒng)的時(shí)延,應(yīng)使交織器和解交織器的時(shí)延降至最小。

首先分析交織器,設(shè)數(shù)據(jù)周期為T,則每個(gè)緩沖區(qū)單元的讀或?qū)懙刂返谋3謺r(shí)間也為T。考察圖2模型中從第i行的交錯(cuò)后的第一個(gè)元素A到第i+1行的元素B所用的時(shí)間,若按寫操作進(jìn)行需219×T,按讀操作進(jìn)行需(28×8+1)T=225T>219T。這表明若讀、寫同時(shí)從0地址開始,則緩沖區(qū)那的每個(gè)存儲單元的寫操作都在讀操作之前,從而保證每個(gè)讀出的數(shù)據(jù)都有效。這里對于交錯(cuò)所產(chǎn)生的左下角區(qū)域元素,交織器開始工作時(shí)讀出的都是無效數(shù)據(jù),但在循環(huán)往復(fù)的連續(xù)數(shù)據(jù)讀寫中,讀出的則是上一頁所寫碼字的部分字節(jié),是有效數(shù)據(jù)。故在交織器中,讀、寫緩沖區(qū)可以同時(shí)開始,考慮到雙口RAM對同一單元不能同時(shí)讀寫,所以設(shè)計(jì)時(shí)令讀滯后于寫一個(gè)數(shù)據(jù)周期T,這樣交織器的最小時(shí)延為T。

解交織器的分析方法類似。由模型二可推算出,當(dāng)系統(tǒng)寫雙口RAM的E單元時(shí),讀從0地址單元開始,故解交織器的最小時(shí)延為:(28×7×8+1)T= 1569T。

3.3 FPGA中延時(shí)功能的實(shí)現(xiàn)

在FPGA的開發(fā)設(shè)計(jì)中,經(jīng)常需要用到延時(shí)模塊。如本設(shè)計(jì)中,實(shí)現(xiàn)雙口RAM的讀寫時(shí)序時(shí)就需要。以IDT 7132的讀時(shí)序?yàn)槔瑫r(shí)序圖如圖4所示。

無論用 還是

還是 來控制讀取,都需要

來控制讀取,都需要 或

或 保持一段低電平。令

保持一段低電平。令 保持低電平,

保持低電平, 平時(shí)為高電平,讀雙口RAM時(shí)觸發(fā)CE變?yōu)榈碗娖剑舆t一小段時(shí)間再恢復(fù)高電平。本設(shè)計(jì)產(chǎn)生這段延時(shí)的方法是用高頻計(jì)數(shù)器產(chǎn)生,具體方法為:在FPGA中設(shè)計(jì)一個(gè)計(jì)數(shù)器,取系統(tǒng)可用的高頻時(shí)鐘(周期小于所需延時(shí))驅(qū)動它計(jì)數(shù),計(jì)到設(shè)定好的終值時(shí)產(chǎn)生觸發(fā)脈沖。不同的計(jì)數(shù)終值可以產(chǎn)生不同的延時(shí)。此方法所產(chǎn)生的延時(shí)為高頻時(shí)鐘周期的整數(shù)倍,若高頻時(shí)鐘周期與所需延時(shí)相比很小,則延時(shí)較精確,否則只能做一粗略的延時(shí)。

平時(shí)為高電平,讀雙口RAM時(shí)觸發(fā)CE變?yōu)榈碗娖剑舆t一小段時(shí)間再恢復(fù)高電平。本設(shè)計(jì)產(chǎn)生這段延時(shí)的方法是用高頻計(jì)數(shù)器產(chǎn)生,具體方法為:在FPGA中設(shè)計(jì)一個(gè)計(jì)數(shù)器,取系統(tǒng)可用的高頻時(shí)鐘(周期小于所需延時(shí))驅(qū)動它計(jì)數(shù),計(jì)到設(shè)定好的終值時(shí)產(chǎn)生觸發(fā)脈沖。不同的計(jì)數(shù)終值可以產(chǎn)生不同的延時(shí)。此方法所產(chǎn)生的延時(shí)為高頻時(shí)鐘周期的整數(shù)倍,若高頻時(shí)鐘周期與所需延時(shí)相比很小,則延時(shí)較精確,否則只能做一粗略的延時(shí)。

當(dāng)需要對某一信號作一段延時(shí)時(shí),初學(xué)者往往在此信號后串接一些非門或其它門電路,此方法在分離電路中是可行的。但在FPGA中,開發(fā)軟件在綜合設(shè)計(jì)時(shí)會將這些門當(dāng)作冗余邏輯去掉,達(dá)不到延時(shí)的效果。用Altera公司的Maxplus II開發(fā)FPGA時(shí),可以通過插入一些LCELL原語來產(chǎn)生一定的延時(shí),但這樣形成的延時(shí)在FPGA芯片中并不穩(wěn)定,會隨溫度等外部環(huán)境的改變而改變,因此Altera并不提倡這樣做。在此,沿用上一段中的思想,可以用高頻時(shí)鐘來驅(qū)動一移位寄存器,待延時(shí)信號作數(shù)據(jù)輸入,按所需延時(shí)正確設(shè)置移位寄存器的級數(shù),移位寄存器的輸出即為延時(shí)后的信號。此方法產(chǎn)生的延時(shí)信號與原信號比有誤差,誤差大小由高頻時(shí)鐘的周期來決定。對于數(shù)據(jù)信號的延時(shí),在輸出端用數(shù)據(jù)時(shí)鐘對延時(shí)后信號重新采樣,就可以消除誤差。

總之,本文著重介紹了用FPGA實(shí)現(xiàn)數(shù)字通信中的交、解交織器的一種比較通用的方案。其它種類的交織器,只需更換讀、寫地址產(chǎn)生模塊,確定讀、寫時(shí)差即可完成。除了隨機(jī)交織器須用查找表的方式產(chǎn)生讀地址序列外,大部分的交織器讀、寫地址都可用本文介紹的類似方法實(shí)現(xiàn),這樣既節(jié)省芯片,縮小電路體積,速度又快,調(diào)試也大大簡化。文中還介紹了一種實(shí)現(xiàn)FPGA中信號粗略延時(shí)的方法以供大家參考。

參考文獻(xiàn)

1 Intelsat Earth Station Standards (IESS) Documents IESS-310 (Rev.B),May 1997

2 王小軍編著.VHDL簡明教程.北京:清華大學(xué)出版社,1997

3 Leonardo HDL Synthesis Guide,Exemplar Logic

4 馬群生,李健航編譯.MAX Plus II 入門.清華大學(xué)Altera培訓(xùn)中心,1996.4