摘 要: 介紹大規(guī)模、高速度的FPGA在小型漁用聲納系統(tǒng)設(shè)計中的應(yīng)用。在該系統(tǒng)設(shè)計中,采用了Xilinx公司的FPGA芯片XCS40作為主要器件,基本上將整個系統(tǒng)的功能集成在了一片芯片上。實踐證明,即降低了成本,又縮短了設(shè)計和調(diào)試的時間。

關(guān)鍵詞: 聲納 FPGA 片上系統(tǒng)

從傳統(tǒng)意義上來說,F(xiàn)PGA等通用可編程器件往往被應(yīng)用于速率較低的DSP設(shè)計中,而在高速的DSP應(yīng)用中,則往往使用專用的DSP芯片及集成電路進行設(shè)計。這樣做雖然滿足了對速度的要求,但是開發(fā)周期較長,產(chǎn)品的調(diào)試修改升級比較困難,而且靈活性較差。

隨著工藝水平的提高,F(xiàn)PGA等可編程器件的速度和規(guī)模都有了很大的提高,而且它還具有集成度高、體積小、功耗低、設(shè)計靈活等優(yōu)勢,這樣就為利用可編程器件實現(xiàn)高速DSP處理開辟了道路。目前新一代的FPGA等可編程器件,不僅在速度上能滿足DSP的要求,而且可編程資源也大大增加,在系統(tǒng)級集成方面也能滿足需要,從而提高了系統(tǒng)的靈活性和適應(yīng)性。因此,在開發(fā)周期較短或?qū)ο到y(tǒng)靈活性要求較高的場所,F(xiàn)PGA能夠提供比專用DSP器件更高的系統(tǒng)速度和更好的解決方案。

我們在設(shè)計小型聲納的過程中,根據(jù)系統(tǒng)的要求,采用了Xilinx公司的Spartan XCS40芯片。

1 器件介紹

Spartan系列的XCS40是Xilinx公司推出的低價格、高性能的現(xiàn)場可編程門陣列。它的主要特點是:

·系統(tǒng)門的數(shù)目達到了40000,Logic Cell數(shù)目達1862,系統(tǒng)資源豐富

·具備片上可配置分布式RAM, 最多配置的RAM比特數(shù)達25088位

·分布式算術(shù)邏輯單元,支持分布式DSP運算

·支持Alliance Core及系統(tǒng)集成

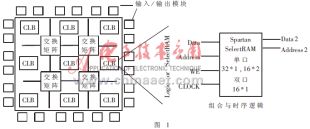

其片內(nèi)結(jié)構(gòu)如圖1所示。

2 由XCS40構(gòu)成的聲納系統(tǒng)的原理

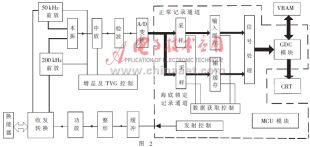

以XCS40為主體構(gòu)成的漁用聲納的基本功能框圖如圖2所示。其中,虛線內(nèi)的功能模塊全部集中在XCS40芯片內(nèi)。

小型漁用聲納系統(tǒng)的基本工作原理是根據(jù)從水下反射的聲波回波信號,顯示水下魚群和海底的深度情況。這種小型的聲波探測系統(tǒng)在漁業(yè)生產(chǎn)和航海安全上起著很重要的作用,在小型船舶上使用相當(dāng)普遍。整個系統(tǒng)分為模擬和數(shù)字兩大部分。

模擬部分根據(jù)環(huán)境噪聲和量程的要求,50kHz或200kHz載頻的鍵控脈沖經(jīng)過緩沖、整形、推動和推挽功放之后,調(diào)制信號送到聲波換能器,發(fā)射到水中。接收電路為一外差接收機。不同頻率的反射信號經(jīng)過前放后,與本機的晶振混頻,產(chǎn)生455kHz的中頻信號, 經(jīng)過兩級中放和檢波后,由A/D變換器形成3比特的數(shù)字信號,送到聲納的數(shù)字處理部分。收發(fā)轉(zhuǎn)換模塊控制著收發(fā)信號的隔離,避免它們之間的串?dāng)_,尤其要避免發(fā)射信號串入接收機端而引起接收機性能的大幅度下降。同時,通過時變增益控制(TVG)等手段, 使得輸入信號的動態(tài)范圍得到了壓縮,增大了接收機的工作范圍,也使得整個模擬部分的抗干擾性和信噪比得到了提高。

整個聲納系統(tǒng)的數(shù)字部分集中在一片XCS40芯片中。經(jīng)A/D變換后的數(shù)據(jù), 在數(shù)據(jù)獲取控制單元的協(xié)調(diào)下,通過正常記錄和海底鎖定記錄兩個通道分別進入輸入存儲器。輸入存儲器中的回波數(shù)據(jù), 經(jīng)過相關(guān)處理、雜波消除、強度變換和坐標(biāo)變換等一系列信號處理后,在FPGA中內(nèi)置的顯示控制模塊的管理下寫入VRAM。與此同時, 顯示控制模塊產(chǎn)生行場同步信號,并把不同強度的回波信號轉(zhuǎn)換成偽彩色信號, 驅(qū)動相應(yīng)的R、G、B輸出,將VRAM中的數(shù)據(jù)最終顯示在監(jiān)視器上。整個數(shù)字系統(tǒng)的運行也由FPGA內(nèi)置的MCU模塊來控制, 提高了系統(tǒng)的集成度。

3 分布式計算與內(nèi)置RAM

由于FPGA基于SRAM的特性,特別適合乘法和累加等DSP算法,也可以用其實現(xiàn)廣泛的數(shù)學(xué)函數(shù)運算。在設(shè)計上也可以采用并行結(jié)構(gòu)和分布式算法,使得資源達到最優(yōu)的配置。在該聲納的設(shè)計中, 使用了相關(guān)濾波器來除去鄰頻干擾、 雜波以及噪聲。并利用分布式計算,大大提高了信號處理效率。對于二進制系統(tǒng),一個線性時不變的網(wǎng)絡(luò)的響應(yīng)可以用下面的公式來表示:

可見, 上面的公式可以用加法器和分布式算術(shù)查找表來實現(xiàn)。對于所采用的相關(guān)濾波器, 可以用下面的比較簡單的方法來實現(xiàn):

這樣,當(dāng)進行異或運算時,對每次回波256點且每點3比特的數(shù)據(jù),可直接對每一位進行相關(guān)處理, 只用一個時鐘周期即可完成運算。由于充分利用了FPGA內(nèi)部的分布式功能模塊和并行計算的優(yōu)點, 使得信號處理的速度得到了很大的提高。

為了實現(xiàn)在片內(nèi)完成DSP的功能, 除了必要的算術(shù)和邏輯功能模塊之外,必須具備一定數(shù)目的片內(nèi)存儲器。設(shè)計中所應(yīng)用的Spartan XCS40就具備了分布式的片內(nèi)RAM。由于Xilinx FPGA的主要功能模塊都是基于SRAM查找表結(jié)構(gòu)的,因此分布式RAM的結(jié)構(gòu)可以在FPGA內(nèi)的任何一處實現(xiàn)。這也是分布式RAM名稱的由來。除去CLB、IO模塊和布線模塊外,分布式片內(nèi)RAM已經(jīng)成為了又一種片內(nèi)資源。由于分布式片內(nèi)RAM沒有管腿和驅(qū)動,它可以達到相當(dāng)快的讀寫操作速度。在我們的設(shè)計中,分布式RAM被用作數(shù)據(jù)的輸入緩存及數(shù)據(jù)寄存器。在片內(nèi),這些RAM被配置在數(shù)字信號處理部分的附近,從而減少了數(shù)據(jù)傳輸?shù)难訒r。

4 集成的顯示控制和MCU模塊

在帶有顯示子系統(tǒng)的設(shè)計中,一般都會用圖形控制芯片(GDC)來實現(xiàn)圖形顯示和控制。圖形控制芯片負(fù)責(zé)產(chǎn)生行場同步信號,輸出像素點信號,控制字符圖形和直線、圓等基本元素的輸出,讀寫VRAM并控制VRAM的刷新。它是顯示子系統(tǒng)的核心。我們在設(shè)計中最初采用的是NEC公司的UPD72020。但是在調(diào)試中發(fā)現(xiàn),由于該顯示控制芯片的主頻與系統(tǒng)的主頻不一樣,導(dǎo)致它與FPGA的時序無法配合。

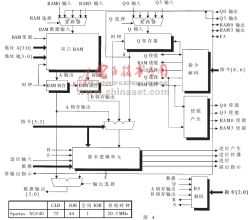

為了解決這個問題,我們在設(shè)計中把圖形控制芯片的功能集成到了FPGA中,形成一個功能比較完備的CORE。圖形控制部分的結(jié)構(gòu)簡圖如圖3所示。圖形控制部分的主要作用,是根據(jù)系統(tǒng)的要求,產(chǎn)生正確的行場時鐘脈沖,從而正確地控制像素點的輸出。系統(tǒng)的主時鐘頻率是40MHz,圖形控制部分把系統(tǒng)的主時鐘進行分頻,產(chǎn)生出18.75kHz和50Hz的行同步信號和場同步信號,加到監(jiān)視器的接口,驅(qū)動正確的顯示。同時,根據(jù)系統(tǒng)的要求,圖形控制模塊向VRAM中寫入新的數(shù)據(jù),并且周期性地讀出VRAM中的數(shù)據(jù)進行顯示和對VRAM進行刷新。本設(shè)計中采用的顯示器是偽彩色顯示器,不同的彩色信號對應(yīng)于不同的回波強度。為了實現(xiàn)這個功能,我們在FPGA中的圖形控制模塊中建立了一個彩色矩陣(Color Matrix)。對應(yīng)于不同強度的像素點數(shù)據(jù),該矩陣可以將其轉(zhuǎn)化成為相應(yīng)輸出比例的R、G、B信號,從而實現(xiàn)強度到彩色的轉(zhuǎn)換。

為了進一步提高系統(tǒng)的集成度,我們采用了CAST公司為Xilinx的FPGA所設(shè)計的C2901微處理器核來讀取鍵盤輸入, 控制整個系統(tǒng)的運行。該微處理器核的資源使用狀況和內(nèi)部結(jié)構(gòu)框圖如圖4所示。

由于采用高度集成的片上設(shè)計方法, 該聲納信號處理板的體積大大縮小, 整個系統(tǒng)僅由模擬電路、 XCS40及存儲器構(gòu)成, 設(shè)計和調(diào)試都非常簡便, 整機工作性能也十分穩(wěn)定。

參考文獻

1 The Programmable Logic Data Book.Xilinx, 1999

2 駱大為.水聲助漁儀器設(shè)備.北京:中國農(nóng)業(yè)出版社,1996

3 孟憲元.可編程專用集成電路的原理、設(shè)計和應(yīng)用.北京:電子工業(yè)出版社,1995

4 LIANG Jian.FPGA Application of Marine Navigation System for DSP.Proceedings of the Fourth International Conference on Signal Processing.Beijing:Publishing House of Electronics Industry,1998:93~96