摘要:隨著嵌入式技術(shù)的發(fā)展,嵌入式系統(tǒng)對系統(tǒng)穩(wěn)定性、可靠性、抗干擾性等要求逐漸增高。在此詳細(xì)分析嵌入式系統(tǒng)EMC產(chǎn)生的原因和途徑,在不增加CPU額外開銷情況下,采用了意法半導(dǎo)體公司硬件看門狗集成電路STWD100,提高了系統(tǒng)可靠性和穩(wěn)定性,并給出了STDW100與CPU應(yīng)用原理圖。實驗證明,采用STDW100硬件看門狗使嵌入式系統(tǒng)具有很強的抗EMC能力,在實際應(yīng)用中使系統(tǒng)具有相當(dāng)高的可靠性和穩(wěn)定性。

關(guān)鍵詞:嵌入式系統(tǒng);EMC;可靠性;看門狗;STDW100

1 EMC的特點

嵌入式系統(tǒng)EMC(Electro Magnetic Compatibility)即嵌入式系統(tǒng)電磁兼容性,指嵌入式系統(tǒng)在復(fù)雜電磁環(huán)境中抵抗其他系統(tǒng)所產(chǎn)生的電磁干擾同時本身產(chǎn)生的電磁干擾又不影響其他系統(tǒng)正常工作。EMC包括EMI(Electro Magnetic interference)和EMS(Electro Magnetic Susceptibility)分別表示嵌入式系統(tǒng)本身產(chǎn)生電磁干擾和嵌入式系統(tǒng)抗電磁干擾的能力。一般要求盡量減小系統(tǒng)工作時本身產(chǎn)生的電磁干擾,加強系統(tǒng)抵抗電磁干擾的能力。例如高頻諧波干擾,這是目前嵌入式系統(tǒng)工作不定的最大潛在因素。怎樣減小嵌入式系統(tǒng)干擾增強其抗干擾性能,盡可能地提高嵌入式系統(tǒng)工作的穩(wěn)定性和可靠性成為電子工程師們的一大技術(shù)難題。

2 嵌入式系統(tǒng)EMC的產(chǎn)生

嵌入式系統(tǒng)產(chǎn)生電磁干擾的大小和抗電磁干擾的能力同系統(tǒng)本身功能有很大關(guān)系,不同嵌入式系統(tǒng)產(chǎn)生的電磁干擾不同抗電磁干擾能力也不同。

2.1 高次諧波干擾

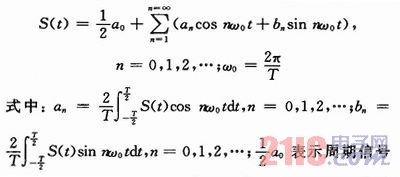

根據(jù)Fourier series任何一個周期信號S(t)并非單一波形,都由直流分量、基波和各次諧波組成,諧波頻率十分豐富,周期信號S(t)可以用式(1)表示:

直流成分,當(dāng)n=1時表示信號基波,n=2,3,4,…表示信號2,3,4,…各次諧波,其中基波是該信號主要組成成份,很多時候信號的特性呈現(xiàn)為基波特性。例如在電源系統(tǒng)中交流信號為S(t)=380sin 2π50t表示市電信號存在n=1的基波,信號在基波附近諧波頻率不斷增加、幅度迅速衰減,從理論上說正弦和余弦信號頻譜只存在一點沖擊信號。正弦信號本身所產(chǎn)生的諧波較小而其他電磁干擾參雜在正弦信號中造成系統(tǒng)諧波很大。系統(tǒng)對信號的基波要加以利用,對信號的諧波要加以抑制、濾除。正弦信號本身對外來干擾信號的抑制能力較差容易出現(xiàn)EMC,嚴(yán)重干擾系統(tǒng)工作,影響系統(tǒng)穩(wěn)定性。

2.2 嵌入式系統(tǒng)主頻過高,引起干擾

隨著電子技術(shù)的發(fā)展,CPU處理速度越來越快,數(shù)據(jù)吞吐量越來越大,主頻越來越高。8位51單片機系統(tǒng)主頻為12 MHz,16位凌陽單片機系統(tǒng)主頻為50 MHz,Altera公司Cyclone系列FPGA芯片系統(tǒng)主頻可達200 MHz,以Inter PAX255,PAX270,PAX310為核心的嵌入式系統(tǒng)主頻可達820 MHz,CPU主頻過高信號變化速率過快,信號![]() 幅度大的地方容易引起干擾。根據(jù)Fourier Series和Euler Formula,方波信號頻譜為Sine信號,Sine信號為連續(xù)信號其本身諧波很大,容易造成系統(tǒng)工作不穩(wěn)定。

幅度大的地方容易引起干擾。根據(jù)Fourier Series和Euler Formula,方波信號頻譜為Sine信號,Sine信號為連續(xù)信號其本身諧波很大,容易造成系統(tǒng)工作不穩(wěn)定。

2.3 系統(tǒng)中大功率、大電流用電器動作產(chǎn)生火花引起干擾

系統(tǒng)中含有大功率、大電流繼電器或交流接觸器,驅(qū)動電流或電壓過大使諧波幅度大,容易產(chǎn)生較強的電磁干擾;在復(fù)雜電磁環(huán)境中電機頻繁啟動與大電流有觸點開關(guān)的打火現(xiàn)象都會引起很強的電磁干擾,在要求較高的系統(tǒng)中必須解決,否則會引起系統(tǒng)工作不穩(wěn)定、可靠性差。

2.4 微弱模擬信號的提取與高精度數(shù)據(jù)采集放大

隨數(shù)字信號高速發(fā)展,很多模擬信號要轉(zhuǎn)變成數(shù)字信號進行處理,CPU處理完成后又要將數(shù)字信號還原成模擬信號,涉及微弱模擬信號的提取和采集放大電路。對于微弱模擬信號的提取通常采用傳感器,傳感器提取的模擬信號非常微弱如果受到外來干擾或系統(tǒng)本身干擾,會造成系統(tǒng)數(shù)據(jù)采集和處理有誤精度不高、系統(tǒng)工作不穩(wěn)定。

2.5 電子元器件和電路板本身所產(chǎn)生的寄生干擾

每個電子元器件都有不同的截止頻率,元器件在不同的頻率下會呈現(xiàn)不同的特性。如果信號衰減和信號畸變過大會造成整個系統(tǒng)穩(wěn)定度受影響甚至系統(tǒng)“死機”或“程序跑飛”。信號頻率過高電容的分布電感,電感的分布電容,電阻對高頻信號的反射,引線的分布電容和分布電感影響系統(tǒng)穩(wěn)定性,當(dāng)引線長度大于噪聲頻率相應(yīng)波長的1/20時,就產(chǎn)生天線效應(yīng),噪聲通過引線向外發(fā)射。

3 嵌入式系統(tǒng)硬件抗EMC技術(shù)

嵌入式系統(tǒng)工作不穩(wěn)定、不可靠因素有很多,干擾可以來自系統(tǒng)本身也可以來自本系統(tǒng)外其他系統(tǒng),關(guān)于系統(tǒng)干擾靠軟件處理能起一定作用,但僅靠軟件沒有硬件的局面難以支撐,系統(tǒng)抗干擾問題始終難以解決。在可編程系統(tǒng)中為了增加系統(tǒng)穩(wěn)定性和可靠性,減小系統(tǒng)CPU開支,常用以下方法:

3.1 抑制電源諧波干擾

在可編程電子系統(tǒng)中,能夠解決好電源干擾問題就解決整個系統(tǒng)干擾的一大半,很多干擾都是從電源中出來,電源干擾過大會造成系統(tǒng)不穩(wěn)定。單純正弦信號不會有干擾,關(guān)鍵正弦信號處于干擾很大的環(huán)境中,這時正弦信號就會附加干擾。例如:電源線過長在電源線上就會產(chǎn)生寄生干擾,可以在電源線上加上小磁珠或磁環(huán)濾波,要求不高的情況下可以加100 Ω電阻對干擾信號進行衰減,使干擾信號對系統(tǒng)不起作用。對開關(guān)電源來說,主要是振蕩器振蕩頻率過高引起諧波,不僅影響電源而且會影響整個系統(tǒng),開關(guān)電源效率較高很多地方都采用,但在要求比較高的系統(tǒng)中仍然采用線性電源。

3.2 CPU選擇能夠滿足系統(tǒng)要求的最低主頻

CPU主頻過高系統(tǒng)時鐘加快,系統(tǒng)時鐘產(chǎn)生的方波頻率升高,由方波帶來的諧波隨之增加。從Fourier Series和Euler Formula得單一方波比正弦波的諧波幅度大得多,諧波頻率復(fù)雜得多,由此系統(tǒng)主頻越高產(chǎn)生的諧波越復(fù)雜,影響系統(tǒng)工作的穩(wěn)定性。但隨著電子技術(shù)的發(fā)展,CPU主頻越來越高,電子系統(tǒng)越來越復(fù)雜,功能不斷增加,集成度不斷提高,但對于CPU來說無論哪方面使用,系統(tǒng)主頻夠用即可。

3.3 減小信號在傳輸過程中的衰減、畸變和反射

現(xiàn)代集成電路制造主要采用CMOS技術(shù),輸入阻抗大、輸出阻抗小,抗干擾能力強,適合小信號放大。CMOS集成電路輸入電流大約為1 mA,信號在電路板上延時Td與電路板引線阻抗有關(guān),阻抗越大信號衰減越大、信號延時越長、系統(tǒng)發(fā)熱越大,系統(tǒng)穩(wěn)定性越差。在高速系統(tǒng)設(shè)計過程中要考慮PCB信號傳輸延時Td,使信號人為延時Tr大于信號傳輸延時。

3.4 注意PCB布線和元器件高頻特性

PCB布線最大原則是元器件之間引線盡量短、信號線交叉盡量少,盡量不用或少用過孔。模擬地、數(shù)字地、高頻地分開走線,然后匯聚成一點,大功率器件、小功率器件和干擾信號特別大的器件在布局時要分開。對干擾信號特別敏感的高頻元器件可以用金屬罩屏蔽起來,避免電磁干擾。

3.5 退耦電容的使用

一般在系統(tǒng)集成電路供電引腳旁都要放置去耦陶瓷電容到地,濾除電源在傳輸過程中所產(chǎn)生的寄生干擾。去耦電容選取并不嚴(yán)格,一般來說都是可按f=1/C來選取,對于CPU控制系統(tǒng)來說濾除10~100 MHz電源信號寄生干擾,電容取0.01~0.1μF陶瓷電容,系統(tǒng)要求較高的高速電路中可以在集成電路電源端到地用一個1~10μF的電解電容,濾除電源1~10GHz的諧波干擾。

4 嵌入式系統(tǒng)軟件抗EMC技術(shù)

為了增強嵌入式系統(tǒng)工作的穩(wěn)定性和可靠性,嵌入式系統(tǒng)除硬件抗干擾外,可以在軟件上采用一定的技巧抗干擾,使系統(tǒng)工作更加穩(wěn)定可靠。

4.1 信息冗余技術(shù)

為了防止干擾,系統(tǒng)對重要數(shù)據(jù)或文件復(fù)制到多個存儲單元,當(dāng)一個存儲單元數(shù)據(jù)損壞后立即啟動備用存儲單元使數(shù)據(jù)恢復(fù)。

4.2 時間冗余技術(shù)

為了增強系統(tǒng)可靠性,對于重要區(qū)域重復(fù)執(zhí)行,將第1次與第2次的執(zhí)行結(jié)果相比較如相同則認(rèn)為正確,如不同第1次或第2次執(zhí)行有問題或兩次都有問題,程序再執(zhí)行第3次、第4次,如果有1次相同則認(rèn)為正確。

4.3 自動檢測與診斷技術(shù)

自動檢測包括嵌入式系統(tǒng)RAM的檢測、ROM的檢測、標(biāo)志位的檢測等,對RAM的檢測在開機時可以在RAM存儲區(qū)內(nèi)開辟幾個單元,向RAM存儲單元寫入不同的數(shù)值例如55H、AAH、EEH等,在執(zhí)行程序時讀出這些存儲單元的值是否開機放置的數(shù)值相等,判斷程序執(zhí)行的正確性。ROM用來放程序或表格數(shù)值,對ROM區(qū)域二進制數(shù)0和1的個數(shù)檢測系統(tǒng)程序執(zhí)行的正確性。在程序的執(zhí)行過程中RAM區(qū)域數(shù)據(jù)結(jié)果不同,對標(biāo)志位產(chǎn)生影響不同,例如51單片機中PSW,當(dāng)兩個數(shù)據(jù)相加出現(xiàn)進位時PSW中第位7位CY由硬件置,用戶可以查詢PSW中第7位判斷程序執(zhí)行的正確性。

4.4 軟件陷阱技術(shù)

軟件陷阱技術(shù)指嵌入式系統(tǒng)中程序存儲器不一定用完,如因干擾嵌入式系統(tǒng)程序計數(shù)器PC值錯誤,程序?qū)經(jīng)]用到的存儲空間,導(dǎo)致系統(tǒng)出錯或程序跑飛,軟件陷阱就是在這些沒有用到的程序存儲器中放入空指令和無條件跳轉(zhuǎn)指令,當(dāng)程序跑飛跑到空程序存儲器中,嵌入式系統(tǒng)則認(rèn)為系統(tǒng)受到干擾程序執(zhí)行出錯,系統(tǒng)自動復(fù)位。

5 集成STFWD100xP WTD的應(yīng)用

5.1 看門狗WTD的分類和特點

看門狗可分為硬件看門狗和軟件看門狗,軟件看門狗不需要外接硬件電路,但軟件定時器會耗費系統(tǒng)CPU資源,軟件過長還可能引起系統(tǒng)不穩(wěn)定導(dǎo)致系統(tǒng)癱瘓;硬件看門狗幾乎不耗費系統(tǒng)資源使用隨意性較大,硬件看門狗主要是為防止程序在執(zhí)行過程中受到干擾致使程序跑飛的一種監(jiān)控芯片,常用WTD集成電路有Xicor公司X25045,Dallas公司DSl232和意法半導(dǎo)體公司STWD100等,有的嵌入式CPU本身自帶WTD,如PIC系列和51S系列單片機。硬件看門狗實際就是一個Timer,未等到定時器溢出時程序不斷給定時器賦值,程序正常執(zhí)行情況下定時器不會溢出,當(dāng)程序跑飛沒有正常為WTD賦值定時器會溢出,系統(tǒng)自動復(fù)位。看門狗就是在程序正常執(zhí)行處放一條或幾條喂狗指令,使看門狗處于喂飽狀態(tài),如程序跑飛長時間沒有喂狗,看門狗就會叫使嵌入式系統(tǒng)重啟或復(fù)位。

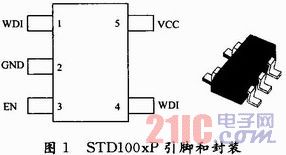

STWD100是意法半導(dǎo)體公司新推出的一款操作簡單、SOT23-5小型封裝、超低功耗、超小體積5腳WTD集成電路,靜態(tài)電流13μA、輸出電流20 mA、輸出功耗320 mW。STWD100系列與X25045不同,STWD100省去繁瑣的命令,例如X25045讀、寫鎖存器,讀寫狀態(tài)寄存器;STWD100系列芯片不同喂狗周期不同,每種芯片只有一個固定的定時周期,例如STWD100xP,STWD100xW,STWD100xX,STWD100xY喂狗周期分別為3.4 ms,6.3 ms,102 ms,1.6 s。STD100xP引腳和封裝如圖1所示。

圖1中1腳WD0:看門狗溢出后輸出,漏級開路門使用時須接上拉電阻;2腳GND:接地;3腳EN:集成電路使能信號,低電平有效最低保持時間1μs;4腳WDI:時鐘信號輸入端(0.2~0.8)Vcc,上升沿定時器置數(shù)并啟動;5腳Vcc:電源,2.7~5.5V。

5.2 STWD100的硬件設(shè)計

5.2.1 STWD100與51嵌入式系統(tǒng)連接原理圖

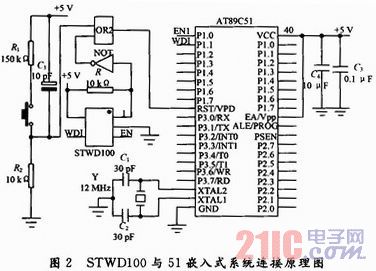

STWD100同51單片機系統(tǒng)連接如圖2所示。

該系統(tǒng)中嵌入式系統(tǒng)復(fù)位信號共有3種、上電復(fù)位、按鍵復(fù)位和看門狗定時器溢出復(fù)位。STDW100初始化設(shè)置有2種方式:

(1)當(dāng)系統(tǒng)上電、使能信號EN=0,STWD100xY看門狗啟動定時,定時周期為3.4 ms,在3.4 ms內(nèi)WDO輸出高電平,程序必須在3.4 ms內(nèi)送入喂狗指令否則系統(tǒng)認(rèn)為程序跑飛,WDO輸出低電平系統(tǒng)自動復(fù)位,如圖2所示。

(2)當(dāng)WDI輸入上升沿時看門狗定時器啟動,啟動后WDO保持原有高電平直到定時器3.4 ms后溢出WDO翻轉(zhuǎn),WDO輸出低電平系統(tǒng)自動復(fù)位如圖2所示。

5.2.2 STWD100的軟件設(shè)計

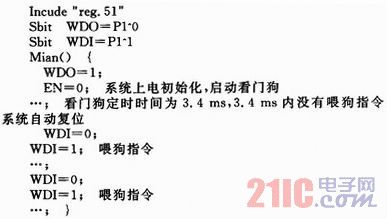

根據(jù)STWD100時序原理,當(dāng)系統(tǒng)上電初始化設(shè)置使能信號EN=0,WD0=1啟動看門狗,程序在3.4 ms定時周期內(nèi)喂狗防止系統(tǒng)死機或程序跑飛,如在3.4 ms內(nèi)系統(tǒng)未檢測到喂狗指令,WDO輸出低電平系統(tǒng)自動復(fù)位,具體程序如下:

5.3 STWD100實驗結(jié)果

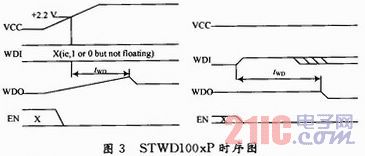

STWD100技術(shù)比較成熟,基本不會出現(xiàn)由STWD100自身技術(shù)原因和缺陷帶來的不穩(wěn)定,關(guān)鍵是用戶掌握好軟件看門狗喂狗的時間和時序,喂狗時間過短系統(tǒng)效率不高,喂狗時間過長容易導(dǎo)致系統(tǒng)重啟。STWD100xP時序圖如圖3所示。實驗結(jié)果證明在幾乎不占用CPU資源的情況下,系統(tǒng)加上STWD100硬件看門狗后,系統(tǒng)工作穩(wěn)定度提高很多幾乎沒有出現(xiàn)死機和程序跑飛的情況,有效防止了系統(tǒng)干擾提高了系統(tǒng)穩(wěn)定性和可靠性。

6 結(jié)語

在有交流接觸器、繼電器、電機控制的程控噴泉控制系統(tǒng)中,加STWD100硬件看門狗,系統(tǒng)連續(xù)開關(guān)50次運行正常;連續(xù)工作12 h并不間斷外加電機、焊機干擾,系統(tǒng)無死機、程序跑飛等異常情況出現(xiàn),工作穩(wěn)定可靠,解決了由繼電器、交流接觸器等器件動作時帶來的干擾,引起CPU誤動和死機等不穩(wěn)定現(xiàn)象。在實際中應(yīng)注意掌握好喂狗時間間隔,一般在1~2 ms效果最佳。STWD100硬件看門狗在不占用CPU資源的情況下,系統(tǒng)工作穩(wěn)定度和可靠性提高到100%,可廣泛用于繼電器、接觸器等具有較強干擾控制系統(tǒng)。