低壓差分信號(LVDS)是一種低壓、差分信號傳輸方案,主要用于高速數(shù)據(jù)傳輸。根據(jù) ANSI/TIA/EIA-644 規(guī)范中的定義,它是一種最為常見的差分接口。這種標準只對適合于 LVDS 應用的驅(qū)動器和接收機電氣特性進行了規(guī)定。因此,它只是一種電氣標準,常被一些更高級的協(xié)議標準當作其接口或物理層。

在高速模擬數(shù)字轉(zhuǎn)換器(ADC)中使用該傳輸方案可在保持轉(zhuǎn)換器高性能的同時實現(xiàn)高速數(shù)據(jù)輸出。獨立 ADC 必須能夠驅(qū)動以PCB走線形式存在的容性負載、以及接收電路的輸入邏輯。此處,ADC 輸出級的一個單端驅(qū)動器會導致大量瞬態(tài)開關(guān)噪聲,這些噪聲是由大電流晶體管的開和關(guān)造成的。這些瞬態(tài)會耦合回ADC的模擬前端,從而對其性能產(chǎn)生不利影響。

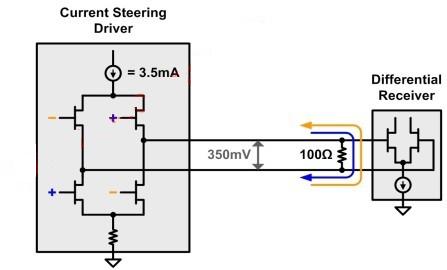

然而,LVDS 驅(qū)動器級需要在一個始終開啟的 3.5mA(典型值)電流源環(huán)境中運行(請參見圖 1)。通過差分對導體以不同方向重新分配電流,便可形成總線上的邏輯 1 和 0。這種消除開關(guān)噪聲和 EMI 的“始終開啟”特性正是降低 ADC 性能的主要原因。

圖 1: LVDS 驅(qū)動器和接收器。(電流型驅(qū)動 差分接收器)

由于專為點對點信號傳輸而設計,LVDS使用的是一種簡單的端接方案。安裝在接收器輸入端的單個100歐姆電阻端接差分對,從而消除了反射。

由于高阻抗接器輸入,驅(qū)動器電流源的全部電流流經(jīng)端接電阻,從而產(chǎn)生了一個 350 mV 額定值的低、差分總線電壓。該電壓在 1.2 V 共模電位左右擺動,其為典型驅(qū)動器輸出失調(diào)電壓(請參見圖 2)。

圖 2:LVDS 總線電壓電平。

相比單端方案,差分信號傳輸還有另一個 LVDS 好處,因為它不易受到共模噪聲的影響,并且產(chǎn)生更少的電磁干擾 (EMI)。

由于接收器只響應差分電壓,因此同鄰近的信號線耦合的噪聲被接收器視作共模調(diào)制,從而被拒絕接收。另外,由于兩個差分對導體傳導電流相等但極性相反,因此它們的磁場基本互相抵消,從而實現(xiàn) EMI 最小化。

根據(jù)數(shù)據(jù)速率的不同,標準 LVDS IC 可以驅(qū)動長達 10 米的距離。然而,不應強制高性能ADC驅(qū)動這一距離。取而代之的是,建議使用兩英寸以內(nèi)的較短的輸出線,以防止鄰近電路的噪聲耦合到 ADC 輸出端,因為其可能會反饋耦合至 ADC 模擬輸入端。

盡管低功耗、低 EMI 和高噪聲抗擾度使得 LVDS 成為高速數(shù)據(jù)轉(zhuǎn)換器的接口選擇,但是必須運用精心的布線技術(shù),以避免阻抗不連續(xù)和信號時延差,否則就抵消了上述 LVDS 的好處。