科學(xué)級(jí)CCD相機(jī)(Scientific grade CCD camera)是一種具有低噪聲、高靈敏度、大動(dòng)態(tài)范圍和高量子效率等優(yōu)良性能的CCD相機(jī),用于對(duì)微光信號(hào)檢測(cè)和微光成像。它在射線數(shù)字成像檢測(cè)、生物 醫(yī)學(xué)工程、水下攝影、武器裝備、天文觀測(cè)、空間對(duì)地觀測(cè)等多種技術(shù)領(lǐng)域得到了廣泛應(yīng)用。

科學(xué)級(jí)CCD相機(jī)一般由高速CCD 感光芯片、視頻信號(hào)處理器、時(shí)序控制器、時(shí)序發(fā)生器、時(shí)序驅(qū)動(dòng)器、外部光學(xué)成像系統(tǒng)等部分組成,其中時(shí)序發(fā)生器性能的優(yōu)劣直接決定了相機(jī)的品質(zhì)參數(shù)。該科學(xué)級(jí)CCD相機(jī)采用DALSA公司的IL-E2 型TDI-CCD作為

2 TDI-CCD的工作原理及驅(qū)動(dòng)分析

2.1 TDI-CCD工作原理簡(jiǎn)介

TDI(time delay and integration)是一種能夠增加線掃描傳感器靈敏度的掃描技術(shù)。TDI-CCD是具有一種面陣結(jié)構(gòu)、線陣輸出的新型CCD,較普通的線陣CCD而 言,它具有多重級(jí)數(shù)延時(shí)積分的功能。從其結(jié)構(gòu)來(lái)看,多個(gè)線陣平行排列,像元在線陣方向和級(jí)數(shù)方向呈矩形排列,像元分布示意圖如圖1所示。

圖1 TDI-CCD像元分布示意圖

圖1中,TDI-CCD的電荷累積方向是沿Y向進(jìn)行的,其推掃級(jí)數(shù)自下而上為第1級(jí)至第96 級(jí)。在成像過(guò)程中,隨著相機(jī)(或景物)的運(yùn)動(dòng),TDI-CCD從第96級(jí)至第1級(jí)依次感光,電荷從第96級(jí)至第1級(jí)逐級(jí)累積。最終,經(jīng)過(guò)多重延時(shí)積分積累 起來(lái)的電荷包(成像數(shù)據(jù)信息)轉(zhuǎn)移到CCD水平讀出寄存器上,并從第1級(jí)經(jīng)

2.2 關(guān)于DALSA IL-E2型TDI-CCD 圖像傳感器

CCD 圖像傳感器是科學(xué)級(jí)CCD相機(jī)的關(guān)鍵組成部件, 其性能的優(yōu)劣直接影響著相機(jī)的功能和使用效果。該科學(xué)級(jí)CCD 相機(jī)選用了加拿大DALSA 公司生產(chǎn)的IL-E2型TDI-CCD 圖像傳感器,該TDI-CCD的像素結(jié)構(gòu) 2048×96 。像元尺寸為13μm( H) ×13μm( V )、最高數(shù)據(jù)輸出頻率為20MHz 、動(dòng)態(tài)范圍為1600:1 、單向、單端輸出、級(jí)數(shù)可選、具有藍(lán)光響應(yīng)增強(qiáng)功能的TDI-CCD。IL-E2型TDI-CCD可以分為3個(gè)功能區(qū),即光敏元探測(cè)區(qū)、電荷傳輸區(qū)、檢測(cè) 輸出區(qū)。

2.3 IL-E2型TDI-CCD驅(qū)動(dòng)時(shí)序分析

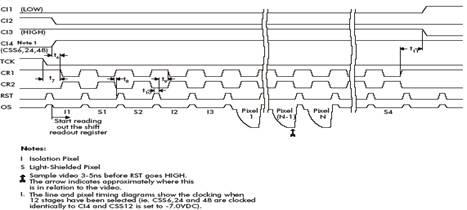

TDI-CCD的驅(qū)動(dòng)時(shí)序控制比普通線陣CCD的驅(qū)動(dòng)時(shí)序控制要復(fù)雜的多, IL-E2型TDI-CCD的時(shí)序控制包括各種直流電平控制和各種時(shí)鐘脈沖序列控制。對(duì)于前者,主要包括供電電壓VDD、輸出柵電壓VEST、溢出柵電壓 VOV、襯底電壓VBB和級(jí)數(shù)控制偏置電壓等;對(duì)于后者,主要包括行轉(zhuǎn)移時(shí)鐘脈沖TCK,像元移位讀出時(shí)鐘脈沖CR1、CR2,輸出復(fù)位時(shí)鐘脈沖 RST,TDI方向移位寄存器驅(qū)動(dòng)時(shí)鐘脈沖CI1~CI4,級(jí)數(shù)控制時(shí)鐘脈沖CSS6、CSS12、CSS24、CSS48。TDI-CCD工作時(shí),在行 轉(zhuǎn)移時(shí)鐘脈沖TCK為高電平期間,像元感光產(chǎn)生的信號(hào)電荷在TDI方向移位寄存器驅(qū)動(dòng)時(shí)鐘脈沖CI1、CI2、CI3、CI4的共同作用下,沿著 TDI(TDI級(jí)數(shù)由TDI級(jí)數(shù)控制脈沖選為6、12、24、48、96中的一種)方向積累并轉(zhuǎn)移到輸出移位寄存器中;當(dāng)TCK為低電平時(shí),TDI- CCD在像元移位讀出時(shí)鐘脈沖CR1、CR2的作用下,輸出復(fù)位時(shí)鐘脈沖RST每來(lái)一個(gè)有效電平高電平時(shí),TDI-CCD的輸出信號(hào)OS端輸出一個(gè)信號(hào), 直到信號(hào)輸出完為止。之后TCK由低電平變?yōu)楦唠娖剑珻I1、CI2、CI3、CI4也相應(yīng)的變?yōu)橛行щ娖剑D(zhuǎn)移上一次轉(zhuǎn)移完后像元感光產(chǎn)生的信號(hào)電荷, 開(kāi)始一個(gè)新的周期。這些時(shí)序控制的詳細(xì)對(duì)應(yīng)關(guān)系如圖2所示。

圖2 TDI-CCD時(shí)序詳圖

對(duì)于此TDI-CCD時(shí)序設(shè)計(jì)與普通線陣CCD時(shí)序設(shè)計(jì)存在以下幾個(gè)突出特點(diǎn)。(1)在TDI方向存在4相移位寄存器驅(qū)動(dòng)時(shí)鐘,它們的周期與行 周期一致,高電平脈寬t3應(yīng)大于3μs, CI1的上升沿滯后于TCK的上升沿,CI2的下降沿滯后于TCK的下降沿,CI1、CI2的高電平脈寬至少有1μs的重疊。CI3、CI4在時(shí)序關(guān)系上 分別為CI1、CI2的倒相。(2)此TDI-CCD的工作級(jí)數(shù)可以通過(guò)CSS6、CSS12、CSS24、CSS48四個(gè)級(jí)數(shù)選擇信號(hào)進(jìn)行控制,使其工 作于96、48、24、12和6級(jí)。

3 時(shí)序發(fā)生器的原理組成和工作過(guò)程分析

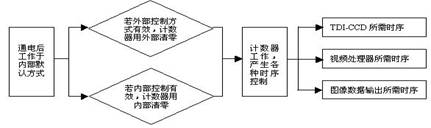

時(shí)序發(fā)生器產(chǎn)生TDI-CCD、視頻處理器和圖像數(shù)據(jù)輸出所需的各種時(shí)鐘脈沖信號(hào), 時(shí)序發(fā)生器在CCD成像單元工作中起著時(shí)間上同步協(xié)調(diào)的作用。它由時(shí)序控制器給出的指令和參數(shù)予以控制。時(shí)序控制器控制TDI-CCD工作時(shí)的行轉(zhuǎn)移周 期, 積分級(jí)數(shù),控制指令和參數(shù)以串行數(shù)據(jù)的形式送至?xí)r序控制器中,時(shí)序發(fā)生器根據(jù)時(shí)序控制器給出的指令和數(shù)據(jù)產(chǎn)生TDI-CCD和視頻處理器所需要的時(shí)鐘脈沖 信號(hào): 行轉(zhuǎn)移時(shí)鐘脈沖、像元移位讀出時(shí)鐘脈沖、輸出復(fù)位時(shí)鐘脈沖、TDI方向移位寄存器驅(qū)動(dòng)時(shí)鐘脈沖、級(jí)數(shù)控制時(shí)鐘脈沖、相關(guān)雙采樣時(shí)鐘脈沖、A/D

時(shí)序發(fā)生器的設(shè)計(jì):時(shí)序發(fā)生器生成TDI-CCD、視頻處理器和圖像數(shù)據(jù)輸出所需要的各種時(shí)序。所有時(shí)序是由主振脈沖序列通過(guò)逐級(jí)分頻后的脈沖 序列進(jìn)行邏輯和組合運(yùn)算產(chǎn)生的。它們之間滿足嚴(yán)格的相位關(guān)系, 這是相機(jī)系統(tǒng)協(xié)調(diào)工作的基礎(chǔ)。時(shí)序發(fā)生器的功能框圖如圖3所示。相機(jī)系統(tǒng)一通電就應(yīng)保證立即工作在內(nèi)部默認(rèn)方式, 這樣就能夠馬上判斷系統(tǒng)是否正常。如果外部或內(nèi)部設(shè)置指令無(wú)效, 系統(tǒng)也返回默認(rèn)方式, 這是相機(jī)系統(tǒng)可靠性的體現(xiàn)。時(shí)序發(fā)生器所產(chǎn)生的各種時(shí)鐘由VHDL 語(yǔ)言完成。

圖3 時(shí)序發(fā)生器功能框圖

4 用 FPGA器件實(shí)現(xiàn)科學(xué)級(jí)CCD相機(jī)時(shí)序發(fā)生器

4.1 FPGA技術(shù)及FPGA器件

FPGA-現(xiàn)場(chǎng)可編程門(mén)陣列技術(shù)是二十年前出現(xiàn),而在近幾年快速發(fā)展的可編程邏輯器件技術(shù)。這種基于EDA技術(shù)的芯片正在成為電子系統(tǒng)設(shè)計(jì)的主 流。大規(guī)模可編程邏輯器件FPGA是當(dāng)今應(yīng)用最廣泛的可編程專用集成電路(ASIC)。設(shè)計(jì)人員利用它可以在辦公室或?qū)嶒?yàn)室里設(shè)計(jì)出所需的專用集成電路, 從而大大縮短了產(chǎn)品上市時(shí)間,降低了開(kāi)發(fā)成本。此外,F(xiàn)PGA還具有靜態(tài)可重復(fù)編程和動(dòng)態(tài)在系統(tǒng)重構(gòu)的特性,使得硬件的功能可以像軟件一樣通過(guò)編程來(lái)修 改。因此,F(xiàn)PGA技術(shù)的應(yīng)用前景非常廣闊。

XC2VP20-FF1152 是Xilinx 公司推出的Virtex-II Pro 系列的FPGA,它內(nèi)部有豐富的資源[5],包括8 個(gè)數(shù)字時(shí)鐘管理器(DCM),290Kbits 的分布RAM,88×16kByte 的Block RAM,88 個(gè)18×18 的專用乘法器(Dedicated Multipliers)單元,2 個(gè)

4.2 基于FPGA的科學(xué)級(jí)CCD相機(jī)時(shí)序發(fā)生器的設(shè)計(jì)與仿真

IL-E2型TDI-CCD的像元數(shù)有每行512,1024和2048三種,本文以2048像元數(shù)為例設(shè)計(jì)時(shí)序電路。2048為有效像元數(shù),由 于每行有5個(gè)隔離像元,4個(gè)暗參考像元,故設(shè)計(jì)中要保證最少使每行輸出2057個(gè)像元,也就是使每個(gè)行周期內(nèi)最少有2057個(gè)CR1、CR2、RST驅(qū)動(dòng) 脈沖。每行除了2057個(gè)像元驅(qū)動(dòng)脈沖以外,其余為空驅(qū)動(dòng)脈沖。空驅(qū)動(dòng)脈沖數(shù)越多,行周期時(shí)間越長(zhǎng),CCD曝光積分時(shí)間越長(zhǎng),靈敏度相應(yīng)提高,但過(guò)長(zhǎng)的曝 光積分時(shí)間會(huì)使CCD輸出飽和失真,故空驅(qū)動(dòng)脈沖數(shù)目不易過(guò)多。積分時(shí)間和像元移位讀出時(shí)鐘頻率是CCD時(shí)序電路的設(shè)計(jì)依據(jù)。在工程應(yīng)用中,我們根據(jù)技術(shù) 指標(biāo)要求,算出行積分時(shí)間即行周期(T)為0.365ms,以此確定合適的系統(tǒng)主時(shí)鐘。驅(qū)動(dòng)時(shí)序用超高速集成電路硬件描述語(yǔ)言(VHDL)編寫(xiě),程序主要 包括:(1)調(diào)用所需的庫(kù)函數(shù)和程序包;(2)定義輸入和輸出端口;(3)用計(jì)數(shù)器對(duì)輸入的系統(tǒng)主時(shí)鐘進(jìn)行分頻。(4)驅(qū)動(dòng)時(shí)序信號(hào)的產(chǎn)生和輸出。由 XILINX公司的設(shè)計(jì)軟件ISE6.2對(duì)XC2VP20-FF1152器件進(jìn)行時(shí)序設(shè)計(jì),通過(guò)時(shí)序仿真與工程應(yīng)用驗(yàn)證了能完成上述所有功能。系統(tǒng)邏輯功 能時(shí)序仿真波形如圖4所示。

圖4時(shí)序發(fā)生器時(shí)序仿真圖

5 結(jié)束語(yǔ)

本文的創(chuàng)新是采用FPGA 器件設(shè)計(jì)科學(xué)級(jí)CCD相機(jī)時(shí)序發(fā)生器, 使得電路由原來(lái)復(fù)雜的設(shè)計(jì)變成主要只用一片XILINX公司的可編程器件XC2VP20-FF1152來(lái)實(shí)現(xiàn)。獨(dú)立的單元測(cè)試與系統(tǒng)聯(lián)調(diào)結(jié)果均表明: 采用現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA) 技術(shù)實(shí)現(xiàn)CCD相機(jī)時(shí)序發(fā)生器, 可使電路成倍簡(jiǎn)化,提高了系統(tǒng)的集成度,時(shí)序發(fā)生器抗干擾能力也增強(qiáng)了,其功耗也成倍降低,從而實(shí)現(xiàn)了科學(xué)級(jí)CCD 相機(jī)工作時(shí)的高可靠性、穩(wěn)定性,同時(shí)還使設(shè)計(jì)與調(diào)試周期成倍縮短。該設(shè)計(jì)方案為T(mén)DI-CCD在科學(xué)級(jí)CCD相機(jī)中的應(yīng)用開(kāi)拓了更加廣闊的前景。