0 引 言

電荷耦合器件(CCD)是一種轉(zhuǎn)換式圖像傳感器,是以電荷作為信號(hào)的MOS型半導(dǎo)體器件。其基本結(jié)構(gòu)是一種密排的MOS電容器,能夠存儲(chǔ)由入射光在CCD光敏單元激發(fā)而產(chǎn)生的電荷,并且能在適當(dāng)?shù)臅r(shí)鐘脈沖驅(qū)動(dòng)下,把存儲(chǔ)的電荷以電荷包的形式定向傳輸轉(zhuǎn)移,從而完成從光信號(hào)到電信號(hào)的轉(zhuǎn)換。CCD具有體積小、質(zhì)量輕、功耗小、工作電壓低和抗燒毀等特點(diǎn),在分辨率、動(dòng)態(tài)范圍、靈敏度等方面的優(yōu)越性也是很多其他器件無(wú)法比擬的,目前CCD器件已經(jīng)廣泛地應(yīng)用到各種各樣的成像系統(tǒng)中,成為現(xiàn)代電子學(xué)和現(xiàn)代測(cè)試技術(shù)中最活躍的傳感器之一。

電荷耦合器件不同于普通的MOS型半導(dǎo)體器件,它需要在較復(fù)雜的驅(qū)動(dòng)脈沖下才能正常工作。在CCD應(yīng)用技術(shù)中,用于產(chǎn)生CCD驅(qū)動(dòng)時(shí)序的設(shè)計(jì),是CCD數(shù)據(jù)采集電路設(shè)計(jì)的關(guān)鍵之一。產(chǎn)生驅(qū)動(dòng)時(shí)序的方法多種多樣,常用的有下面幾種:EPROM方法、直接數(shù)字電路驅(qū)動(dòng)方法、單片機(jī)、專用IC等,各有優(yōu)缺點(diǎn)。由于CPLD的集成度高,在速度和時(shí)序控制上具有較大的優(yōu)勢(shì),而且在電路設(shè)計(jì)完成后,可以根據(jù)需要將CPLD邏輯重新編程,因此選用CPLD來(lái)設(shè)計(jì)CCD的驅(qū)動(dòng)時(shí)序是一種不錯(cuò)的選擇。目前,大多數(shù)CCD工作時(shí)序設(shè)計(jì)都是采用CPLD來(lái)實(shí)現(xiàn)和完成的。

1μPD795結(jié)構(gòu)原理及驅(qū)動(dòng)時(shí)序

1.1 μPD795結(jié)構(gòu)原理

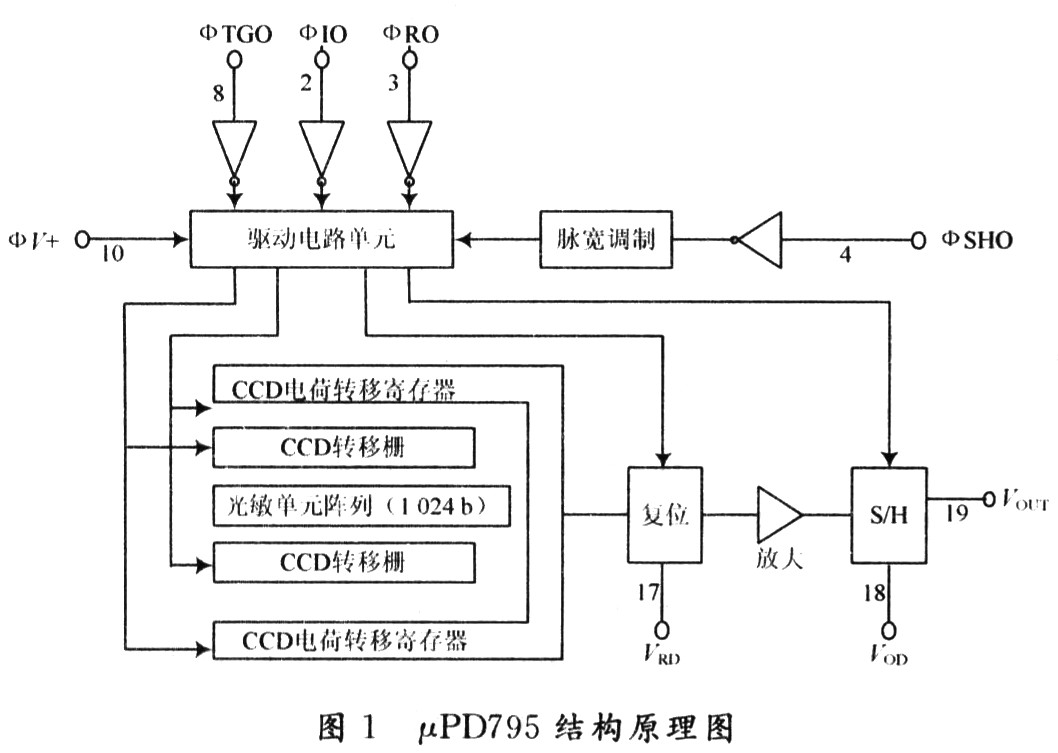

μPD795是NEC公司生產(chǎn)的高靈敏度、低暗電流、具有內(nèi)置放大電路和采樣保持電路的線陣CCD圖像傳感器。它內(nèi)部包含一列1 024像元的光敏二極管和兩列525位的電荷轉(zhuǎn)移寄存器。可以工作在5 V驅(qū)動(dòng)(脈沖)和12 V電源條件下。同時(shí)μPD795具有出色的光電特性,很高的轉(zhuǎn)移效率,達(dá)到了99.996%。主要由三個(gè)模塊組成:表面積分單元,用于產(chǎn)生電荷信號(hào);CCD移位寄存器,用于電荷信號(hào)轉(zhuǎn)移;輸出放大器,將電荷信號(hào)轉(zhuǎn)換成電壓信號(hào)。

結(jié)構(gòu)原理圖如圖1所示,封裝形式為20腳DIP。中間一排是由光敏二極管構(gòu)成的光敏陣列,有效單元為1 024位,其作用是接收外界的光信號(hào),并轉(zhuǎn)換為相應(yīng)的電荷信號(hào),光敏陣列兩側(cè)分別為轉(zhuǎn)移柵和電荷轉(zhuǎn)移寄存器,在傳輸門(mén)時(shí)鐘信號(hào)φTGO的作用下,像元的光電信號(hào)分別轉(zhuǎn)移到位于其兩側(cè)的CCD轉(zhuǎn)移柵。而后CCD的MOS電容中的電荷信號(hào)在φIO的作用下從輸出端口串行輸出。

1.2 驅(qū)動(dòng)時(shí)序分析

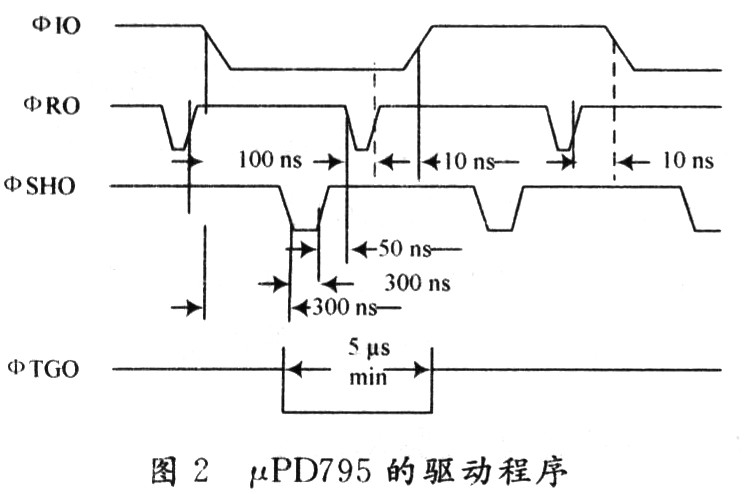

CCD器件需要三路以上的驅(qū)動(dòng)時(shí)序脈沖。各驅(qū)動(dòng)脈沖必須嚴(yán)格滿足相位時(shí)序要求,才能保證CCD器件正常工作。該芯片正常工作需要四路脈沖,分別為電荷轉(zhuǎn)移寄存器時(shí)鐘φIO、復(fù)位時(shí)鐘φRO、采樣保持時(shí)鐘φSHO以及傳輸門(mén)時(shí)鐘φTGO。他們之間的時(shí)序關(guān)系如圖2所示。

CCD的驅(qū)動(dòng)時(shí)序是一組周期性且關(guān)系比較復(fù)雜的脈沖信號(hào),它是影響CCD器件的信號(hào)處理能力、轉(zhuǎn)移效率、信噪比等性能的一個(gè)重要因素。常規(guī)的驅(qū)動(dòng)電路設(shè)計(jì)有以下幾種方法:面陣CCD通常采用相應(yīng)的專用驅(qū)動(dòng)IC,但是難以調(diào)試,而且無(wú)法適應(yīng)于其他CCD器件;線陣CCD可采用數(shù)字電路驅(qū)動(dòng)、單片機(jī)I/O口驅(qū)動(dòng),或者選用可編程邏輯器件針對(duì)特定器件的驅(qū)動(dòng)時(shí)序要求完成驅(qū)動(dòng)電路設(shè)計(jì)。為了使CCD器件在各種光強(qiáng)信號(hào)下正常工作,需要設(shè)置不同的積分時(shí)間和相應(yīng)的驅(qū)動(dòng)脈沖,傳統(tǒng)的單一驅(qū)動(dòng)脈沖無(wú)法滿足工作要求,必須設(shè)計(jì)一種可提供多種驅(qū)動(dòng)脈沖的電路。

2 系統(tǒng)框圖

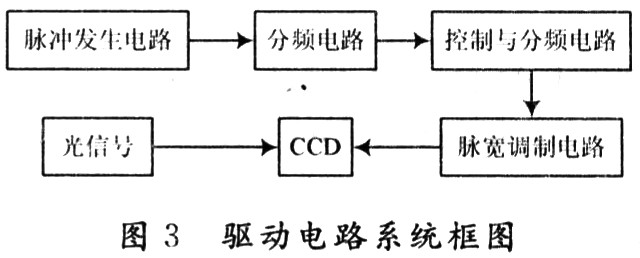

整個(gè)驅(qū)動(dòng)電路系統(tǒng)可以分為四個(gè)部分;如圖3所示,包括脈沖發(fā)生電路、分頻電路、控制與分頻電路以及脈寬調(diào)制電路。脈沖發(fā)生電路可由74LS00和7.5 MHz的晶振以及相應(yīng)的阻容電路組成,該部分相對(duì)簡(jiǎn)單,電阻和電容的數(shù)目也不多。分頻電路可選用D觸發(fā)器/JK觸發(fā)器,如 74LS(HC)74,74LS(HC)76,均帶置位、清零端,較易控制;采用同步計(jì)數(shù)器74LS163實(shí)現(xiàn)邏輯功能,該計(jì)數(shù)器為四位二進(jìn)制可編程計(jì)數(shù)器。當(dāng)然也可以采用82C54(10MHz可編程)。控制電路由μPD4011,μPD4012,μPD4013以及74LS27組成。μPD4011作為外部控制信號(hào)可以起到調(diào)整頻率的作用。脈寬調(diào)制電路由與非門(mén)、或非門(mén)和帶有直接清零功能的二進(jìn)制同步計(jì)數(shù)器組成。

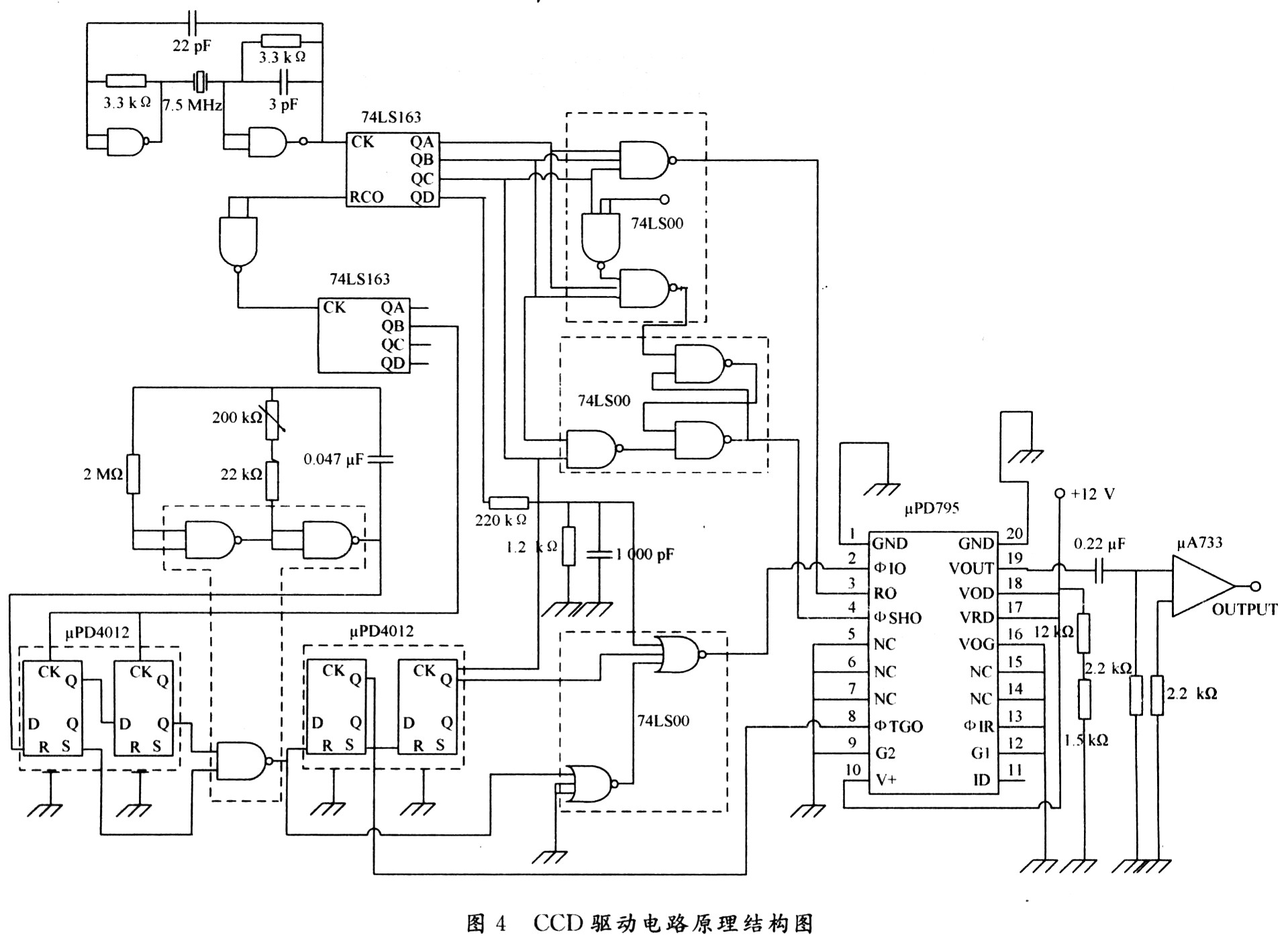

3 驅(qū)動(dòng)電路

CCD 圖像傳感器的驅(qū)動(dòng)。簡(jiǎn)言之就是通過(guò)驅(qū)動(dòng)電路產(chǎn)生CCD正常工作所需的特定脈沖。為了產(chǎn)生如圖2所示的各路驅(qū)動(dòng)脈沖以及滿足傳感器的小型化和工作速度的要求。采用復(fù)雜可編程邏輯器件CPLD實(shí)現(xiàn)其邏輯功能是一個(gè)較好的選擇。CPLD是基于乘積項(xiàng)結(jié)構(gòu),可實(shí)現(xiàn)各種邏輯運(yùn)算.全硬件結(jié)構(gòu),具有極大的靈活性和通用性,使用方便,硬件測(cè)試和實(shí)現(xiàn)快捷,開(kāi)發(fā)效率高,成本低,上市時(shí)間短,技術(shù)維護(hù)簡(jiǎn)單,工作可靠性好等優(yōu)點(diǎn)。在該設(shè)計(jì)中,μPD795所需的驅(qū)動(dòng)脈沖是在 Max+PlusⅡ環(huán)境下完成設(shè)計(jì)并編譯、校驗(yàn)后在線下載到CPLD器件內(nèi)部,實(shí)現(xiàn)邏輯功能。實(shí)際的驅(qū)動(dòng)電路的原理結(jié)構(gòu)圖如圖4所示。該例中的驅(qū)動(dòng)電路并不復(fù)雜,所用的器件也有限。但若驅(qū)動(dòng)脈沖種數(shù)繼續(xù)增加,則電路的復(fù)雜程度也要成比例增加。該設(shè)計(jì)中采用EPM7064SLC44-7,該芯片由64個(gè)宏單元組成,是Altera公司生產(chǎn)的MAX7000S系列中芯片的一種,可以實(shí)現(xiàn)在線編程。在Max+PlusⅡ環(huán)境下進(jìn)行了仿真,得到了滿意的結(jié)果后進(jìn)行了硬件設(shè)計(jì)。

4 實(shí)驗(yàn)結(jié)果

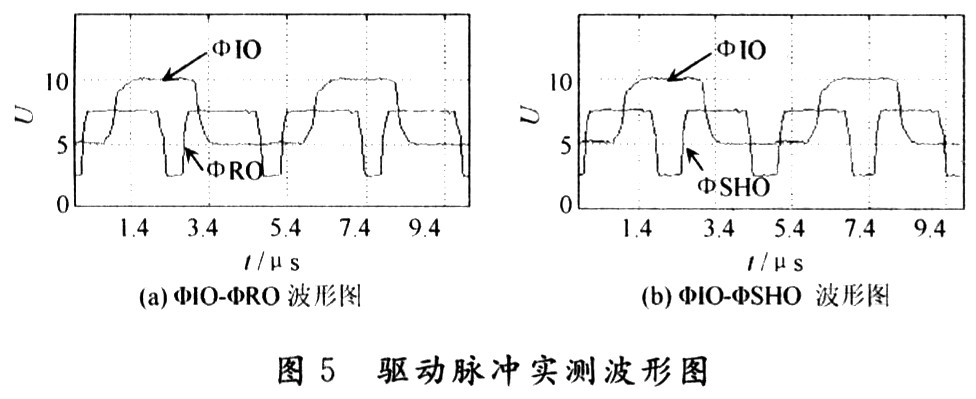

對(duì)制作PCB板用示波器和邏輯分析儀進(jìn)行了測(cè)試,測(cè)量檔位為2 μs,測(cè)量CCD驅(qū)動(dòng)波形φIO,φRO,φSHO如圖5所示。縱坐標(biāo)中低電平為0 V,高電平為5 V。

5 結(jié) 語(yǔ)

時(shí)序電路中的CPLD,除提供CCD正常工作所需的時(shí)序外,還保留了部分引腳和功能模塊,可以作為增加某些新功能的需要。從該驅(qū)動(dòng)電路與信號(hào)處理單元及上位機(jī)和顯示器構(gòu)成的完整線陣CCD相機(jī)系統(tǒng),以及從實(shí)測(cè)波形數(shù)據(jù)來(lái)看。該驅(qū)動(dòng)電路在實(shí)際使用中穩(wěn)定可靠,達(dá)到了設(shè)計(jì)前的要求,這說(shuō)明用CPLD構(gòu)成線陣 CCD相機(jī)驅(qū)動(dòng)電路是一種切實(shí)可行的方案。