基于DSP的高速激光標(biāo)記控制系統(tǒng)設(shè)計

摘要: 本文在激光標(biāo)記控制技術(shù)方面進行了一些新的探索:利用PCI的高速數(shù)據(jù)傳輸和DSP高速數(shù)據(jù)處理能力,提出一種“PC機+PCI總線+DSP控制板卡”的方式,用于振鏡標(biāo)記控制系統(tǒng),從而實現(xiàn)對標(biāo)記控制的精確控制,提高控制效率,保障系統(tǒng)實時性。DSP控制板卡是整個系統(tǒng)的核心,它直接決定著系統(tǒng)的掃描速度和掃描精度,本文將著重介紹該控制板卡的設(shè)計。

Abstract:

Key words :

振鏡掃描式激光標(biāo)記技術(shù)就是通過控制兩片高速振鏡的偏轉(zhuǎn)角, 改變激光的傳播方向, 經(jīng)過F-Theata透鏡在工件表面的聚焦, 在工件表面作標(biāo)記。與傳統(tǒng)的標(biāo)記技術(shù)相比, 它具有適用面廣(對不同材料、形狀的加工表面均適合) , 工件無機械變形, 無污染, 標(biāo)記速度快, 重復(fù)性好, 自動化程度高等特點, 在工業(yè)、國防、科研等許多領(lǐng)域具有廣泛的用途。高速高精度的振鏡標(biāo)記已成為當(dāng)今標(biāo)記行業(yè)的發(fā)展方向。

傳統(tǒng)的振鏡標(biāo)記控制系統(tǒng)通過PC 機的串口、并口ISA 總線與單片控制板相連,這種方式接口簡單、連接方便, 開發(fā)費用低, 但由于傳輸速度低, 已不能滿足現(xiàn)代數(shù)控系統(tǒng)的實時性要求。本文在激光標(biāo)記控制技術(shù)方面進行了一些新的探索:利用PCI的高速數(shù)據(jù)傳輸和title="DSP">DSP高速數(shù)據(jù)處理能力,提出一種“PC機+PCI總線+DSP控制板卡”的方式,用于振鏡標(biāo)記控制系統(tǒng),從而實現(xiàn)對標(biāo)記控制的精確控制,提高控制效率,保障系統(tǒng)實時性。DSP控制板卡是整個系統(tǒng)的核心,它直接決定著系統(tǒng)的掃描速度和掃描精度,本文將著重介紹該控制板卡的設(shè)計。

1 DSP芯片

DSP控制板卡的主芯片選用德州儀器公司C6000系列的高速數(shù)據(jù)處理芯片TMS320C6205。該芯片為高性能的定點處理器,主頻可達200MHz,每個周期能執(zhí)行8條32-bit的指令,處理速度可達1600MIPS;采用高性能的VLIW結(jié)構(gòu)的TMS320C62xTM DSP核,有8個獨立的功能單元,32個32位的通用寄存器;提供64K字節(jié)的內(nèi)部程序RAM和64K字節(jié)的內(nèi)部數(shù)據(jù)RAM;提供32位的外部存儲器無縫接口,包括同步器件(如SDRAM、SBSRAM等)、異步器件(如FLASH、SRAM等)和可尋址52M字節(jié)的外部存儲空間;提供靈活的PLL、時鐘產(chǎn)生器,可配置倍頻值;提供符合PCI 2.2規(guī)范的PCI總線接口,直接實現(xiàn)芯片和PCI總線的橋接功能;提供兩個32位的定時器;提供在線調(diào)試的JTAG邊界掃描接口。采用此芯片,能夠?qū)崿F(xiàn)高速的數(shù)據(jù)處理,保證系統(tǒng)工作的實時性,且由于帶了PCI橋接功能,提供了和PCI總線的接口,經(jīng)濟可靠。

2 硬件設(shè)計

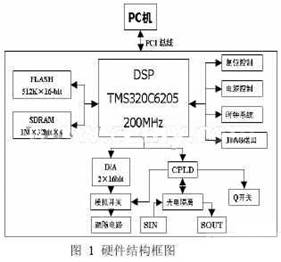

2.1 結(jié)構(gòu)框圖

如圖1所示為系統(tǒng)的硬件結(jié)構(gòu)框圖。DSP控制板卡通過PCI總線與PC機連接,實現(xiàn)高速通信。DSP處理模塊為主控制模塊,使用主頻為200MHz的 TMS320C6205芯片作為主控制芯片。DSP處理模塊充分利用了C6000系列DSP的快速計算能力和高精度定時器,能夠保證振鏡標(biāo)記機進行勻速、高速標(biāo)記,這些由PC機是沒有辦法做到的。DSP的外圍電路包括存儲模塊、復(fù)位控制、電源控制、時鐘系統(tǒng)、JTAG端口、數(shù)模轉(zhuǎn)換模塊、CPLD邏輯控制模塊和光電隔離模塊等。其中存儲模塊包括FLASH模塊和SDRAM模塊,F(xiàn)LASH用來存儲系統(tǒng)啟動代碼和軟件代碼,SDRAM用于提供軟件運行時所需的額外存儲空間。DSP控制板卡輸出兩路模擬量控制兩塊振鏡的運動,輸出Q開關(guān)控制信號以控制激光器的開關(guān)光,輸入/輸出16路光電隔離信號用于功能擴展。

2.2 PC機與DSP的通信

PCI 總線是一種不依附于某個具體處理器的局部總線。從結(jié)構(gòu)上看,PCI是在CPU和原來的系統(tǒng)總線之間插入的一級總線,具體由一個橋接電路實現(xiàn)對這一層的管理,并實現(xiàn)上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送。管理器提供了信號緩沖,使之能支持10種外設(shè),并能在高時鐘頻率下保持高性能。PCI總線也支持總線主控技術(shù),允許智能設(shè)備在需要時取得總線控制權(quán),以加速數(shù)據(jù)傳送。PCI總線相比起ISA總線,有傳輸速度快,傳輸量大的優(yōu)點。

本系統(tǒng)選用TMS320C6205,該芯片自帶了符合PCI2.2規(guī)范的PCI總線橋接功能,開發(fā)者免去了PCI協(xié)議的硬件和軟件實現(xiàn),給系統(tǒng)設(shè)計帶來了便利,縮短了開發(fā)周期,也節(jié)省了開發(fā)費用。開發(fā)者只需將PCI插槽上的總線信號和DSP芯片上相關(guān)的PCI總線信號直接相連即可。帶“金手指”的DSP控制板卡可以直接插在PC機的PCI卡槽中使用,實現(xiàn)PC機與DSP之間的通信。PCI設(shè)備可以訪問所有的內(nèi)部RAM空間、外設(shè)和外部存儲器空間。

DSP控制板卡使用的PCI總線寬度為32為(3.3V),總線頻率為33MHz,傳輸速率為33×32/4MB/s = 132MB/s 。此傳輸速率為整個系統(tǒng)能實現(xiàn)高速運行提供了保障。

2.3 CPLD邏輯控制

整個高速系統(tǒng)的邏輯控制是通過高速CPLD芯片來實現(xiàn)的。選用ALTERA公司的MAX7128E芯片實現(xiàn),可用編程邏輯門為2500,宏單元數(shù)128,邏輯陣列塊數(shù)8,用戶可定義I/O腳100個,pin-to-pin延時為5ns。MAX7000系列器件可以通過編程器進行編程,也可以在線編程。本設(shè)計采用了在線編程(ISP)。ISP允許在設(shè)計開發(fā)過程中迅速方便地重復(fù)編程,簡化了制作過程,允許器件在編程之前就先裝配到印制板上。

系統(tǒng)設(shè)計中LED信號燈、FLASH、DA芯片、16路I/O光電隔離接口、模擬開關(guān)、Q開關(guān)、PWM輸出、軟件復(fù)位控制都使用了CE1空間的地址,為了防止這些器件的互相干擾,必須對輸入地址進行譯碼。通過判斷輸入到CPLD的PA[2:6]和PA[16:21]可以知道DSP正在訪問的地址區(qū)域,進行CE1空間的地址譯碼,從而產(chǎn)生相應(yīng)的控制信號,以實現(xiàn)邏輯控制和時序控制。

CPLD上構(gòu)建的寄存器的高地址都是一樣的,命名為dsp_reg_addr,由Pa16~21構(gòu)成,若Pa16~21設(shè)置為"111000"即表示地址0x0178xxxx。

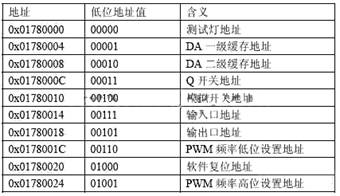

低地址由Pa2~6構(gòu)成,對10個寄存器尋址,地址對應(yīng)關(guān)系見表1所示。

表 1地址分配表

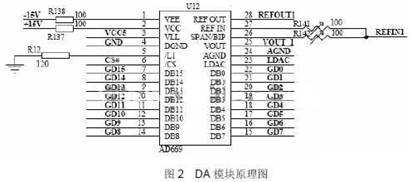

2.4 數(shù)模轉(zhuǎn)換模塊

數(shù)模轉(zhuǎn)換模塊將DSP處理完的數(shù)字信號轉(zhuǎn)換為模擬信號以控制兩路振鏡的偏轉(zhuǎn)。由于現(xiàn)在對標(biāo)記精度的要求越來越高,傳統(tǒng)的8位數(shù)模轉(zhuǎn)換器已無法滿足用戶的需求,因此本系統(tǒng)選用ADI公司的16位高精度數(shù)模轉(zhuǎn)換器AD669芯片,如圖2所示。AD669為16位并行輸入,二級數(shù)據(jù)緩存結(jié)構(gòu)。設(shè)計中將/L1信號直接接地設(shè)置為有效,通過控制/CS和LDAC信號分別控制一級緩存和二級緩存。控制振鏡信號的電壓范圍為-10V~+10V,以標(biāo)記100mm×100mm幅面大小的標(biāo)牌為例,精度可達100mm/216=0.0015mm,對應(yīng)最小輸出電壓為0.00031V。

經(jīng)實驗發(fā)現(xiàn),在上電時,AD669芯片的輸出為一不可控量,會使振鏡在上電瞬間有一個偏轉(zhuǎn),倘若偏轉(zhuǎn)幅度過大,長期使用會導(dǎo)致振鏡的斷裂。為了保護振鏡,可設(shè)計一個模擬開關(guān)電路以控制AD669芯片上電時的輸出,使其為0V。筆者將模擬開關(guān)放在AD669芯片的參考電壓輸入端,通過CPLD實現(xiàn)對模擬開關(guān)的控制,來控制參考電壓的有無,從而保證在上電時振鏡不偏轉(zhuǎn)。

3 PCB設(shè)計

該控制板卡選用主頻200MHz的高速DSP處理芯片,高速信號系統(tǒng)中,存在EMC問題,將影響系統(tǒng)的性能。為了設(shè)計出一塊穩(wěn)定,抗干擾性能好的控制板卡,采取了以下措施

1、板層的合理安排

該控制板卡為六層板,板層設(shè)計為(從頂層到底層依次)信號層-地層-電源層-信號層-地層-信號層。這樣的板層結(jié)構(gòu)安排,使每一個信號層和電源層都緊鄰一個地層,給信號提供一個較短的回流路徑。

2、時鐘信號線的處理

PCI時鐘信號的一半要靠反射波來提升,因此,時鐘信號CLK走線長度近似為2500 mil,走蛇形線實現(xiàn)(此點在PCI2.2規(guī)范的走線要求中有明確規(guī)定)。對于DSP芯片,晶振電路盡量靠近DSP芯片,且時鐘信號盡量短。

3、SDRAM相關(guān)信號線的處理

SDRAM工作頻率為100MHz,在高頻下,信號的傳輸時間和信號的走線長度有直接的關(guān)系,已不能忽略此問題。因此SDRAM的數(shù)據(jù)線和地址線要等長走線,以保證信號傳輸?shù)馁|(zhì)量。另外,串?dāng)_和振鈴問題在高頻下也極易出現(xiàn),對SDRAM和DSP接口的控制信號和數(shù)據(jù)、地址總線信號,在源端串接匹配電阻以提高信號傳輸質(zhì)量,保證SDRAM在高頻下能正常工作。

4、數(shù)模電路的隔離處理

控制板卡上有數(shù)字電路和模擬電路,在布局時,必須考慮數(shù)模電路的隔離問題,盡量將數(shù)字電路和模擬電路分塊布局,避免數(shù)字信號走線跨越模擬電路區(qū)域,以防止兩塊電路間的相互干擾。另外數(shù)字電路和模擬電路通過0歐電阻一點共地。

5、電容的使用

在每個數(shù)字芯片的電源引腳旁邊放置一個1.01uF的去耦電容。

4 總結(jié)

本系統(tǒng)將高速PCI總線與C6000高速DSP處理器相結(jié)合,配以高精度的數(shù)模轉(zhuǎn)換模塊,實現(xiàn)了一套高速高精度的控制系統(tǒng),并將其成功的運用到振鏡激光標(biāo)記系統(tǒng)。該系統(tǒng)充分利用了DSP的高速處理能力和內(nèi)部的高精度定時器,分擔(dān)了PC機的實時性任務(wù),從而實現(xiàn)了PC機與DSP控制板卡的優(yōu)勢互補,實現(xiàn)了實時性標(biāo)記,保證了標(biāo)記質(zhì)量的均勻性。本文還給出了DSP控制板卡在PCB設(shè)計階段的注意點,該板卡已在生產(chǎn)實際中投入使用,具有較好的穩(wěn)定性和抗干擾性。

參考文獻:

[1] 王念旭. DSP基礎(chǔ)與應(yīng)用系統(tǒng)設(shè)計[M] . 北京:北京航空航天大學(xué)出版社,2003.

[2] 徐文,王峻峰. 基于DSP和AD7846的高精度控制系統(tǒng)[J] 微計算機信息,2006,2:173-175

[3] 李方慧,王飛,何佩琨 . TMS320C6000 系列DSPs 的原理與應(yīng)用[M] . 北京:電子工業(yè)出版社,2003.

[4] TMS320C62x Multichannel Evaluation Module User’s Guide. PDF. Texas Instruments Incorporated, 2004.

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。