1. 引言

隨著通訊系統(tǒng)的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

在密集型實時信號處理應用中,DSP 由于其本身結構特點具有不可替代的位置。但是遺憾的是目前很多DSP不具有RapidIO 接口,而且也沒有ASIC 能夠為這些DSP提供RapidIO接口。為了在RapidIO 網絡中充分利用DSP 數據處理的優(yōu)勢,我們采用FPGA 做一個轉接橋邏輯,將DSP 的總線連接到一個RapidIO 的IP 核,從而實現DSP 和RapidIO 網絡的互聯。

2. 總線結構概述

2.1 總線結構的演化

高速通信和超快速計算的需求日益增大,使得多處理器以及各種外部設備協同工作才能滿足實時快速的要求。傳統(tǒng)的系統(tǒng)中,這些處理器、處理器簇、外設之間的數據交互是基于并行的共享總線方式進行。從單分段總線到級聯的多分段總線,這些基于共享總線的體系結構中,所有的設備通訊競爭帶寬,這樣交互數據成為了整體系統(tǒng)性能的瓶頸。不僅如此,并行總線所需要的大量IO 引腳也給系統(tǒng)的電器性能和機械性能帶來相當的考驗。因此,提高系統(tǒng)性能就迫切需要一種新的體系結構。

目前新型的體系結構是基于點對點串行交換結構的體系。相比傳統(tǒng)的并行共享總線結構,串行交換結構中的兩個端點交互數據不影響其他端點之間的數據交互,從而大大提高了系統(tǒng)帶寬,除此之外,串行交換結構所需要的引腳也大大減少了,而且串行結構采用的差分線連接也提高了信號傳輸的距離和可靠性。當前流行的串行交換結構主要有PCI-Express,InfiniBand,RapidIO 等。這些總線結構的應用范圍既有交叉有各有側重。

2.2 RapidIO 交換結構

RapidIO 互連架構,它的設計與最流行的集成通信處理器、主機處理器以及網絡數字信號處理器相兼容,是高性能包交換互連技術。它滿足了高性能嵌入式系統(tǒng)行業(yè)對內部系統(tǒng)互連的需求,包括可靠性、高帶寬和更快的總線速率。相比PCI、PCI-X、PCIE 和Infiniband來說,RapidIO 主要特性是具有極低的延遲性和高帶寬,并很容易實現和PCI、PCI-X、PCIE、FPDP、以太網等的橋接,適合用于芯片與芯片、板與板、系統(tǒng)與系統(tǒng)之間的高速數據傳輸。

3. 系統(tǒng)設計

3.1 工程背景

多片 DSP 形成處理器簇,共同完成快速實時的運算已經成為現代信號處理機一種流行的方式。但是目前大多數DSP 都不具備RapidIO 接口,所以我們采用FPGA,將DSP 的總線與一個RapidIO IP 核總線相連接,實現DSP 與RapidIO 網絡的通信。

3.2 芯片選型

我們選用 Analog 的TigerShark101(以下簡稱TS101) DSP, ADSP-TS101S 是TigerSHARC 處理器系列中的首款器件。FPGA 選用Altera 的Stratix II GX 60 芯片。

Altera 的RapidIO 的IP 核兼容于2005 年2 月發(fā)布的RapidIO 互連標準1.3,實現了3種標準速度1.25G、2.5G、3.125G 下1x/4x 的物理層協議。同時,Altera 公司的SOPC 工具提供了大量的成熟的IP 核和可裁剪的Avalon 總線,方便的幫助用戶實現模塊化設計。

3.3 系統(tǒng)結構

將 TS101 的總線橋接到FPGA 的Avalon 總線上。其中,DSP 芯片是用來做大量的數據處理,FPGA 是DSP 和RapidIO 之間通訊的橋梁。FPGA 內的RapidIO 接口有成熟的IP 核,將DSP 和RapidIO 的IP 核連接的關鍵在于實現DSP 外部總線到IP 核Avalon 總線的轉換。

TS101 內部有一個寄存器SYSCON,用來控制外部端口、主機接口、多處理器接口的數據位寬、插入的等待周期、流水線深度等設置。由于這個寄存器在上電后只能修改一次,這里我們將外部端口配置位32 位的慢速協議,完成RapidIO 的維護,門鈴等事務;將主機接口配置位64 位的流水線協議,完成高速的IO 事務。通過轉接橋邏輯的轉換。

4. 轉接橋設計

4.1 轉接橋總體結構

轉接橋邏輯為 TS101 總線接口與Avalon 總線接口轉換器,由四個模塊及輔助電路構成。

4.2 總線模式控制電路

總線模式控制電路完成根據系統(tǒng)請求情況切換 TS101 總線端地址、數據以及相應的控制信號的輸入輸出方向、功能及狀態(tài)。其中需要控制的部分包括:數據總線的輸入輸出方向連接及模式控制,地址總線的輸入輸出方向連接及模式控制,TS101 的讀控制信號的輸入輸出方向連接及模式控制,TS101 的寫控制信號的輸入輸出方向連接及模式控制,TS101 的ACK 信號的輸入輸出方向連接及模式控制。另外,該模塊中還完成一些控制信號的連接。

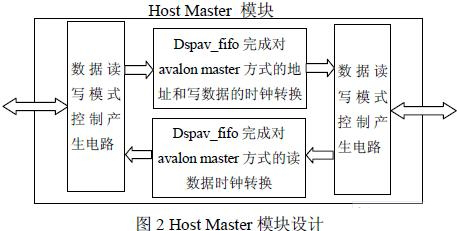

4.3 Host Master 模塊

Host_Master 模塊完成在系統(tǒng)工作于TS101 側控制模式時對Avalon 總線進行讀寫的總線時鐘切換和相關部分工作時的控制。它大致可分為四部分完成:

1. 數據讀寫控制產生電路在數據寫時根據輸入管腳中的片選信號、寫信號,將DSP 要寫入Avalon 總線的地址及數據寫入host_address_fifo 中。當是數據讀時,根據輸入管腳中的片選信號、讀信號,將DSP 要寫入Avalon 總線的地址寫入host_addrfifo 中,同時產生數據讀等待信號,當從host_readdata_fifo 總線讀到數據后,該電路撤銷讀等待信號,并將得到的數據送入TS101 的數據總線。

2. host_address_fifo 模塊完成在TS101 控制系統(tǒng)總線時,DSP 接口時鐘到Avalon 總線地址及寫入數據的換時鐘控制。

3. host_readdata_fifo 模塊完成在TS101 控制系統(tǒng)總線時,Avalon 總線到DSP 接口總線的讀入數據的換時鐘控制。

4. 數據讀控制狀態(tài)機電路部分完成TS101 的讀控制信號的產生,以及讀到的數據信號的存儲控制。

4.4 Avalon Master 模塊

Avalon_Master 模塊設計一個狀態(tài)機控制電路,完成在Avalon 總線上的地址、Byteenable、讀寫控制信號、讀數據信號和寫數據信號的產生與控制處理。同時還有等待讀數據到來以及讀數據確認工作。

4.5 Avalon Slave 模塊

Avalon_Slave 模塊是一個Avalon 總線的從設備,它可接收Avalon 總線上其它主設備發(fā)送過來的數據寫請求、數據讀請求,同時將從通過Host 接口讀到的數據按相應的總線規(guī)則送到數據總線上,同時產生數據有效信號。由于這里的設計采用可變讀等待設計,同時還需要完成對TS101 數據讀取換鐘轉換。該模塊主要由以下三部分構成:

1. ts101_slave_address_fifo 模塊模塊完成在Avalon 總線上的主設備控制系統(tǒng)總線時,Avalon 總線到DSP 總線的地址及寫入數據的換時鐘控制。

2. ts101_slave_readdata_fifo 模塊模塊完成在Avalon 總線上的主設備控制系統(tǒng)總線時,DSP 總線到Avalon 總線的讀入數據的換時鐘控制。

3. 數據讀控制電路部分完成讀數據的確認以及讀值有效信號的產生。

4.6 Host Slave 模塊

Host_Slave 模塊為一個控制狀態(tài)機電路,它根據Avalon_Slave 模塊提供的信號完成對DSP 的主總線控制請求,帶發(fā)送信號的組織,發(fā)送和接收信號的確認接收,包括產生HBRN信號,并根據HBGN 信號的狀態(tài)產生讀寫控制信號、讀寫地址信號、寫數據信號以及從DSP中讀回待接收的讀數據信號。

5. 功能測試

目前,Altera 的RapidIO IP 核支持的RapidIO 事務有:讀操作NREAD 請求和響應,寫操作NWRITE 請求,帶響應的寫操作NWRITE_R 請求和響應,流寫(SWRITE)請求,維護(MAINTENANCE)讀請求和相應,維護(MAINTENANCE)寫請求和響應,維護(MAINTENANCE)端口寫請求,門鈴(DOORBELL)請求和相應。在實際的測試中,將這個電路板和Mercury 公司Ensemble MPQ-101 同時安裝在Silicontkx 的串行RapidIO 開發(fā)平臺上,結果證實DSP 通過轉接橋邏輯控制RapidIO IP 核,已經實現了所有的這些事務。

6. 總結和展望

RapidIO 作為下一代嵌入式互聯技術,在國內的信號處理平臺上的運用越來越廣泛。但是目前很多處理芯片不具有RapidIO 的接口。利用FPGA可以方便快速定制一個合適的接口,為RapidIO 網絡增添各種豐富的節(jié)點。同時,本文給出了實現這個轉接橋的思路做了詳細討論,這樣不同的DSP,甚至CPU 都可以利用這種思路來接入RapidIO 網絡。

在目前的設計中,一個 FPGA 為一個DSP 提供轉接橋邏輯,過于浪費FPGA 的資源。在緊接下來的設計中,我們將4 片DSP 組成一簇接入FPGA,從而提高單板的處理能力,同時提高了FPGA 的利用率。