摘 要:提出一種基于SOPC的數(shù)據(jù)發(fā)生系統(tǒng)及其PCI接口的設(shè)計方案,詳細介紹了系統(tǒng)主要模塊的硬件設(shè)計方法,實現(xiàn)SOPC系統(tǒng)中定制用戶自定義主從外設(shè)及其通過相應(yīng)的主從端口與Avalon。總線的連接,并在EDA工具QuartusⅡ和ModelSim平臺上用硬件描述語言VHDL語言對該方案中的基本模塊,如數(shù)據(jù)產(chǎn)生,乒乓結(jié)構(gòu)和PCI9054接口邏輯進行了邏輯綜合及功能仿真。可以在本系統(tǒng)的基礎(chǔ)上,通過軟件的完善,實現(xiàn)復(fù)雜的非常規(guī)類型數(shù)據(jù)的產(chǎn)生,提高了系統(tǒng)的適應(yīng)性和靈活性,有利于參數(shù)的修改和系統(tǒng)升級。

關(guān)鍵詞:SOPC;Avalon總線;乒乓結(jié)構(gòu);PCI9054

0 引 言

可編程片上系統(tǒng)(SOPC)是一種特殊的嵌入式系統(tǒng),因為SOPC是片上系統(tǒng)(SoC),即由單個芯片完成整個系統(tǒng)的主要邏輯功能;SOPC是可編程系統(tǒng),具有靈活的設(shè)計方式,可裁減,可擴充,可升級,并具備軟硬件在系統(tǒng)可編程的功能;SOPC結(jié)合了SoC和FPGA的優(yōu)點,涵蓋了嵌入式系統(tǒng)設(shè)計技術(shù)的全部內(nèi)容;SOPC涉及目前已引起普遍關(guān)注的軟硬件協(xié)同設(shè)計技術(shù)。

現(xiàn)以數(shù)據(jù)發(fā)生系統(tǒng)為例,介紹采用SOPC技術(shù),以硬件描述語言為主要手段,產(chǎn)生偽隨機序列的設(shè)計方案。研究了偽隨機序列的產(chǎn)生,兩片SRAM乒乓結(jié)構(gòu)存儲以及通過PCI9054芯片與PC機之間數(shù)據(jù)傳遞等模塊的硬件實現(xiàn)問題。

1 基本原理和系統(tǒng)的整體結(jié)構(gòu)

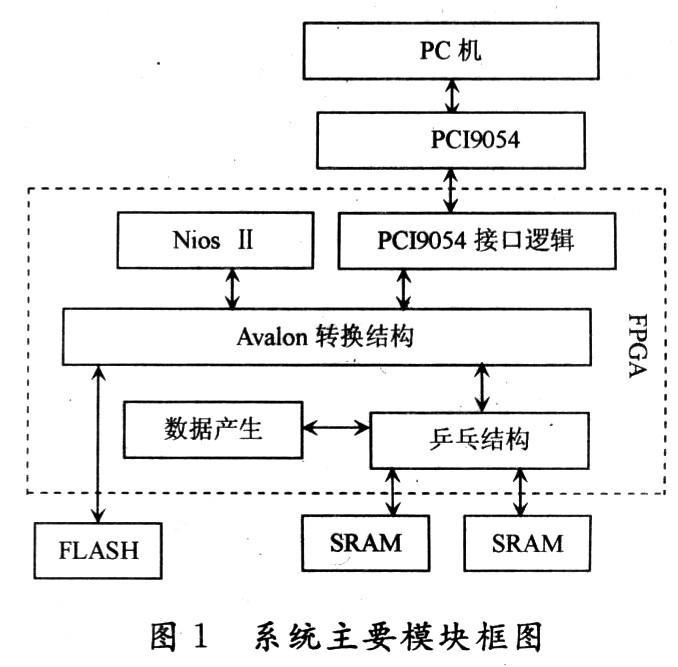

本系統(tǒng)的主要模塊框圖如圖1所示,SOPC系統(tǒng)采用Altera的CycloneⅡ系列的芯片。系統(tǒng)包括NiosⅡ軟核處理器,擴展的程序存儲器FLASH,數(shù)據(jù)存儲器SRAM,以及用戶自定義邏輯如PCI9054接口邏輯模塊、數(shù)據(jù)產(chǎn)生模塊、乒乓結(jié)構(gòu)模塊等,并通過Avalon總線連接起來。數(shù)據(jù)產(chǎn)生模塊產(chǎn)生偽隨機序列,該數(shù)據(jù)存儲到兩片片外擴展的SRAM中,PCI9054接口邏輯將數(shù)據(jù)從SRAM中讀出后通過PCI9054接口芯片傳輸?shù)絇C機中,其中SRAM中數(shù)據(jù)的寫入和讀出是通過乒乓結(jié)構(gòu)模塊控制的。

由于PCI總線協(xié)議比較復(fù)雜,該系統(tǒng)采用PCI接口專用芯片PCI9054,用于PCI總線的控制。為了實現(xiàn)數(shù)據(jù)的高速傳輸,采用了DMA傳輸模式。在該模式中,PCI9054既是PCI總線的控制器又是本地總線的控制器,所以其與FPGA之間的接口邏輯模塊設(shè)置為AvaIon主外設(shè),控制SRAM的讀操作。

FPGA的片上資源很寶貴,所以數(shù)據(jù)的存儲采用了片外擴展SRAM。由于數(shù)據(jù)為16 b,而且為實現(xiàn)數(shù)據(jù)的高速傳輸,采用了兩片256K x 16 b的SRAM(IDT71V416)構(gòu)成乒乓結(jié)構(gòu),以用作系統(tǒng)的數(shù)據(jù)存儲器。為保證整個系統(tǒng)高速運行以及以后升級的需要,選用了存取時間為10 ns的IDT71V416。

2 系統(tǒng)主要硬件設(shè)計

2.1 數(shù)據(jù)產(chǎn)生模塊

該模塊的邏輯功能由VHDL語言設(shè)計實現(xiàn),可以通過修改該模塊的設(shè)計產(chǎn)生所需要的數(shù)據(jù),本系統(tǒng)產(chǎn)生的數(shù)據(jù)為偽隨機序列。模塊的邏輯功能是:先產(chǎn)生8 b的偽隨機數(shù),再將所產(chǎn)生的數(shù)據(jù)通過D觸發(fā)器組合成16 b的數(shù)據(jù)。該系統(tǒng)采用了非線性反饋的移位寄存器,即全狀態(tài)移位計數(shù)器來產(chǎn)生所需要的偽隨機數(shù)。這種計數(shù)器利用了移位寄存器的所有狀態(tài),能夠自啟動,不需要額外輸入。這種偽隨機序列發(fā)生器,可大大簡化結(jié)構(gòu),提高可靠性,易于實現(xiàn)。

全狀態(tài)移位計數(shù)器的狀態(tài)變化規(guī)律有兩個特點:狀態(tài)的最高位由反饋函數(shù)確定;余下的各位由原態(tài)移位得到。該系統(tǒng)采用的反饋函數(shù)為:

![]()

式中:Qi(i=1,…,8)為電路的現(xiàn)態(tài)。

2.2 乒乓結(jié)構(gòu)模塊

2.2.1 乒乓結(jié)構(gòu)的硬件實現(xiàn)

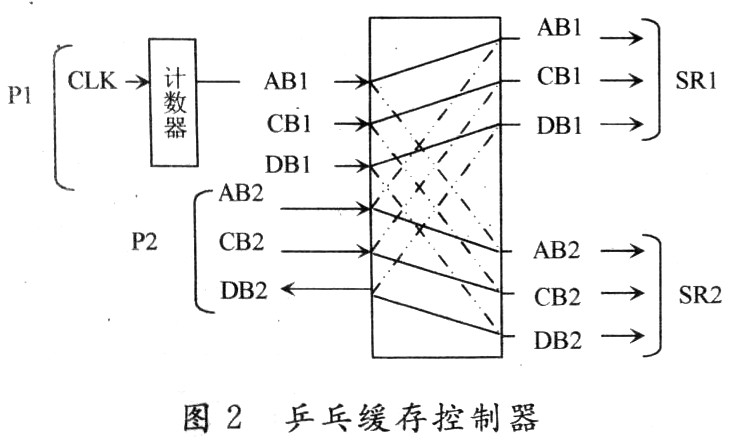

為了提高系統(tǒng)的傳輸速率,兩片SRAM構(gòu)成了乒乓緩存結(jié)構(gòu),即在一片執(zhí)行寫操作的同時,另一片在執(zhí)行讀操作。乒乓結(jié)構(gòu)模塊的原理如圖2所示,P1口與數(shù)據(jù)產(chǎn)生模塊相連接,僅具有寫入功能,P2口設(shè)計為Avalon從端口,與Avalon總線相連僅具有讀出功能。

對于數(shù)據(jù)產(chǎn)生模塊而言,由于僅具有并行數(shù)據(jù)的輸出,沒有地址和控制信號端口,故它無法直接對SRAM進行寫操作,因而要求乒乓結(jié)構(gòu)模塊有地址產(chǎn)生功能。P1口的CLK作為計數(shù)器的脈沖源,計數(shù)器的輸出作為SRAM的地址。DBl連接數(shù)據(jù)產(chǎn)生模塊的輸出端。CBl為控制信號,因為P1口只有寫入功能,所以其we_n恒接低,oe_n恒接高。

P2口為只有讀出功能的Avalon從端口,所以AB2為從端口的地址線address;DB2為數(shù)據(jù)線readdata;CB2中的we_n為讀信號線read,oe_n恒接低。由于兩片SRAM始終處于工作狀態(tài),所以相應(yīng)的片選信號chip_select_n恒接低。

兩片SRAM在P1口和P2口之間的切換的控制信號即chipselect,由計數(shù)器產(chǎn)生。當(dāng)計數(shù)值小于262 144時,chipselect接低,SR1與P1口相接,SR2與P2口相接;當(dāng)計數(shù)值在262 144~524 288之間時,chipselecl接高,SR1與P2口相接,SR2與P1口相接。當(dāng)計數(shù)值到達524 288時,計數(shù)器清零。

2.2.2 Avalon從外設(shè)的端口信號設(shè)計

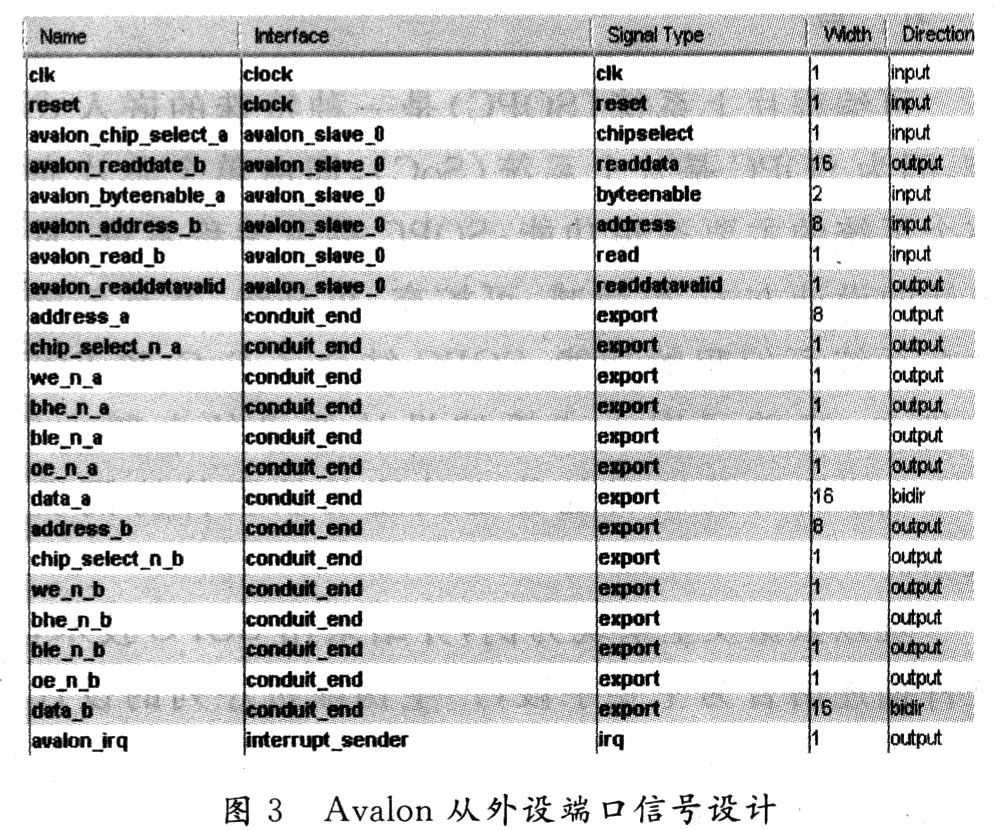

系統(tǒng)中,數(shù)據(jù)產(chǎn)生模塊與乒乓結(jié)構(gòu)模塊結(jié)合為一個模塊,通過P2口掛在Avalon總線上。該模塊的信號列表如圖3所示。其中,avalon_slave_O接口類型的信號與Avalon總線相連接,而conduit_end接口類型的信號與SRAM相連接。圖3中的Avalon從端口即為P2口,采用了流水線讀傳輸?shù)哪J剑@種模式能在前一次傳輸返回readdata前開始一次新的傳輸,增加了帶寬。

2.2.3 動態(tài)地址對齊及其時許設(shè)計

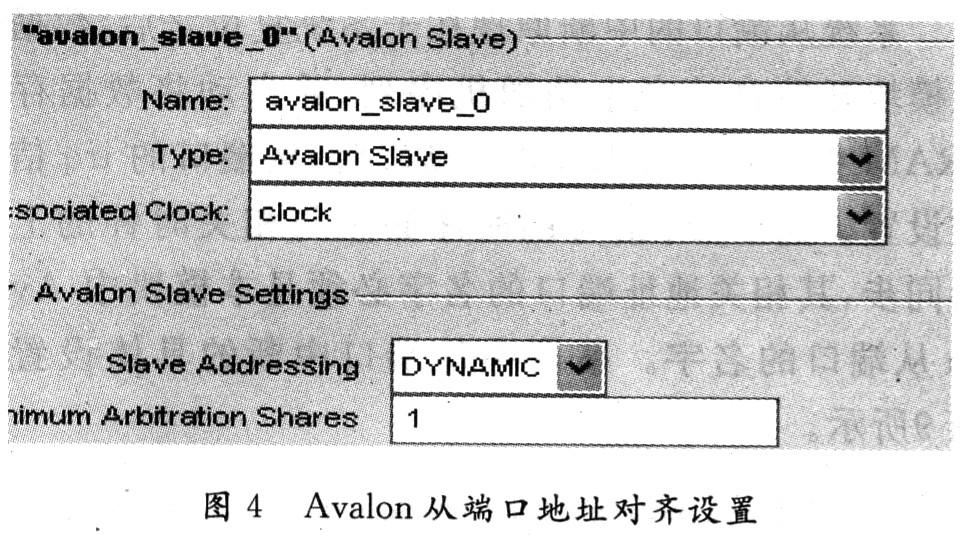

Avalon總線模塊能夠適應(yīng)主從外設(shè)的不同寬度和不匹配的數(shù)據(jù)寬度。當(dāng)系統(tǒng)中村子不匹配的存儲口時,要考慮地址對齊問題。對于存儲器類型的外設(shè),采用動態(tài)地址對齊方式。IDT71V416型SRAM是靜態(tài)RAM,屬于存儲器型外設(shè),所以該Aalon從端口采用動態(tài)地址對齊方式,如圖4所示。選用動態(tài)地址對齊方式,使得主端口能連續(xù)地對從外設(shè)進行讀寫,并使系統(tǒng)將外設(shè)認作存儲器型外設(shè)。

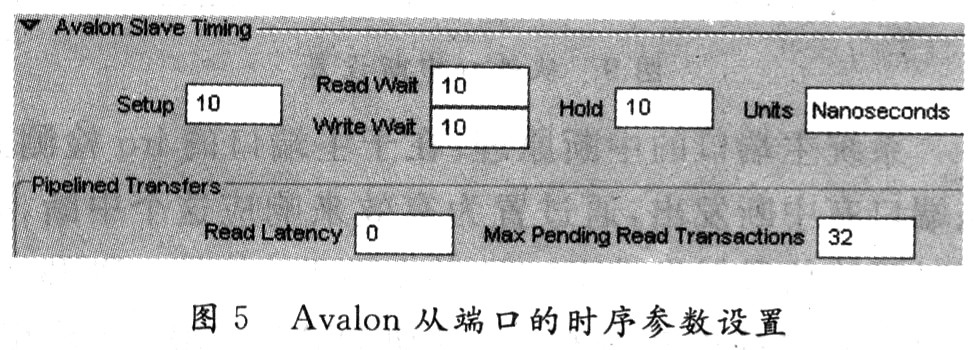

根據(jù)IDT71V416型SRAM手冊中讀寫時序的各時間參數(shù)值設(shè)定set up,read wait,write wait及holdtime的時間均為10 ns,使該端口既符合Avalon總線讀寫時序的要求,又符合IDT71V416型SRAM的讀寫時序的要求,如圖5所示。

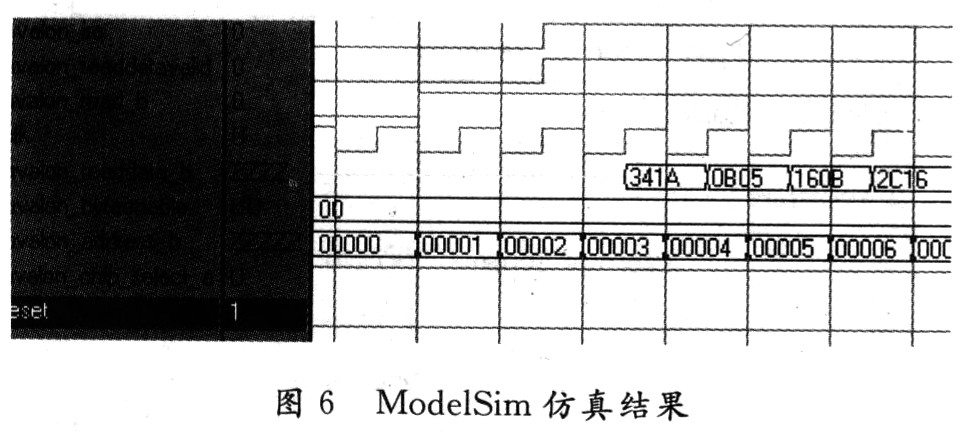

數(shù)據(jù)產(chǎn)生,乒乓結(jié)構(gòu)和兩片SRAM三部分的組合在ModelSim中的仿真結(jié)果如圖6所示。avalon_ad-dress_b不變時是在執(zhí)行第一次寫操作,此時沒有數(shù)據(jù)讀出,所以avalon_readdata_b值為高阻;avalon_ad-dress_b開始變化時,表示一片SRAM已經(jīng)寫滿,正在執(zhí)行該片的讀操作,而另一片在執(zhí)行寫操作,avalon_readdata_b為系統(tǒng)生成的數(shù)據(jù)。

2.3 PCI9054接口邏輯模塊

PCI總線作為PC機與外部設(shè)備之間重要的連接總線,具有數(shù)據(jù)傳輸穩(wěn)定靈活,傳輸速度快,即插即用和良好的擴展性等特點,被廣泛地用在各種與PC機互聯(lián)的設(shè)備中。該系統(tǒng)采用的PCI9054芯片口可以將復(fù)雜的PCI總線接口轉(zhuǎn)換為相對簡單的用戶接口,大大縮短了設(shè)計周期。

2.3.1 本地總線狀態(tài)機設(shè)計

由于PCI9054的DMA傳輸方式只適宜于做單次傳輸,故該系統(tǒng)采用了DMA結(jié)合中斷的方式傳輸數(shù)據(jù)。由于數(shù)據(jù)的存儲采用了乒乓結(jié)構(gòu),可以在一片SRAM執(zhí)行DMA傳輸?shù)耐瑫r執(zhí)行另一片寫操作,這樣不會造成數(shù)據(jù)丟失,狀態(tài)也比較容易控制。

系統(tǒng)復(fù)位后,數(shù)據(jù)產(chǎn)生模塊開始產(chǎn)生偽隨機序列,產(chǎn)生的數(shù)據(jù)直接存入SRAM中。此時,計數(shù)器同步計數(shù),當(dāng)計數(shù)值每一次達到262 144時,也就是一片SRAM已經(jīng)存滿時,SOPC系統(tǒng)就會觸發(fā)PCI9054中斷請求信號LINT#,CPU響應(yīng)中斷,發(fā)出讀命令、要讀取的字節(jié)數(shù)、地址信號等。PCI9054:先通過LHOLD申請本地總線的控制權(quán),SOPC系統(tǒng)通過LHOLDA響應(yīng),使PCI9054.獲得本地總線的控制權(quán)。PCI9054將PCI地址空間映射到本地地址空間,接著啟動本地總線的DMA傳輸。

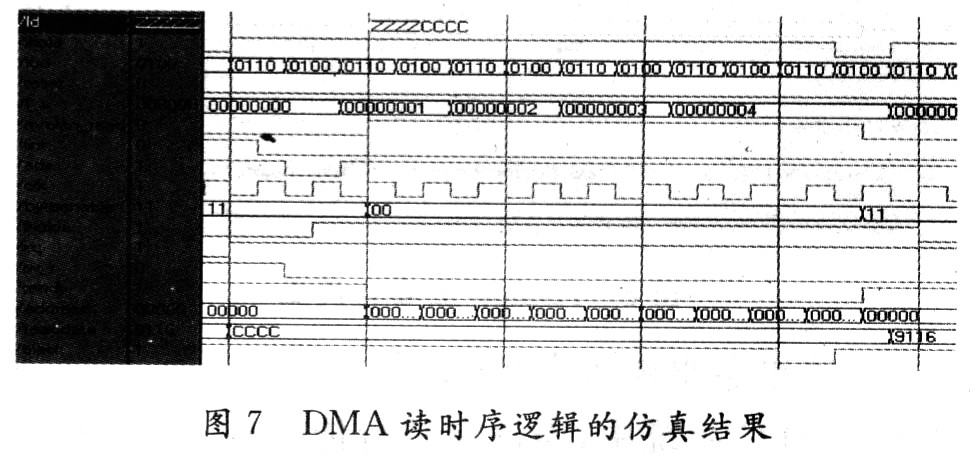

該系統(tǒng)采用VHDL語言,實現(xiàn)了DMA讀傳輸本地端的時序控制狀態(tài)機設(shè)計。狀態(tài)0為空閑狀態(tài)(i-dle),若LHOLD信號被置1,則轉(zhuǎn)到狀態(tài)1,否則留在狀態(tài)0。狀態(tài)1為總線保持狀態(tài)(hold),在此狀態(tài)下應(yīng)將LHOLDA信號置l。如果信號ADs為O且LW_R為0,則轉(zhuǎn)到狀態(tài)2。狀態(tài)2為DMA讀狀態(tài)(DMA_read),在此狀態(tài)下應(yīng)將READY信號和模塊內(nèi)部信號avaIon_read置l,從而使AvaIon主端口的master_read置1,表示Avalon主外設(shè)發(fā)起讀傳輸。如果BLAST為1,則表明此次DMA讀取還沒有完成,繼續(xù)留在狀態(tài)2;如果BLAsT為0,則表明此次DMA讀取完成,轉(zhuǎn)到狀態(tài)3。狀態(tài)3為DMA讀操作完成狀態(tài)(end cycle),當(dāng)LHOLD被置0時,表示PCI9054不再請求本地總線,則轉(zhuǎn)到狀態(tài)0;當(dāng)BLAST為0且LHOLD為1時,則表明PCI9054還要進行DMA讀操作,則轉(zhuǎn)到狀態(tài)1繼續(xù)。其中的DMA讀操作的時序邏輯的ModelSim仿真結(jié)果如圖7所示。

2.3.2 Avalon主外設(shè)的端口信號設(shè)計

該系統(tǒng)中,PCI9054控制數(shù)據(jù)從本地總線上讀出,先到PCI9054的FIFO中,再將FIFO中的數(shù)據(jù)傳輸?shù)絇CI總線上。因此SOPC系統(tǒng)中的PCI9054接口邏輯模塊為Avalon主外設(shè),主端口通過address,read,wait-request等信號發(fā)起Avalon總線上的讀操作,從而控制Avalon從外設(shè)即乒乓結(jié)構(gòu)模塊的讀操作。

由于本系統(tǒng)定制的從外設(shè)采用了流水線讀的傳輸模式,為了使端口傳輸模式匹配,主外設(shè)也采用流水線讀的傳輸模式。流水線主端口一個必須的信號為readdatavalid,Avalon交換結(jié)構(gòu)向主端口發(fā)出readdat-avalid,以表示readdata信號正在提供有效的數(shù)據(jù)。

本系統(tǒng)定制的Avalon主外設(shè)構(gòu)成模塊主要由5部分構(gòu)成,其中Read Master Logic提供了符合Aval-on接口規(guī)范的主端口信號;Control Logic是ReadMaster Logic與PCI9054 Local Bus Logic控制信號和狀態(tài)信號轉(zhuǎn)換的橋梁;FIFO是數(shù)據(jù)由Read MasterLogic向PCI9054傳輸?shù)木彌_區(qū)。這三部分通過主端口流水線讀傳輸時序邏輯聯(lián)系在一起,提供了Avalon主外設(shè)的主端口接口界面。PCI9054 Local Bus Logic即VHDL語言設(shè)計的本地總線狀態(tài)機,它將PCI9054本地端的信號通過狀態(tài)機邏輯轉(zhuǎn)換為與Control Logic和FIFO相對應(yīng)的信號;Clock/Reset提供了主外設(shè)的clk和reset信號。

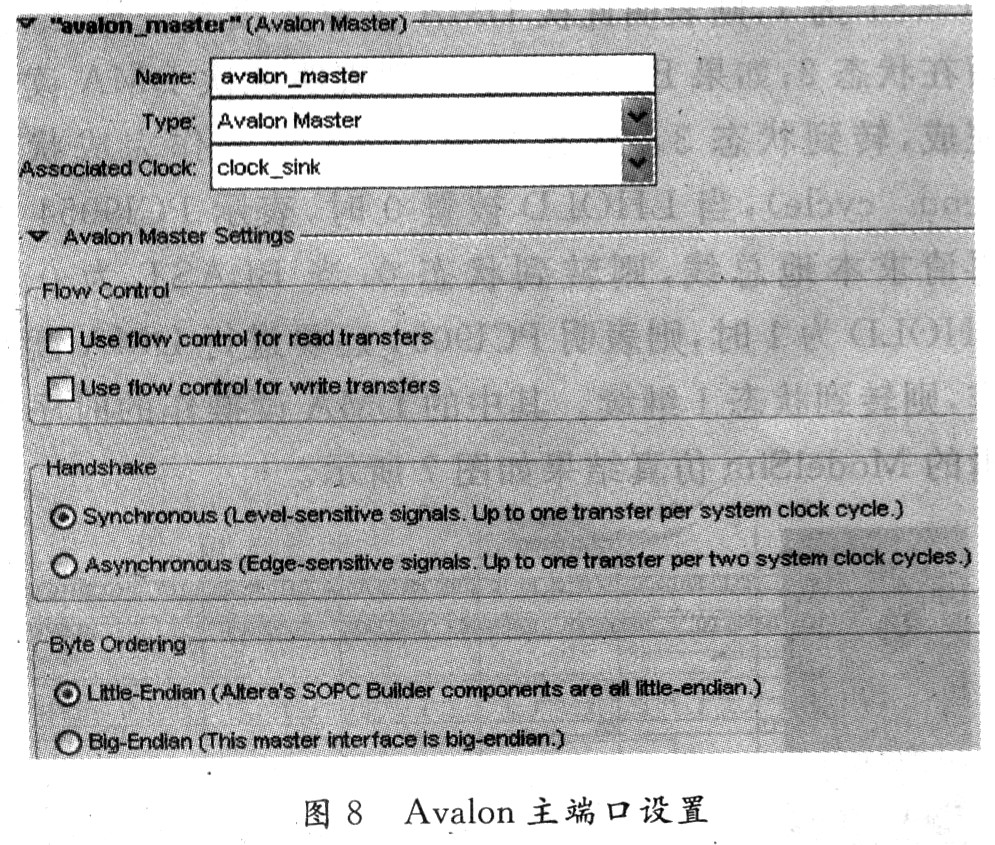

利用SOPC Builder中的new cormponent edit設(shè)計PCI9054接口邏輯模塊的接口。在new component ed-it的signal中設(shè)置模塊的各信號線以及相應(yīng)的總線型號類型;在interface中設(shè)置各信號線對應(yīng)的端口類型及其相應(yīng)的參數(shù)。圖8為Avalon主端口的參數(shù)設(shè)置。

2.4 系統(tǒng)中各中斷的實現(xiàn)

在SOPC系統(tǒng)中,當(dāng)沒有進行傳輸時,Avalon交換結(jié)構(gòu)忽略來自主端口所有與傳輸相關(guān)的輸出信號,并且主端口也忽略來自Avalon交換結(jié)構(gòu)所有與傳輸相關(guān)的輸入信號。但是Avalon總線接口提供控制信號來實現(xiàn)中斷請求等功能,這些信號不直接與數(shù)據(jù)傳輸相關(guān)。Avalon中斷請求信號允許從端口發(fā)出一個IRQ,表明它需要主外設(shè)來服務(wù)。系統(tǒng)中,PCI9054采用了DMA加中斷的方式來傳輸數(shù)據(jù),而且DMA傳輸中的主控制器PCI9054芯片也要通過中斷信號LINT#來觸發(fā),所以中斷的實現(xiàn)是本系統(tǒng)功能實現(xiàn)的關(guān)鍵。

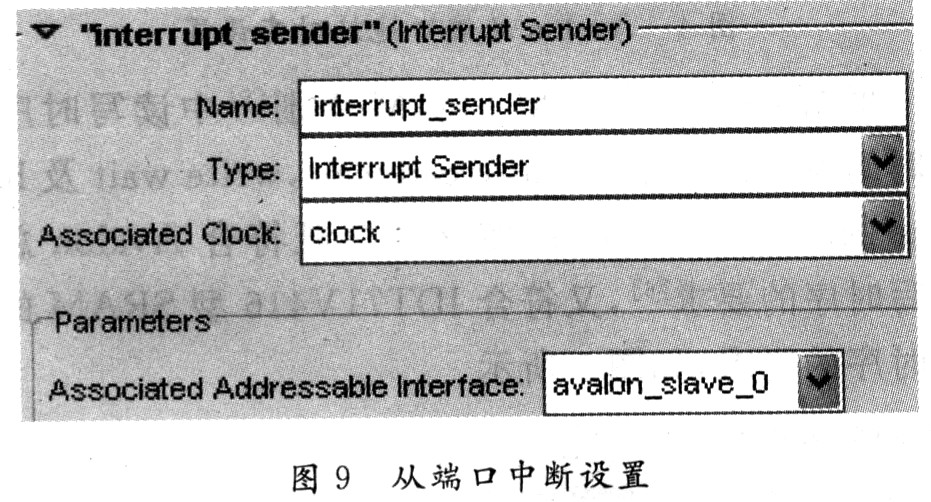

系統(tǒng)從端口的中斷原理在于系統(tǒng)復(fù)位之后,數(shù)據(jù)產(chǎn)生模塊開始自動產(chǎn)生偽隨機序列,并自動將數(shù)據(jù)存入SRAM中,當(dāng)一片SRAM存滿之后,從端口的irq信號被設(shè)置。這個irq信號的時序必須與相關(guān)時鐘的上升沿同步,其相關(guān)地址端口的名字必須是本模塊中Aval-on從端口的名字。系統(tǒng)中從端口中斷的具體設(shè)置如圖9所示。

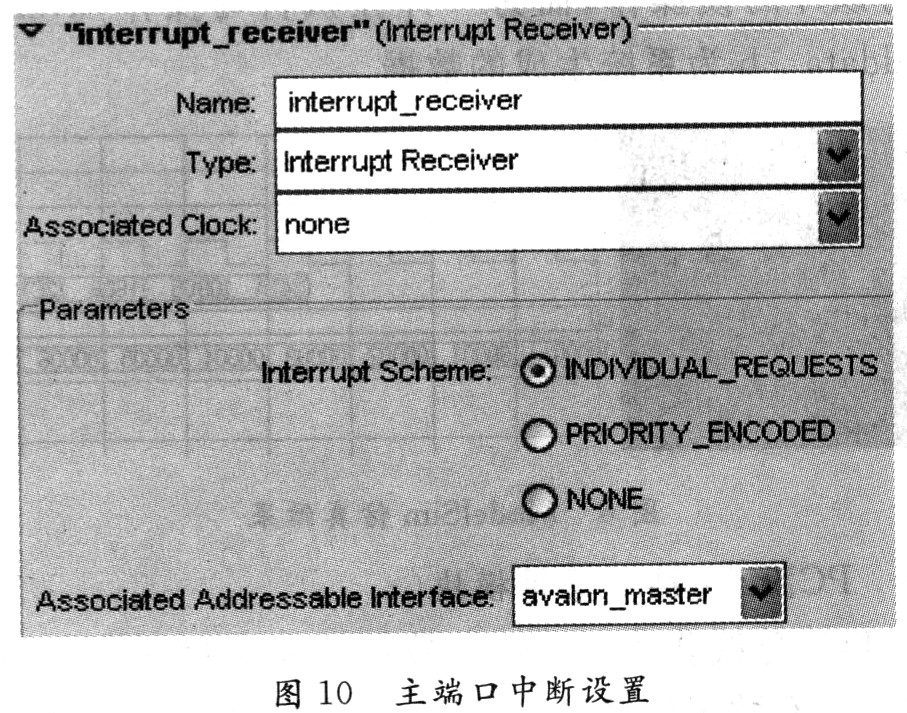

系統(tǒng)主端口的中斷原理:在于主端口的irq檢測到從端口有中斷發(fā)出,通過置為有效來響應(yīng)這個中斷,并同時用該信號觸發(fā)PCI9054的LINT#信號。PCI9054獲得本地總線的控制權(quán),并啟動DMA傳輸,向SOPC:系統(tǒng)中的主外設(shè)即PCI9054接口邏輯模塊發(fā)送地址和傳輸?shù)淖止?jié)長度,開始DMA傳輸。當(dāng)字節(jié)長度減為O,另一片SRAM存滿時,再次觸發(fā)PCI9054的LINT#信號,使得PCI9054啟動下一次DMA傳輸。主端口中斷的設(shè)置如圖10所示。

3 結(jié) 語

圖10 主端口中斷設(shè)置詳細介紹了基于SOPC設(shè)計的數(shù)據(jù)發(fā)生系統(tǒng)中PCI接口的開發(fā)過程。對其中的關(guān)鍵技術(shù),如設(shè)計添加在SOPC系統(tǒng)中的用戶自定義主外設(shè)和從外設(shè);PCI9054本地總線狀態(tài)機的設(shè)計,乒乓結(jié)構(gòu)的存儲模塊的設(shè)計,以及系統(tǒng)中各中斷的實現(xiàn)等主要部分做了分析和研究,給出了基于SOPC的硬件實現(xiàn)方案。系統(tǒng)的主要部分由VHDL語言設(shè)計實現(xiàn),有利于參數(shù)修改和系統(tǒng)升級。