在數(shù)字圖像處理、航空航天等高速信號處理應(yīng)用場合,需要有高速大容量存儲空間的強力支持,來滿足系統(tǒng)對海量數(shù)據(jù)吞吐的要求。通過使用大容量同步動態(tài)RAM(SDRAM" title="SDRAM">SDRAM)來擴展嵌入式DSP" title="DSP">DSP系統(tǒng)存儲空間的方法,選用ISSI公司的IS42S16400高速SDRAM芯片,詳細(xì)論述在基于TMS320C6201(簡稱C6201)的數(shù)字信號處理系統(tǒng)中此設(shè)計方法的具體實現(xiàn)。

1 IS42S16400芯片簡介

IS42S16400是ISSl公司推出的一種單片存儲容量高達(dá)64 Mb(即8 MB)的16位字寬高速SDRAM芯片。SDRAM的主要特點是:①同步訪問,讀寫操作需要時鐘;②動態(tài)存儲,芯片需要定時刷新。IS42S16400采用CMOS工藝,它的同步接口和完全流水線的內(nèi)部結(jié)構(gòu)使其擁有極大的數(shù)據(jù)傳輸速率,可以工作在高達(dá)133 MHz的時鐘頻率下,刷新頻率每64 ms為4096次。該SDRAM芯片內(nèi)部有4個存儲體(bank),通過行、列地址分時復(fù)用系統(tǒng)地址總線,對不同存儲體內(nèi)不同頁面的具體存儲單元進(jìn)行讀寫訪問尋址。在進(jìn)行讀操作之前,必須預(yù)先激活SDRAM內(nèi)對應(yīng)的存儲體,并選擇存儲器的某一行,然后送人列地址讀取需要的數(shù)據(jù)。從輸出列地址到SDRAM返回相應(yīng)數(shù)據(jù)之間存在一個存取延遲。如果訪問新的頁面,則先需要關(guān)閉所有的存儲體,否則已打開的頁面將一直有效。在寫操作之前,由于已經(jīng)預(yù)先激活了有關(guān)的行地址,因此可以在輸出列地址的同時輸出數(shù)據(jù),沒有延遲。IS42S16400提供自刷新模式的設(shè)置,可以使芯片運行在低功耗的狀態(tài)下,從而大大減少嵌入式系統(tǒng)的功率消耗。

2 C6201與SDRAM的外部存儲器接口

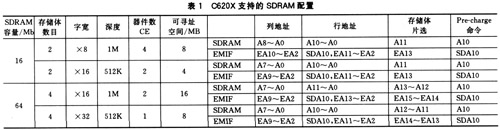

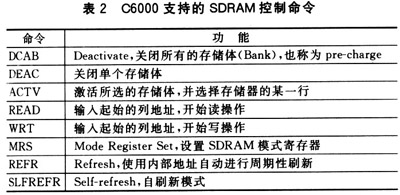

DSP芯片訪問片外存儲器時必須通過外部存儲器接口EMlF(External Memory Interface)。C6000系列DSPs的EMIF" title="EMIF">EMIF具有很強的接口能力,不僅具有很高的數(shù)據(jù)吞吐率(最高達(dá)1200 MB/s),而且可以與目前幾乎所有類型的存儲器直接接口。在C6201系統(tǒng)中,提供了4個彼此獨立的外存接口(CEX)。除CEl空間只支持異步接口外,所有的外部CEx空間都支持對SDRAM的直接接口。表1總結(jié)了C620XDSPs的EMIF所兼容的SDRAM配置。表2給出了C6000系列DSPs的EMIF所支持的SDRAM控制命令。

2.1 SDRAM的刷新

為了提高存儲容量,SDRAM采用硅片電容來存儲信息。隨著時間的推移,必須給電容重新充電才能保持電容里的數(shù)據(jù)信息,這就是所謂的“刷新”。它的存在也使得SDRAM的應(yīng)用變得略顯復(fù)雜,帶來了一定的應(yīng)用難度。

C6000系列DSPs有專門的SDRAM控制寄存器(SDTCL)和SDRAM時序控制寄存器(SDTIM),用來進(jìn)行SDRAM的各種時序控制,大大減輕了設(shè)計人員的開發(fā)難度。SDCTL寄存器中的RFEN位控制是否由EMIF完成對SDRAM的刷新。如果RFEN=1,EMIF會控制向所有的SDRAM空間發(fā)出刷新命令(REFR);而SDTIM寄存器中的PERIOD位段則控制具體的刷新周期。

在REFR命令之前,會自動插入一個DCAB命令,以保證刷新過程中所有的SDRAM都處于未激活狀態(tài)。DCAB命令之后,EMIF開始按照SDTIM寄存器中PERD字段設(shè)置的值進(jìn)行定時刷新。刷新前后,頁面信息會變?yōu)闊o效。

對于C620X,EMIF SDRAM控制模塊內(nèi)部有一個2位的計數(shù)器,用來監(jiān)測提交的刷新申請的次數(shù)。每提交一個申請,計數(shù)器加1;每次刷新周期之后,計數(shù)器減1。復(fù)位時,計數(shù)器自動置為11b,以保證在存取訪問之前先進(jìn)行若干次刷新。計數(shù)器的值為llb,代表緊急刷新狀態(tài),此時頁面信息寄存器變無效,迫使控制器關(guān)閉當(dāng)前的SDRAM頁面。然后,EMIF SDRAM控制器在DCAB命令后執(zhí)行3次REFR命令,使計數(shù)器的值減為0,再繼續(xù)完成余下的存取操作。

2.2 SDRAM的初始化

當(dāng)某個CE空間配置為SDRAM空間后,必須首先進(jìn)行初始化。用戶不需要控制初始化的每一個步驟,只需要向EMIF SDCTL寄存器的INIT位寫1,申請對SDRAM作初始化。然后,EMIF就會自動完成所需要的各步操作。初始化操作不能在進(jìn)行SDRAM存取過程中進(jìn)行。整個初始化過程包括下面幾個步驟:

①對所有的SDRAM空間發(fā)出DCAB命令;

②執(zhí)行3個REFR命令;

③對所有的SDRAM空間發(fā)出MRS命令。

2.3頁面邊界控制

SDRAM屬于分頁存儲器,EMIF的SDRAM控制器會監(jiān)測訪問SDRAM時行地址的情況,避免訪問時發(fā)生行越界。為了完成這一任務(wù),EMIF在內(nèi)部有四個頁面寄存器,自動保存當(dāng)前打開的行地址,然后與后續(xù)存取訪問的地址進(jìn)行比較。需要說明的是,當(dāng)前存取操作結(jié)束并不會引起SDRAM中已經(jīng)激活的行被立即關(guān)閉,EMIF的控制原則是維持當(dāng)前的打開狀態(tài),除非必須關(guān)閉。這樣做的好處是可以減少關(guān)閉/重新打開之間的命令切換時間,使接口在存儲器訪問的控制過程中充分利用地址信息。

對于C620X,每個CE空間包含1個頁面寄存器(只對配置為SDRAM空間有效),因此C620X每個CE空間1次只能激活1頁。進(jìn)行比較的地址位數(shù)取決于SDCTL寄存器中SDWID位的值。如果SDWID=O,該CE空間構(gòu)成頁面的大小為512,比較的邏輯地址是位23~11;如果SDWID=1,該CE空間SDRAM構(gòu)成頁面的大小為256,比較的邏輯地址是位23~10。一旦發(fā)現(xiàn)存取訪問發(fā)生了頁面越界,EMIF會自動執(zhí)行DCAB操作,然后再開始新的行訪問。

2.4訪問地址的移位

由于SDRAM行邏輯地址與列邏輯地址復(fù)用相同的EMIF 引腳,所以EMIF接口需要對行地址與列地址進(jìn)行相應(yīng)的移位處理。地址的移位處理由SDCRL寄存器中的SDWlD位控制。 另外,對于SDRAM,因為輸入地址也是控制信號,因此需要說明以下幾點:

①RAS有效期間的高位地址信號會被EMIF內(nèi)部SDRAM控制器鎖存,以保證執(zhí)行READ和WRT命令時選通正確的bank;

②READ/WRT操作期間,EMIF會保持pre-charge信號為低(C620X是SDAl0),以防止READ/WRT命令執(zhí)行后發(fā)生auto pre—charge操作。

2.5接口時序的設(shè)計

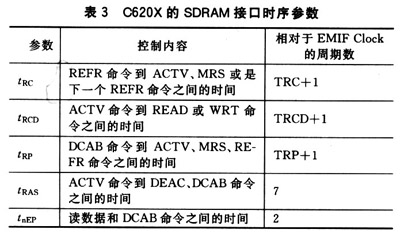

對于C620X,EMIF與SDRAM的接口時序由SDCTL寄存器控制。EMIF提供了5個時序參數(shù),其中3個在SDCTL寄存器中設(shè)置,另外2個為固定值,如表3所列。在分析接口時序的配合情況時,需要計算“富裕時間”tmargin的大小,這是在考慮了SDRAM芯片的器件手冊提供的最壞情況之后,得到的時序上的一個裕量。至于tmargin值的大小,是系統(tǒng)設(shè)計層需要考慮的問題,具體要求隨不同的系統(tǒng)而異,而且與印制板的實際布線情況以及負(fù)載的情況密切相關(guān)。

3 系統(tǒng)設(shè)計中IS42S16400芯片的應(yīng)用

3.1 C6201與IS42S16400的接口實現(xiàn)

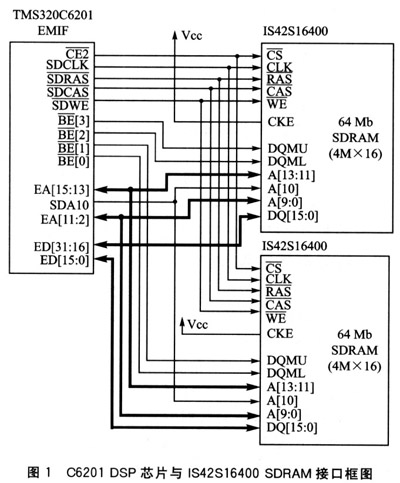

由于IS42S16400屬于16位字寬的64 Mb SDRAM芯片,而C6201的EMIF只提供32位字寬的同步外存儲接口,為了使整個系統(tǒng)的存儲空間保持連續(xù),使用2片SDRAM與DSP芯片組成實際大小為16 MB的外部存儲系統(tǒng),如圖1所示。圖1中IS42S16400芯片各引腳含義如下:CS,片選;CLK,系統(tǒng)同步時鐘;RAS,行地址選擇;CAS,列地址選擇;WE,讀/寫使能;CKE,時鐘使能;DQMU、DQML,高低字節(jié)使能;A[13:123],Bank地址選擇線;A[11:0],行、列地址線;DQ[15:0],雙向數(shù)據(jù)端口。

由圖1可以看出,雖然C620l提供32位地址尋址能力,但是經(jīng)EMIF直接輸出的地址信號只有EA[21:2]。一般情況下,EA2信號對應(yīng)邏輯地址A2,但這并不意味著DSP芯片訪問外存時只能進(jìn)行word(32位)的存取。實際內(nèi)部32位地址的最低2~3位經(jīng)譯碼后由BEx輸出,是能夠控制字節(jié)訪問的。更高位邏輯地址經(jīng)譯碼后輸出CE[3:0]。

在實際的系統(tǒng)實現(xiàn)中,C6201的CLKOUT1時鐘頻率為200 MHz,故而SDRAM的實際工作頻率為100 MHz(SDCLK=CLKOUT2=CLKOUT1 frequency/2),即tcyc=10 ns。SDRAM被配置在CE2空問(起始邏輯地址為0x02000000)。

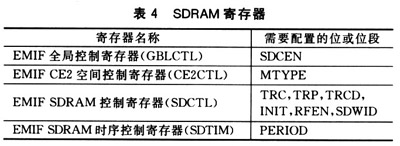

3.2 06201 EMIF SDRAM寄存器設(shè)置

表4列出了配置SDRAM需要設(shè)置的EMIF寄存器名稱及相應(yīng)的位或位段。

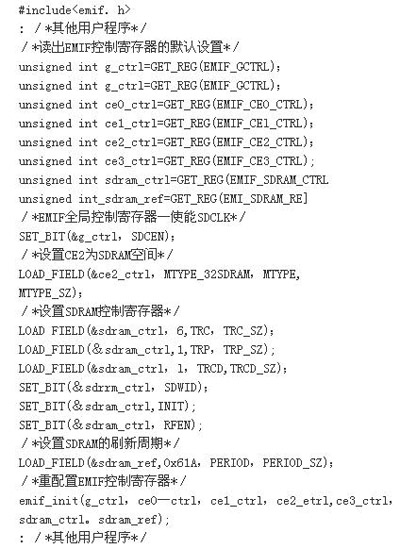

3.3 CCS開發(fā)環(huán)境中SDRAM配置程序源代碼

TI公司的集成開發(fā)環(huán)境CCS(Code Composer Studio)中,IS42S16400SDRAM芯片的配置程序C代碼如下:

結(jié) 語

以上介紹了TMS320C6201 DSP芯片與SDRAM(IS42S16400)的具體硬件接口實現(xiàn)。由于SDRAM具有的大容量、高速度和低價格的優(yōu)勢,使用SDRAM構(gòu)建嵌入式應(yīng)用海量存儲系統(tǒng)會成為一種行之有效的方法。目前該系統(tǒng)已調(diào)試完畢。使用SDRAM作為DSP系統(tǒng)外接高速、大容量主存儲器具有非常明顯的優(yōu)勢,充分顯示了SDRAM在嵌人式系統(tǒng)中的良好應(yīng)用前景。