文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)03-0017-03

0 引言

電子工藝日新月異,而元器件的邊沿速度也越來越高。電路工作速度快了之后,PCB設(shè)計(jì)的要求也隨之越來越高。PCB設(shè)計(jì)質(zhì)量的好壞甚至決定了電路中元器件工作性能乃至整體電路的性能是否達(dá)標(biāo)。特別是考慮到成本以及PCB面積,綜合電路功能,EMI(Electromagnetic Interface)干擾源產(chǎn)生的途徑也越來越多,機(jī)理也越來越復(fù)雜。

1 EMI產(chǎn)生機(jī)理及解決方案

簡(jiǎn)單的EMI三要素包含電磁干擾源、傳播途徑、受擾體[1]。明確了EMI產(chǎn)生的因素之后,在PCB設(shè)計(jì)時(shí)就要考慮哪些因素最容易解決,哪些只能折衷解決。從而在布局、布線以及接地時(shí)就必須認(rèn)真考慮。

1.1 布局

在進(jìn)行PCB布局的時(shí)候,首先根據(jù)功能進(jìn)行區(qū)域劃分。不同功能分布于不同區(qū)域。同時(shí)在功能區(qū)域中再重點(diǎn)照顧敏感單元。

總體而言,PCB布局的時(shí)候要遵循下面原則:

(1)在高速電路中,必須考慮元器件的管腳的分布參數(shù),尤其對(duì)于高速時(shí)鐘信號(hào),器件管腳的分布電容影響特別大。同時(shí)參考分布電感的影響,有可能會(huì)引起信號(hào)的震蕩,從而導(dǎo)致電路功能失效。所以在布局時(shí)應(yīng)盡量緊湊,縮短將來布線時(shí)的導(dǎo)線長度,減小EMI的影響。

(2)如果在電路中模擬器件和電子器件同時(shí)存在,那么就必須將兩者分開布局。因?yàn)閿?shù)字器件的信號(hào)成分非常復(fù)雜,存在多次諧波,會(huì)對(duì)模擬信號(hào)產(chǎn)生非常大的影響。在布局時(shí)必須認(rèn)真考慮[2]。

(3)目前的高速電路中勢(shì)必有時(shí)鐘單元。而時(shí)鐘單元工作的原理其實(shí)可以等效為一個(gè)噪聲源,當(dāng)滿足一定條件時(shí)這個(gè)單元就會(huì)震蕩。它是電路中非常重要的傳導(dǎo)干擾和輻射干擾的源泉。所以在PCB布局時(shí)一定不要把時(shí)鐘單元放置于PCB的邊沿位置。否則PCB的EMI問題將會(huì)非常嚴(yán)重。盡量將時(shí)鐘單元放置于PCB的中心位置。可以大大降低電路中的EMI現(xiàn)象[3]。

1.2 布線

在PCB布線時(shí)如果成本控制不高,則可以盡量地增加地平面,以減小EMI影響。但是如果對(duì)于成本控制嚴(yán)格,則就必須認(rèn)真考慮PCB的層數(shù)以及疊層順序。同時(shí)還要考慮信號(hào)類別,高速信號(hào)盡量和低速信號(hào)分開布線;噪聲的來源以及如何增強(qiáng)噪聲抑制;阻抗匹配的問題,如果高速信號(hào)失匹,必然造成信號(hào)的反射,降低電路可靠性;其他如網(wǎng)絡(luò)表在布線時(shí)也要綜合考慮。

1.2.1 布線的基本原則

布線時(shí)一般遵循如下原則:

(1)在布線時(shí)盡量避免斷點(diǎn),即盡量避免走直角,如圖1所示,因?yàn)檫@樣會(huì)造成反射。為了避免這種現(xiàn)象,盡量將信號(hào)拐點(diǎn)處平滑。同時(shí)關(guān)鍵信號(hào)不得跨越分割區(qū)域,否則EMI會(huì)急劇增加。最常見的信號(hào)線跨越就是跨越不同的電源分割區(qū)域。

(2)在布局時(shí)就考慮到了模擬器件和數(shù)字器件需要分開,所以二者布線同樣要盡量分開。同時(shí)盡量加寬地線和電源線的寬度,一般的布線經(jīng)驗(yàn)是地線寬度>電源線寬度>信號(hào)線寬度。同時(shí)在數(shù)字信號(hào)線布線時(shí)綜合考慮3W原則,對(duì)于多層板,內(nèi)電層要考慮20H原則,考慮到這些則可以避免70%的EMI現(xiàn)象。對(duì)于模擬敏感的導(dǎo)線則采取諸如包地的措施。

(3)諸如USB2.0或者其他高速差分線在布線時(shí)盡量采用耦合方式布線,同時(shí)確保差分對(duì)之間的參考平面完整。由于差分對(duì)一般而言都是高速信號(hào),所以盡量不要在PCB邊沿布線。

1.2.2 環(huán)路(loops)

電流回路是在PCB設(shè)計(jì)中不可避免的。自信號(hào)流出至信號(hào)流入而形成環(huán)路,每個(gè)環(huán)路都相當(dāng)于一個(gè)天線。要減小PCB中的EMI,也就意味著要減小環(huán)路的數(shù)量以及環(huán)路的天線能力。這就是說在設(shè)計(jì)時(shí)要了解每一個(gè)信號(hào)線的流向,對(duì)于高速信號(hào)必須要減小它的環(huán)路面積[4]。

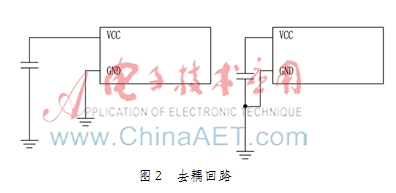

對(duì)于電路中應(yīng)用最多的是去耦電容構(gòu)成的電源回路,如圖2所示。如果去耦電容放置位置如左圖,則構(gòu)成的電流回路較大,EMI現(xiàn)象也會(huì)較為明顯;而如右圖則緊靠芯片放置,去耦回路很小,能起到較為明顯的去EMI作用。減小環(huán)路一般要注意如下事項(xiàng):

(1)保證每條信號(hào)線的兩點(diǎn)之間只有一條路徑。

(2)盡量使用地平面,同時(shí)保證信號(hào)回路沒有阻塞。

1.2.3 PCB的地線

(1)PCB的接地系統(tǒng)中要明確數(shù)字地、模擬地、系統(tǒng)屏蔽地之間的區(qū)別。數(shù)字地與模擬地之間用磁珠和電容隔離。而將數(shù)字地和屏蔽地直接相連。

(2)在PCB中如果允許,則盡量加粗地線。實(shí)在條件有限,最少也要降額50%使用,才能安全可靠。

(3)接地線要構(gòu)成閉合回路,能夠增強(qiáng)抗干擾能力,也可以減小系統(tǒng)之間的電位差[5]。

1.3 濾波設(shè)計(jì)

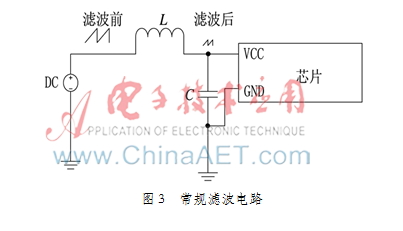

在高速PCB中,對(duì)于電源線和信號(hào)線,可以采取濾波處理。常規(guī)的措施有添加磁性濾波器件、EMI濾波器、去耦電容等(如圖3)。

1.3.1 去耦電容選擇

(1)在電路中去耦電容的作用既可以平滑電源,也可以增強(qiáng)器件抗干擾能力。一般去耦電容選擇瓷片電容,瓷片電容溫度穩(wěn)定性較高,精度高,體積小,ESR(等效電阻)低。在電路設(shè)計(jì)中一般選用1 ?滋F~100 ?滋F容值之間,同時(shí)根據(jù)電路來考慮電容的耐壓?jiǎn)栴}。

(2)去耦電容位置已經(jīng)在前面電源回路中講述過,一定要緊靠器件放置,否則效果不好。

1.3.2 磁性器件選擇

磁性器件有電感和磁珠兩類,一般在電源端選用電感,而在信號(hào)線之間選用磁珠。在磁性器件選擇時(shí)一定要考慮它的飽和度參數(shù)。一旦磁性器件飽和,則會(huì)燒毀。同時(shí)要考慮磁性器件的Q(品質(zhì)因數(shù))和DCR參數(shù)。

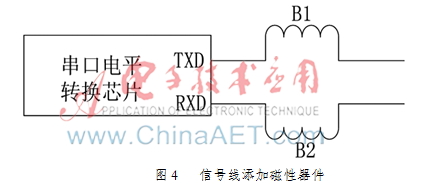

在信號(hào)線中常用的有串口線上使用磁珠增強(qiáng)抗EMI能力,如圖4所示。

1.3.3 EMI濾波器選擇

在電源入和信號(hào)線出的地方是共摸干擾嚴(yán)重的地方。常見的抗共模干擾措施有添加共摸電感、壓敏電阻、LC電路、專用的EMI濾波器等。在高速數(shù)字電路中,如USB、HDMI等數(shù)字接口高速傳輸,必須考慮EMI問題。這里就不再一一贅述了。

1.4 信號(hào)反射

在信號(hào)傳輸中總是希望源端能量能夠全部傳輸?shù)截?fù)載端,也就是ZL和ZO一定要相等。如果它們不相等(即阻抗不匹配),則勢(shì)必有部分能量會(huì)被反射。

如果線路傳輸延遲較長,有較強(qiáng)的信號(hào)反射回源端,那么源端必須改變一個(gè)較大的量去補(bǔ)償,這個(gè)時(shí)候就出現(xiàn)了振鈴,如圖5所示。

信號(hào)出現(xiàn)振鈴的時(shí)候,也是EMI現(xiàn)象嚴(yán)重的時(shí)候。在PCB設(shè)計(jì)中為了避免出現(xiàn)這種現(xiàn)象。一般需遵循如表1原則。

2 EMI測(cè)試

在產(chǎn)品設(shè)計(jì)之后,雖然綜合考慮了很多避免EMI的方法。但是一定要通過測(cè)試才能發(fā)現(xiàn)問題,然后整改設(shè)備,解決問題。

EMI測(cè)試包含了測(cè)試方法、儀器以及測(cè)試場(chǎng)所。測(cè)試方法自然是參考各項(xiàng)標(biāo)準(zhǔn)來測(cè)試,而儀器如果條件不允許的話,使用頻譜儀也能定性的測(cè)試。如果想要知道設(shè)備具體EMI相關(guān)值,必須使用專業(yè)設(shè)備。至于測(cè)試場(chǎng)所,最好是在暗室中測(cè)試,如果條件不允許,則折衷考慮。

3 結(jié)語

高速PCB設(shè)計(jì)中對(duì)于EMI的考慮是一個(gè)非常復(fù)雜的程序。而且在前面所述的多種因素有時(shí)互為矛盾,此時(shí)就需要設(shè)計(jì)者綜合考慮哪個(gè)是主要矛盾,要首先考慮,哪些可以退而求其次。但無論如何,對(duì)于解決EMI的手段勢(shì)必會(huì)越來越多且有效。

參考文獻(xiàn)

[1] 曼特羅斯.電磁兼容的印制電路板設(shè)計(jì)[M].呂英華等,譯.北京:機(jī)械工業(yè)出版社,2008.

[2] 田建學(xué).機(jī)載設(shè)備電磁兼容設(shè)計(jì)與實(shí)施[M].北京:國防工業(yè)出版社,2010.

[3] 陳淑鳳.航天器電磁兼容技術(shù)[M].北京:中國科學(xué)技術(shù)出版社,2007.

[4] 鄭軍奇.EMC電磁兼容設(shè)計(jì)與案例分析[M].北京:電子工業(yè)出版社,2010.

[5] 朱文立.電磁兼容設(shè)計(jì)與整改對(duì)策及案例分析[M].北京:電子工業(yè)出版社,2012.