文獻標識碼: A

文章編號: 0258-7998(2015)02-0055-04

0 引言

Sigma-Delta(ΣΔ)加速度傳感器利用了ΣΔ調制技術實現(xiàn)了數(shù)字輸出,,相對于傳統(tǒng)加速度傳感器系統(tǒng),其對周圍環(huán)境溫度變化不太敏感,,而且穩(wěn)定性較好,,尤其是其能夠很方便地給后級數(shù)字處理單元提供直接數(shù)字輸出,有利于系統(tǒng)的集成[1-2],。國外對于ΣΔ加速度傳感器系統(tǒng)的研究開展得較早,,取得的研究成果也較多。國內在相關的研究方面落后了很多,,且主要集中于低噪聲性能的研究[3-5],。然而諧波失真是加速度傳感器誤差的一個重要來源,目前針對其開展的研究并不多,。文獻[6]開展了一種閉環(huán)微機械加速度計的非線性研究,,主要集中于結構生產(chǎn)工藝精度偏差導致質量塊零點偏移進而導致的非線性問題。文獻[1]開展了高階ΣΔ加速度傳感器的非線性研究,,研究了敏感結構非線性,、運放非線性增益、靜電力反饋非線性對系統(tǒng)的影響,。由于沒有考慮其他非線性因素,,文獻[1]中在大信號輸入下積分器和敏感結構非線性行為級仿真顯示諧波失真淹沒在噪聲中,而靜電力反饋非線性諧波失真較大,。實際上在加速度傳感器應用中,,往往輸入加速度信號較大,,在這種情況下接口電路的積分器建立、開關導通電阻,、溝道電荷注入效應等都會產(chǎn)生非線性,,這些非線性的建立和轉換過程會在輸出呈現(xiàn)出較大的諧波失真,從而影響帶寬內有用信號精度,。本文基于一種五階ΣΔ加速度計閉環(huán)系統(tǒng),,分析了其各個主要部分的非線性,在MATLAB的Simulink下建立了非線性模型進行仿真,。設計了一種單端五階開關電容ΣΔ加速度計閉環(huán)接口電路,,對比行為級仿真結果和電路仿真結果,驗證了建立的模型的有效性,。

1 主要非線性特性分析

1.1 敏感結構引起的電荷轉換非線性

當傳感器感知外界加速度ain時,,質量塊產(chǎn)生位移x,從而引起了差動電容值發(fā)生相反的變化,,假如初始電容為C0,,電容初始間距為d0,如果采用圖1所示的開關電容檢測方法對差動電容變化進行檢測,,則:

其中A0=2C0Vd/Cf,,Vd是參考電壓。當給系統(tǒng)施加較大的加速度信號時,,質量塊位移量x也較大,,此時電荷轉換輸出電壓的三次諧波分量不可忽略?;贛ATLAB/Simulink下的函數(shù)可以很容易地建立該非線性模型,。

1.2 積分器非線性

積分器是ΣΔ加速度計系統(tǒng)中的重要部分,主要非線性部分來源于非線性的直流增益,、有限增益帶寬,、有限壓擺率等。圖2是開關電容積分器的積分模型圖,。如果運放擺率足夠大,或者輸入信號較小時,,積分過程的非線性主要由積分器中的運放非線性增益引起,,關于運放的非線性直流增益模型已經(jīng)在文獻[1]中給出。然而當考慮到低功耗設計或者輸入信號較大時,,運放的有限壓擺率和帶寬將會導致積分器的建立非線性,。此時有|Va(0+)|>Io/gm, 積分器輸出為:

從式(2)可以看出,,當積分器的輸入信號增大,,由運放擺率和帶寬限制的非線性部分開始占據(jù)主要部分,。

1.3 開關非線性

用開關電容電路來實現(xiàn)ΣΔ加速度計接口電路時,模擬開關的大量使用會引入開關的非線性問題,。開關在導通時處于線性工作區(qū),,一般情況下采用CMOS互補開關,則開關導通電阻為:

其中r1~r3是關于工藝和電容的系數(shù),。由上式可以看出由開關導通電阻導致的積分器輸出非線性,。其本質上是由襯底偏置效應引起的。同理,,襯底偏置效應也會引起溝道電荷注入過程中的非線性,,導致諧波失真的產(chǎn)生,這些非線性的關系式可以很容易地在MATLAB中建立模型,。

靜電力反饋非線性和運放直流增益非線性已經(jīng)在文獻[1]中給出,,這里不再詳細描述,只在系統(tǒng)建模中加入其非線性模型,,建立完備的整體ΣΔ加速度計非線性模型,。另外為了系統(tǒng)建模時的準確性,在系統(tǒng)模型中加入開關采樣抖動,、kT/C噪聲,、運放噪聲等等非理想特性,結合上文所描述的開關非線性,、C-V轉換非線性,、積分器非線性、靜電力反饋非線性模塊,,建立的非理想特性五階加速度計系統(tǒng)模型如圖3所示,。該五階加速度計結構參考了文獻[3]的結構,本文的加速度計系統(tǒng)基于一種低Q值傳感器表頭,,該高階結構的穩(wěn)定性是基于后級電學調制器局部反饋系數(shù)的調整,。當采樣頻率為250 kHz,輸入信號244.12 Hz,,信號幅度為0.3 g時,,行為級非理想模型仿真結果如圖4所示,系統(tǒng)輸出噪底的平均值約為-150 dB,,三次諧波失真約為-103.9 dB,。

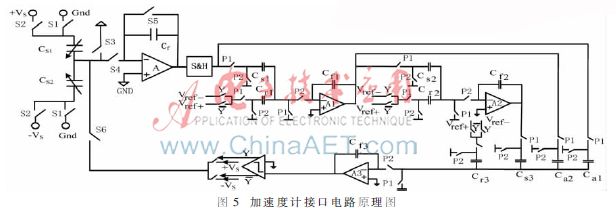

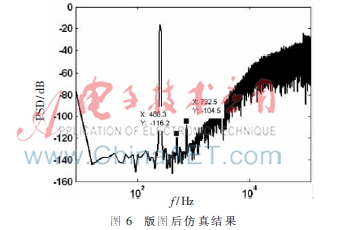

2 電路設計和版圖后仿真

圖5是本文設計的加速度計接口電路原理圖。圖中包含了等效的機械結構部分(可變電容Cs1和Cs2),、前級低噪聲電荷敏感電路,、采樣保持電路(S&H)、積分器網(wǎng)絡以及比較器電路,。該設計的前級低噪聲檢測電路參考了文獻[1]的設計思路,,實現(xiàn)高精度的電荷轉換輸出,。后級三階積分器網(wǎng)絡和兩階加速度計表頭構成了五階的高階系統(tǒng),抑制了系統(tǒng)的量化噪聲,。積分器網(wǎng)絡中的采樣電容和反饋電容分離,,這樣能夠很方便地實現(xiàn)局部反饋因子,使得反饋參考電壓能夠一致,,不用分別設計參考電壓值,。該結構采用一位量化輸出,所以比較器的輸出可以直接用來控制一位DAC反饋的開關,,將數(shù)字輸出轉換成模擬參考信號,,反饋給加速度計表頭。在TSMC 0.35 ?滋m工藝下對該單端加速度計接口電路進行版圖設計和優(yōu)化,,將該接口電路的版圖網(wǎng)表導入Spectre下進行后仿真,,采樣頻率為250 kHz,輸入正弦信號同樣為244.12 Hz,,信號幅度為0.3 g,,版圖的后仿真結果如圖6所示,系統(tǒng)輸出噪底的平均值約為-140 dB,,比行為級仿真結果高了約10 dB,,這可能是前級電荷檢測部分的噪聲混疊導致的。版圖后仿真的二次諧波失真為-116.2 dB,,三次諧波失真為-104.5 dB,。二次諧波的產(chǎn)生是由于本文為了簡化設計流程,采用了單端實現(xiàn)的方式,。在版圖設計時由于工藝參數(shù)的誤差,,都會使得設計值和理想的參數(shù)存在一定的偏差。后仿真結果的三次諧波失真和行為級結果差別不大,,這從一個方面反映了行為級非線性模型的準確性,。另外版圖后仿真結果顯示其和行為級模型有一樣的噪聲整形能力,這說明了電路設計的正確性,。

3 結束語

本文分析了ΣΔ加速度計系統(tǒng)的非線性,,并在MATLAB中建立了一個五階加速度計系統(tǒng)的整體模型,其中包含了主要的非線性模型和噪聲特性模型,,利用根軌跡法分析了高階系統(tǒng)的穩(wěn)定性,。在TSMC 0.35 ?滋m工藝下實現(xiàn)了加速度計接口電路和版圖設計,版圖的后仿真結果顯示當輸入0.3 g的正弦加速度信號時,,輸出的三次諧波失真和行為級建模基本一致,,由于噪聲混疊使得輸出噪底比行為級提高了10 dB,。后仿真結果表明設計的電路和行為級模型具有一樣的噪聲整形能力,,進一步驗證了建立的行為級模型的準確性和電路實現(xiàn)的正確性。

參考文獻

[1] 呂炳均.高階SIGMA DELTA微加速度計接口ASIC芯片研究[D].哈爾濱:哈爾濱工業(yè)大學,,2013.

[2] Xiao Dingbang,,Wu Xuezhong,Li Shengyi.System design of second-order sigma delta micromachined accelerometer[C].Proceedings of the 1st IEEE International Conference on Nano/Micro Engineered and Molecular Systems,,2006:299-302.

[3] LIU X W,,XU H L,Yin L,,et al.A low noise sigma-delta microaccelerometer interface circuit[J].IEICE Electronics Express,,2014,11(12):1-6.

[4] 劉云濤.電容式SIGMA-DELTA微加速度計接口ASIC芯片研究[D].哈爾濱:哈爾濱工業(yè)大學,,2010.

[5] 孫騰,,車錄鋒,黎曉林,,等.基于PID反饋的高Q值加速度計閉環(huán)檢測電路[J].傳感器與微系統(tǒng),,2011,30(2):101-106.

[6] Wan Caixin,,Dong Jingxin.Nonlinearity of a closed-loop micro-accelerometer[C].16th IEEE International Conference on Control Applications,,October 2007:1260-1265.

[7] 楊驍.寬帶Sigma-Delta調制器的研究與設計[D].西安:西安交通大學,2008.