文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.005

中文引用格式: 林俊明,鄭耀華,張志浩,等. CMOS射頻功率放大器高效率和高線(xiàn)性度研究進(jìn)展[J].電子技術(shù)應(yīng)用,2015,41(11):17-23.

英文引用格式: Lin Junming,Zheng Yaohua,Zhang Zhihao,et al. Survey of high efficiency and linearity of CMOS power amplifiers[J].Application of Electronic Technique,2015,41(11):17-23.

0 引言

目前,全球應(yīng)用于智能手機(jī)等便攜性移動(dòng)設(shè)備的移動(dòng)網(wǎng)絡(luò)急速發(fā)展和擴(kuò)張,且多功能智能手機(jī)應(yīng)用愈加廣泛,為滿(mǎn)足用戶(hù)實(shí)時(shí)通信的用戶(hù)體驗(yàn),應(yīng)用于智能手機(jī)的通信系統(tǒng)應(yīng)該能夠更加有效地處理文字、聲音和視頻數(shù)據(jù)并實(shí)現(xiàn)全球漫游。為了提供高數(shù)據(jù)速率的大數(shù)據(jù)傳輸,現(xiàn)代通信系統(tǒng)(WCDMA/3G/4G/LTE)采用了更加復(fù)雜的高頻譜效率的調(diào)制方式,如OFDM或QPSK和QAM等相移鍵控和幅移鍵控相結(jié)合的調(diào)制方式。為滿(mǎn)足不同用戶(hù)的使用需求,智能手機(jī)一般都支持兩種或者兩種以上網(wǎng)絡(luò)制式,而隨著手機(jī)的工作制式不同,其有效的頻率帶寬不同,因此,作為通信模組之一的功率放大器(PA)應(yīng)具備多頻多模(Multi-band and Multi-mode)的能力。

作為3GPP(3rd Generation Partnership Project)的演進(jìn)路線(xiàn)中的主流技術(shù),LTE-Advanced將是2015年的主流通信方式。LTE的關(guān)鍵技術(shù)有多載波和多天線(xiàn)技術(shù),其中多載波技術(shù)采用正交頻分復(fù)用(OFDM)的調(diào)制方式,使各個(gè)子載波重疊排列,大大提高頻譜效率的同時(shí)保持了載波之間的正交性,以避免載波之間的干擾。不過(guò),LTE信號(hào)在給定的受限的帶寬內(nèi),有著非常高的峰均比(PAPR),這使PA常工作在功率回退區(qū),造成PA的實(shí)際效率低下的現(xiàn)象。另外,為了線(xiàn)性放大LTE這類(lèi)非常包絡(luò)信號(hào)(non-constant envelope signal),要求PA有著較高的線(xiàn)性度(Linearity),因此,應(yīng)用于新一代通信系統(tǒng)的功率放大器,必須有著較高的功率效率和線(xiàn)性度,且有著較寬的工作帶寬或者是滿(mǎn)足多頻多模的通信要求。

隨著便攜設(shè)備的功能模塊越來(lái)越復(fù)雜,將各個(gè)模塊單片集成起來(lái),將大大縮短設(shè)備制造商的加工時(shí)間,因此,如何減小芯片的有效面積和用廉價(jià)的工藝在單一芯片上實(shí)現(xiàn)整個(gè)射頻模組將是未來(lái)的研究主流。現(xiàn)代比較流行的集成電路工藝主要有六種:硅CMOS、BICMOS、Bipolar、GaAs、HBT和SiGe,但由于硅工藝是最為成熟的,也是成本最低、集成度高和應(yīng)用最廣泛的集成工藝,另外,大多數(shù)無(wú)線(xiàn)收發(fā)機(jī)的基帶處理部分都使用硅工藝,因此,硅CMOS工藝是單片實(shí)現(xiàn)各個(gè)模塊集成的理想解決方案。不過(guò)CMOS工藝自身存在著物理缺陷,如低截止電壓(breakdown voltage)、較差的電流能動(dòng)能力、片上無(wú)源器件的Q值小、較大的寄生電容、地襯底電阻率較低、沒(méi)有較為精確的RF模型和較差的線(xiàn)性度等,這些缺陷都大大限制了CMOS在RFIC領(lǐng)域的應(yīng)用,而且通信系統(tǒng)對(duì)高效率、高線(xiàn)性度和可實(shí)現(xiàn)性有著很高的要求,所以目前PA制造商還是常使用價(jià)格比較昂貴的III-V類(lèi)混合硅半導(dǎo)體工藝器件(Compound Semiconductor Device)[1-4],這些器件通過(guò)TWV(Through-Wafer-via)技術(shù)提供一個(gè)具有良好散熱效率的理想環(huán)境,常用于Bluetooth、WLAN和GSM/GPRS等應(yīng)用[5]。不過(guò),CMOS工藝的物理缺陷可以通過(guò)一系列技術(shù)來(lái)緩解,在高供電電壓的情況下,可以選擇HV CMOS和BCD(Bipolar-CMOS-DMOS)工藝[6]。采用下行鍵合線(xiàn)(Down-bonding Wires)可以實(shí)現(xiàn)在給定的負(fù)載下得到較高的輸出功率,這種方法的缺點(diǎn)是會(huì)減小電壓擺幅,不過(guò)可以通過(guò)引入差分結(jié)構(gòu)克服這個(gè)缺點(diǎn)。解決CMOS工藝低截止電壓的一個(gè)很好的技術(shù)是引入共源共柵的Cascode結(jié)構(gòu),不過(guò)這種結(jié)構(gòu)會(huì)使等效的knee電壓增加,所以也會(huì)在一定程度上減小電壓擺幅。CMOS的寄生電容和襯底較低的電阻率,使得在晶體管引腳間的信號(hào)存在著耦合,不過(guò)這種耦合影響也不全是消極的,通過(guò)利用在Cascode結(jié)構(gòu)中的共柵(CG)晶體管的RF泄露信號(hào)(Leakage signals)提供一個(gè)負(fù)反饋,不僅可以增強(qiáng)線(xiàn)性度,而且可以減小柵極和漏極間的電壓耦合,這種方法最大的一個(gè)優(yōu)點(diǎn)就是不需要額外的器件和芯片面積,而且容易實(shí)現(xiàn)。由于CMOS的跨導(dǎo)較低,其電流驅(qū)動(dòng)能力較其他III-V類(lèi)半導(dǎo)體低,需要通過(guò)級(jí)聯(lián)結(jié)構(gòu)來(lái)實(shí)現(xiàn)(Cascaded-stage)較大的功率增益,所以,多級(jí)級(jí)聯(lián)(multistage cascade topology)是CMOS PA中最常見(jiàn)的一種電路拓?fù)洹km然采用Cascode結(jié)構(gòu)和柵氧厚度較厚的晶體管可以減輕CMOS的熱載流體效應(yīng)和低柵氧厚度的低擊穿電壓的問(wèn)題,但這并不是最理想的辦法。根據(jù)最新的研究報(bào)告,應(yīng)用于3G/4G的手持設(shè)備的硅工藝PAs的性能已經(jīng)可以和III-V類(lèi)PAs相比擬[7],另外,類(lèi)似于III-V類(lèi)工藝的TWV技術(shù),在SiGe BiCMOS工藝中, TSV(Through-Silicon-Via)技術(shù)同樣可以為SiGe BiCMOS工藝提供一個(gè)理想的回流地環(huán)境和熱釋放條件,因此,采用TSV技術(shù)的SiGe CMOS工藝將會(huì)是PA設(shè)計(jì)的一個(gè)首選方案[8]。

1 PA效率增強(qiáng)技術(shù)的關(guān)鍵研究進(jìn)展

功率放大器是手持移動(dòng)設(shè)備中耗能最大的模塊之一,因此為了延長(zhǎng)電池的使用壽命和迎合新一代通信(4G/LTE)的要求,高效率是PA設(shè)計(jì)的一個(gè)很重要而且頗有挑戰(zhàn)性的指標(biāo)。由于傳統(tǒng)的PA供電電壓是固定的,而且它的最優(yōu)負(fù)載僅僅是當(dāng)PA輸出最大功率時(shí)的最優(yōu)阻抗,對(duì)于LTE這種有著高PAPR的調(diào)制方式,PA常工作在功率回退區(qū),因此PA的實(shí)際工作效率非常低。

提高這類(lèi)PA效率的關(guān)鍵技術(shù)主要有兩類(lèi):通過(guò)一定方法調(diào)制負(fù)載,使每個(gè)功率回退點(diǎn)都對(duì)應(yīng)于一個(gè)最優(yōu)阻抗[9]和通過(guò)輸出的瞬時(shí)功率調(diào)制供電電壓,從而減小功率回退時(shí)的靜態(tài)功耗。第一種通過(guò)調(diào)制負(fù)載的方法常用于手機(jī)等移動(dòng)設(shè)備,第二種方法常常直接通過(guò)利用調(diào)制信號(hào)的包絡(luò)直接去調(diào)制PA的工作電壓,從而減小功耗[10]。

通過(guò)直接調(diào)制PA的工作電壓而達(dá)到增強(qiáng)PA效率的技術(shù)主要有PM(Polar Modulation)、EER(Envelope Elimination and Restoration)和ET(Envelope Tracking),如圖1所示。PM利用數(shù)字信號(hào)處理技術(shù)(DSP)來(lái)產(chǎn)生相位和幅度調(diào)制信號(hào)[11,12],不過(guò)這種方法受限于DC-DC轉(zhuǎn)換器自身的效率、帶寬和面積,并且DC-DC轉(zhuǎn)換模塊通常需要使用片外的電感和開(kāi)關(guān)實(shí)現(xiàn),這大大限制了PM在RFIC中的應(yīng)用。EER和ET是目前PA效率增強(qiáng)的主流技術(shù)。EER通過(guò)包絡(luò)檢波器和限幅器將輸入信號(hào)分解成幅度信號(hào)和相位信號(hào),因此可以用非線(xiàn)性PA來(lái)放大相位信號(hào),而PA的電壓則由幅度信號(hào)調(diào)制,從而可以達(dá)到較大的效率,如圖2所示,但EER內(nèi)部固有的非線(xiàn)性導(dǎo)致幅度調(diào)制路徑和相位調(diào)制路徑間存在延時(shí)[13,14]。

與EER不同的是,ET使用線(xiàn)性的PA,如圖3所示。因此,ET的最大的一個(gè)好處就是沒(méi)有類(lèi)似于EER的這種延時(shí)失配現(xiàn)象[15],從而使ET技術(shù)可以在增強(qiáng)效率的基礎(chǔ)上通過(guò)其他技術(shù)來(lái)取得線(xiàn)性度和效率之間的折中,并可以應(yīng)用于寬帶信號(hào)[16]。ET主要目標(biāo)是為了當(dāng)輸入高PARP信號(hào)時(shí),同時(shí)在最大輸出功率和在功率回退區(qū)域獲得最大工作效率,且滿(mǎn)足高線(xiàn)性度的要求,如EVM和ACLR等。另外,ET技術(shù)的效率和線(xiàn)性度依賴(lài)于電源調(diào)制器(Supply Modulator),如果電源調(diào)制效率低下,則ET整體的效率就非常低,因此必須增強(qiáng)電源調(diào)制器的線(xiàn)性度,文獻(xiàn)[17]通過(guò)雙開(kāi)關(guān)和前饋信號(hào)來(lái)增強(qiáng)電源調(diào)制器的效率。為了精確跟蹤寬帶信號(hào)并不產(chǎn)生明顯失真,需要提高電源調(diào)制器的工作帶寬[18]。

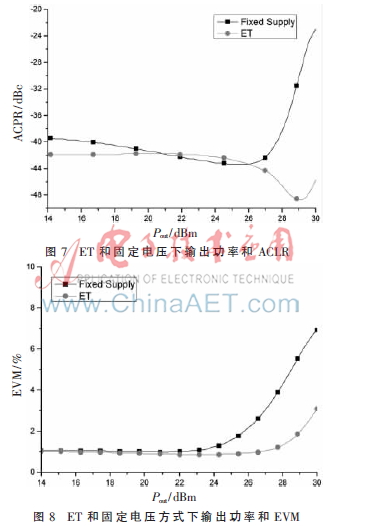

使用ET技術(shù)可以大幅度提高功率回退時(shí)的效率,如圖4所示,為了減小復(fù)雜性和提高跟蹤精度,電源調(diào)制器可以通過(guò)開(kāi)關(guān)實(shí)現(xiàn)在線(xiàn)性區(qū)使PA工作電壓保持一個(gè)較小的恒定值,而在過(guò)渡區(qū)和壓縮區(qū)則通過(guò)調(diào)制信號(hào)的包絡(luò)來(lái)調(diào)制PA的工作電壓,如圖5所示。采用這種方式的ET技術(shù)有一個(gè)缺點(diǎn),那就是增益會(huì)有所降低,如圖6所示,但這種方式較固定電壓的方式有著較低的ACLR和EVM,特別是在高輸出功率的情況下,如圖7和圖8所示。

ET技術(shù)的一個(gè)優(yōu)點(diǎn)是相位調(diào)制和幅度調(diào)制環(huán)路間沒(méi)有延遲失配,故可以在效率、線(xiàn)性度和帶寬間進(jìn)行折中設(shè)計(jì),這些技術(shù)都可以歸納為ET的優(yōu)化技術(shù),其中較為重要的是改善線(xiàn)性度,而包絡(luò)整形(Envelope-shaping)是改善線(xiàn)性度的一個(gè)有效方法[1],其結(jié)果可以通過(guò)跟蹤掃描的點(diǎn)來(lái)表示出來(lái)[19]。這種方法可以改善工作于ET方式下的PA性能,包括效率和線(xiàn)性度[20],通過(guò)結(jié)合其他電路拓?fù)浣Y(jié)構(gòu),可以更進(jìn)一步改善ET PA的效率。文獻(xiàn)[21]通過(guò)采用偽差分的拓?fù)浣Y(jié)構(gòu),結(jié)合SiGe BICMOS的TSV技術(shù)實(shí)現(xiàn)了一個(gè)高效率的ET-PA系統(tǒng)。

改善ET的效率的另一個(gè)有效的方法是像傳統(tǒng)開(kāi)關(guān)PA一樣引入工作在飽和區(qū)的功率放大器(Saturated Power Amplifier),這樣不僅可以提高ET PA的輸出功率,還可以最大化效率。

為了同時(shí)改善PA的動(dòng)態(tài)范圍、線(xiàn)性度和效率,可以采用動(dòng)態(tài)反饋控制(Dynamic feedback control)和共源共柵Cascode結(jié)構(gòu)的電路拓?fù)鋄22],這種結(jié)構(gòu)中的CG級(jí)采用了自偏置技術(shù),從而改善了線(xiàn)性度和效率。不過(guò)這種結(jié)構(gòu)也存在著自身的缺陷,因?yàn)镃G級(jí)的晶體管的非線(xiàn)性會(huì)使整體的線(xiàn)性度下降,而且漏-柵間的擊穿電壓?jiǎn)栴}將是這種結(jié)構(gòu)的一個(gè)瓶頸。這是因?yàn)楣ぷ饔贓T PA的CG級(jí)在ET PA工作于功率回退區(qū)時(shí),由于電源調(diào)制器的作用,PA的工作電壓會(huì)很小,而且Cascode結(jié)構(gòu)的飽和電壓相對(duì)較高(如knee電壓),使晶體管工作在線(xiàn)性區(qū),從而使ET PA在峰值功率和回退時(shí)的功率增益會(huì)有著很大的偏差,這就使PA的線(xiàn)性度和動(dòng)態(tài)范圍性能下降了[23]。這個(gè)問(wèn)題存在的根本原因是因?yàn)镃G級(jí)的偏置電壓是固定的,因此,可以通過(guò)柵極自適應(yīng)動(dòng)態(tài)偏置技術(shù)和Cascode反饋偏置(Cascode Feedback Bias Technique)技術(shù)進(jìn)行折中設(shè)計(jì),反饋偏置技術(shù)利用在CMOS工藝下CG晶體管的泄露信號(hào)通過(guò)負(fù)反饋環(huán)路反饋到偏置電路,從而改善CMOS PA的線(xiàn)性度[24],采用共源共柵Cascode結(jié)構(gòu)的另外一個(gè)需要仔細(xì)考慮的問(wèn)題是關(guān)于CG級(jí)和CS級(jí)的尺寸比例,這在一定程度上會(huì)影響PA整體的效率[22]。對(duì)于ET技術(shù)在多頻多模情況下的應(yīng)用,簡(jiǎn)單而高效的方法是通過(guò)并聯(lián)一個(gè)開(kāi)關(guān)電容從而實(shí)現(xiàn)兩個(gè)模式間的切換,文獻(xiàn)[1]通過(guò)結(jié)合升壓電源調(diào)制器(Boosted supply modulator)和開(kāi)關(guān)電容實(shí)現(xiàn)了一個(gè)雙模多頻帶的高效率ET功率放大器,使ET PA不僅可以工作在高功率模式,還可以工作于低功率模式。

由于多數(shù)移動(dòng)設(shè)備可以在多個(gè)網(wǎng)絡(luò)制式間相互切換,因此,對(duì)于工作于類(lèi)似于GSM/EDGE網(wǎng)絡(luò)制式下的PA,可以采用其他技術(shù)來(lái)增強(qiáng)效率。如采用反相結(jié)構(gòu)(outphasing architecture)的PA,這種結(jié)構(gòu)最大的優(yōu)點(diǎn)是可以使用非線(xiàn)性PA,且不需要額外的電源調(diào)制器就可以獲得較大的效率并不會(huì)引起輸出電壓擺幅下降,最大的缺點(diǎn)就是輸出端的求和電路不可避免會(huì)存在著功率損耗,因此求和的兩條路徑間的匹配會(huì)影響到整體電路的效率[25]。Doherty PA也是一種能夠有效提高功率回退區(qū)效率的增強(qiáng)技術(shù),最大的理論效率可以達(dá)到79%,并擴(kuò)展大概6 dB的線(xiàn)性范圍[26],不過(guò),這種技術(shù)由于需要采用1/4波長(zhǎng)傳輸線(xiàn),不僅增加了損耗,還需要占據(jù)較大的芯片面積,從而大大限制了其在RFIC的應(yīng)用。

高電壓應(yīng)用下的效率增強(qiáng),可以采用傳統(tǒng)的開(kāi)關(guān)功率放大器,其中關(guān)鍵問(wèn)題是片上電源的耦合和反彈[27],一個(gè)可行的解決方案是采用兩個(gè)較寬的開(kāi)關(guān)PA并聯(lián)代替原來(lái)的開(kāi)關(guān)PA,從而避免了開(kāi)關(guān)PA的感性反饋,從而減小了電源耦合[6]。另外,通過(guò)采用壓電器件(Piezoelectric Device),可以使PA輸出幾十瓦的功率并且有著很高的集成度,這種壓電器件有著很好的噪聲控制[28],又因壓電反應(yīng)可以等效為一個(gè)壓電電容,因此并不會(huì)增加電路分析的復(fù)雜度。

2 高線(xiàn)性PA的關(guān)鍵技術(shù)研究進(jìn)展

當(dāng)PA工作于高效率區(qū)時(shí),PA將會(huì)因本身的非線(xiàn)性而出現(xiàn)功率壓縮,從而減小了PA的功率增益,而當(dāng)PA工作于功率回退區(qū)時(shí),PA的實(shí)際工作效率非常低,這將會(huì)消耗大部分電能,因此,PA的線(xiàn)性化目的是改善PA的整體線(xiàn)性度,且使整體的效率比功率回退時(shí)的效率高。PA的線(xiàn)性體現(xiàn)為兩個(gè)方面:AM-AM和AM-PM失真。而衡量PA的線(xiàn)性度和偏離程度的指標(biāo),應(yīng)該根據(jù)系統(tǒng)的要求和調(diào)制方式來(lái)決定。PA常用的線(xiàn)性度指標(biāo)有ACPR、EVM、1 dB壓縮輸出功率和三階交調(diào)點(diǎn),在工程上常用單音(single tone)和雙音信號(hào)(two tone)對(duì)PA分別進(jìn)行諧波和交調(diào)失真等非線(xiàn)性測(cè)量與分析。此時(shí),ACPR代表頻譜帶外的失真,而EVM代表帶內(nèi)失真。由于雙音信號(hào)會(huì)對(duì)相鄰信道造成干擾,所以對(duì)于某一信道,都有一個(gè)頻譜限制(spectral mask)。

改善PA的線(xiàn)性度的一個(gè)常用方法是通過(guò)反相的非線(xiàn)性補(bǔ)償電路來(lái)抵消原來(lái)電路的非線(xiàn)性[29-31],這些電路通過(guò)補(bǔ)償AM-AM或者是AM-PM失真來(lái)達(dá)到優(yōu)化線(xiàn)性度的目的,然而,2-D電路綜合技術(shù)(2DCST),利用電流-電壓轉(zhuǎn)換器和可調(diào)的壓控電容(Voltage Characteristic Capacitor)實(shí)現(xiàn)同時(shí)補(bǔ)償AM-AM和AM-PM失真,且不需要反相電路[32]。雖然這些技術(shù)可以比較有效地改善PA的線(xiàn)性度,不過(guò)這些技術(shù)需要額外的控制單元,如電流-電壓轉(zhuǎn)換器等,從而限制了其在RFIC方面的廣泛應(yīng)用。

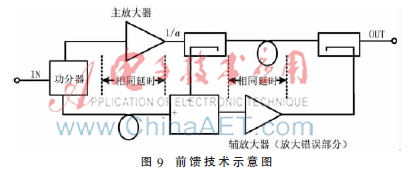

反饋是改善PA線(xiàn)性度的另外一種有效的方法,而且可以改善帶寬,不過(guò)前提是犧牲了增益。前饋技術(shù)(Feed Forward)廣泛應(yīng)用于高穩(wěn)定性要求的PA設(shè)計(jì)中,主要通過(guò)前饋錯(cuò)誤環(huán)路獲得原始信號(hào)的錯(cuò)誤信號(hào),然后將放大后的信號(hào)與錯(cuò)誤信號(hào)相減,從而得到線(xiàn)性的信號(hào),如圖9所示。如果其內(nèi)部的兩級(jí)PA是穩(wěn)定的,則整體的PA就是非常穩(wěn)定的,然而前饋技術(shù)的如下幾個(gè)缺陷使其在RFIC中的應(yīng)用極其有限:

(1)如果延時(shí)單元由無(wú)源器件組成,則會(huì)增大PA整體的損耗,如果由有源器件組成,則會(huì)因?yàn)闊o(wú)源器件的非線(xiàn)性造成失真;

(2)輸出級(jí)的減法器間的損耗,大大降低了PA的整體效率;

(3)整PA線(xiàn)性度的改善決定于每個(gè)減法器的信號(hào)的增益和相位匹配。

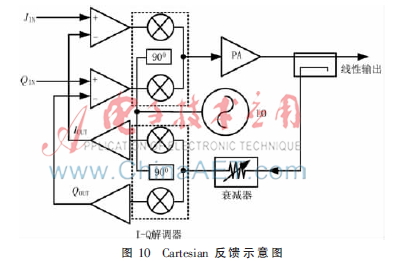

采用Cartesian負(fù)反饋技術(shù)(Cartesian Feedback)[33]可以克服前饋技術(shù)的以上缺點(diǎn),因?yàn)镃artesian Feedback 不需要使用減法器,如圖10所示,并且對(duì)環(huán)路間的失配不敏感,與Cartesian Feedback技術(shù)相似的還有極化環(huán)路反饋技術(shù)(Polar Loop Feedback)[34],這兩種技術(shù)有著相反的特性,不過(guò)都對(duì)負(fù)載和PVT的變化不敏感,而較大的缺點(diǎn)就是環(huán)路的帶寬受限,文獻(xiàn)[33]通過(guò)犧牲較大的輸出功率而實(shí)現(xiàn)帶寬超過(guò)10 MHz的PA。與改善效率的方法一樣,同樣可以通過(guò)在Cascode結(jié)構(gòu)中結(jié)合反饋和自適應(yīng)偏置技術(shù)來(lái)改善線(xiàn)性度[35]。

將RF輸出信號(hào)直接反饋到輸入端,雖然可以獲得較大的帶寬,但在RF頻率上容易造成PA不穩(wěn)定,從而產(chǎn)生振蕩,雖然文獻(xiàn)[36]通過(guò)結(jié)合偏置技術(shù)改善了這種情況,但其所采用的方法僅僅適用于驅(qū)動(dòng)級(jí)。為了克服直接負(fù)反饋在RF頻率下不穩(wěn)定的缺點(diǎn),文獻(xiàn)[37]通過(guò)直接檢測(cè)輸入和輸出端的信號(hào)相位和幅度,采用雙路閉環(huán)負(fù)反饋結(jié)構(gòu)。這種方法又稱(chēng)功率反饋(Power Feedback),這種結(jié)構(gòu)通過(guò)消除AM-AM失真的方法來(lái)實(shí)現(xiàn)輸出較大的功率而沒(méi)有群延時(shí)失真[38],不過(guò)這種方法得益于III-V類(lèi)工藝的優(yōu)點(diǎn),因此并不適用于CMOS工藝,因?yàn)镃MOS工藝本身的線(xiàn)性度較差,且其非線(xiàn)性的柵極電容會(huì)造成較大的AM-AM和AM-PM失真。

采用預(yù)失真技術(shù)(Pre-distortion)也是一種比較可行的線(xiàn)性PA結(jié)構(gòu),不過(guò)這種結(jié)構(gòu)得益于預(yù)先可估計(jì)的失真模型,從而構(gòu)建與之相反的模型電路來(lái)達(dá)到失真補(bǔ)償?shù)哪康摹H绻鸓A的非線(xiàn)性特性隨工藝、溫度和負(fù)載阻抗變化時(shí),預(yù)失真技術(shù)并不是理想的解決方案,因?yàn)楹茈y去同時(shí)構(gòu)建一個(gè)全方面的失真模型。

3 總結(jié)

隨著移動(dòng)設(shè)備的功能越來(lái)越復(fù)雜,集成度越來(lái)越高,單片實(shí)現(xiàn)RF前端模組有著重要的研究意義,又因?yàn)镽F的基帶處理單元基本都使用硅工藝,與之兼容的硅CMOS工藝是很好的解決方案。雖然CMOS工藝因?yàn)槲锢砣毕菰谛阅苌媳炔簧螴II-V類(lèi)工藝,但是隨著研究的深入,通過(guò)結(jié)合其他優(yōu)化技術(shù),使用CMOS實(shí)現(xiàn)RF的一些重要模塊已經(jīng)成為可能。

隨著新一代網(wǎng)絡(luò)(4G/LTE)的應(yīng)用和逐漸普及,移動(dòng)通信的數(shù)據(jù)空前增長(zhǎng),移動(dòng)設(shè)備對(duì)電池續(xù)航時(shí)間的要求也大大提升。LTE上行鏈路信號(hào)采用SC-FDMA調(diào)制方式,均峰比明顯高于W-CDMA。PA作為移動(dòng)終端中耗能最大的模塊之一,LTE上行鏈路信號(hào)的功率電平大部分時(shí)間都保持在較低值,極少達(dá)到峰值功率,因此,PA大部分時(shí)間工作在功率回退區(qū),從而消耗電池電能,進(jìn)而影響設(shè)備的散熱設(shè)計(jì)功耗(TDP)。

包絡(luò)跟蹤(ET)技術(shù)根據(jù)PA的輸入信號(hào)的包絡(luò)動(dòng)態(tài)調(diào)整PA的工作電壓,使PA在回退時(shí)也有著較高的效率,且ET內(nèi)部有著固有的線(xiàn)性特性,使ET PA很容易在線(xiàn)性度、效率和帶寬之間的進(jìn)行折中設(shè)計(jì),所以ET是應(yīng)用于LTE環(huán)境的一個(gè)較好的解決方案。

非線(xiàn)性是PA處理類(lèi)似于LTE這些高PAPR信號(hào)的另外一個(gè)問(wèn)題,因?yàn)殡S著輸入信號(hào)功率的加大,PA會(huì)因?yàn)閮?nèi)部的非線(xiàn)性而出現(xiàn)功率增益壓縮,從而無(wú)法線(xiàn)性放大輸入信號(hào)而出現(xiàn)失真,最終導(dǎo)致ACLR和EVM超標(biāo)。PA的線(xiàn)性度的改善可以采用反饋和數(shù)字預(yù)失真的方法,不過(guò)采用預(yù)失真的方法需要提供一個(gè)比較完善的失真模型,而反饋則會(huì)使增益下降。隨著DSP技術(shù)的成熟,數(shù)字預(yù)失真技術(shù)也逐漸成為ET PA的主流線(xiàn)性?xún)?yōu)化技術(shù)。

參考文獻(xiàn)

[1] YUNSUNG C,DAEHYUN K,JOOSEUNG K,et al.A dual power-mode multi-band power amplifier with envelope tracking for handset applications[J].IEEE Transactions on Microwave Theory and Techniques,2013,61(4):1608-1619.

[2] KANG D,DAEKYU Y,KYOUNGJOON M,et al.A highly efficient and linear class-AB/F power amplifier for multi-mode operation[J].IEEE Transactions on Microwave Theory and Techniques,2008,56(1):77-87.

[3] YU Z,METZGER A G,ZAMPARDI P J,et al.Linearity improvement of HBT-based Doherty power amplifiers basedon a simple analytical model[J].IEEE Transactions on Mic-rowave Theory and Techniques,2006,54(12):4479-4488.

[4] YOUNGOO Y,CHOI K,WELLER K P.DC boosting effect of active bias circuits and its optimization for class-ABInGaP-GaAs HBT power amplifiers[J].IEEE Transactions onMicrowave Theory and Techniques,2004,52(5):1455-1463.

[5] CHOWDHURY D,HULL C D,DEGANI O B,et al.A fullyintegrated dual-mode highly linear 2.4 GHz CMOS power amplifier for 4G WiMax applications[J].IEEE Journal of Solid-State Circuits,2009,44(12):3393-3402.

[6] Haifeng M,van der Zee R,Nauta B.Design and analysis ofa high-efficiency high-voltage class-D power output stage[J].IEEE Journal of Solid-State Circuits,2014,49(7):1514-1524.

[7] KRISHNAMURTHY V,HERSHBERGER K,EPLETT B,et al.SiGe power amplifier ICs for 4G(WIMAX and LTE) mobile and nomadic applications[C].Radio Frequency Integrated Circuits Symposium(RFIC),2010 IEEE;2010 23-

25 May 2010.

[8] RUILI W,LOPEZ J,YAN L,et al.A highly efficient 1-Watt broadband class-J SiGe power amplifier at 700 MHz[C].Silicon Monolithic Integrated Circuits in RF Systems(SiRF),2012 IEEE 12th Topical Meeting on;2012 16-18 Jan.2012.

[9] JOONGJIN N,JIN-HO S,KIM B.A handset power amplifierwith high efficiency at a low level using load-modulation technique[J].IEEE Transactions on Microwave Theory and Techniques,2005,53(8):2639-2644.

[10] YAN L,LOPEZ J,PO-HSING W,et al.A SiGe envelope-tracking power amplifier with an integrated CMOS envelopemodulator for mobile WiMAX/3GPP LTE transmitters[J].IEEE Transactions on Microwave Theory and Techniques,2011,59(10):2525-2536.

[11] NAKATANI T,RODE J,KIMBALL D F,et al.Digitally-controlled polar transmitter using a Watt-Class current-mode class-D CMOS power amplifier and guanella reverse balun for handset applications[J].IEEE Journal of Solid-State Circuits,2012,47(5):1104-1112.