一般情況下硬件電路設計,在仿真的時候大多是采用軟件仿真方式,這種方式在硬件電路相對簡單的過去還可以滿足電子工程師的需求。而在硬件電路日趨復雜的現(xiàn)在已經(jīng)越來越難以滿足實際設計需求。為此,硬件加速仿真的推出就必不可少。在硬件加速仿真領域Mentor Graphics有著豐富的經(jīng)驗,已經(jīng)把硬件仿真推進到了第四個階段——應用程序階段。在該階段中,單個硬件不再是區(qū)分因素,在硬件和操作系統(tǒng)上運行的應用程序?qū)?a class="innerlink" href="http://forexkbc.com/tags/仿真平臺" title="仿真平臺" target="_blank">仿真平臺轉(zhuǎn)換成驗證中心來工作,應用程序驅(qū)動使用新模型來減少SoC驗證任務從而為硬件仿真加速。

硬件仿真發(fā)展的四個階段

Veloce2 是Mentor公司的硬件仿真平臺,目前運行Veloce OS3 操作系統(tǒng),可針對當今復雜的片上系統(tǒng) (SoC) 設計實現(xiàn)完整的功能驗證。其自定義片上硬件仿真技術可提供高可靠的編譯、類軟件仿真似的交互式調(diào)試、超高的吞吐率以及快速驗證收斂時間。

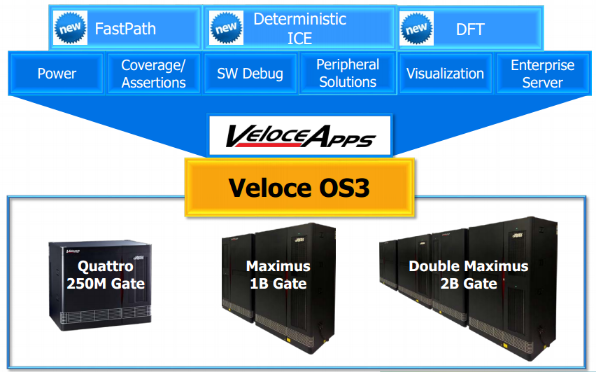

為了進一步提升硬件仿真效率,Mentor近期還推出了用于 Veloce?硬件仿真平臺的新型應用程序(APP),包括 Veloce Deterministic ICE、 Veloce DFT 和 Veloce FastPath,可以解決復雜 SoC 和系統(tǒng)設計中的關鍵系統(tǒng)級驗證難題。相比以硬件為中心的策略, Veloce OS3 上的 Veloce Apps 組合使用可以更快速地向更多工程師提供更豐富的功能。

Mentor APP架構(gòu)圖

Mentor推出的三個APP,可以說是在硬件仿真領域劃時代的進步。這對于提升硬件仿真平臺靈活度和效率有著至關重要的作用。每種新型 Veloce Apps 均可解決一項特定驗證問題。

其中,Veloce Deterministic ICE 在調(diào)試過程中加入了 100%可見性和可重復性,從而克服了電路內(nèi)仿真 (ICE) 環(huán)境的不可預知性,并可使用其他“ 基于虛擬的” 使用模型;· Veloce DFT 可提升流片之前的可測試性設計 (DFT) 驗證速度,從而最大程度地降低了災難性故障的風險,并極大減少了 DFT 插入后驗證設計的運行時間;Veloce FastPath 在驗證使用更快速的模型的多時鐘域的 SoC 設計中優(yōu)化硬件仿真性能。

除了這些已經(jīng)推出的新型 Veloce Apps之外,Mentor還將繼續(xù)擴充 Veloce Apps 庫,以進一步提升硬件仿真效率。

這些新型Veloce Apps的推出,也是和Mentor優(yōu)秀的Veloce OS 操作系統(tǒng)密不可分的。Veloce OS 操作系統(tǒng)為Veloce 平臺增加了軟件可編程性和資源管理。最新升級的 Veloce OS3 涵蓋多項創(chuàng)新:集成全新的高性能計算平臺,削減 50% 的編譯時間。“即插即用”的門電路級處理設置,能接受平面或?qū)哟位O計。此流程可減少編譯所需的內(nèi)存量,從而提高性能。新的流程可以更加輕松地加載和驗證門級設計,提高硅保真的可信度。硬件仿真和軟件操作系統(tǒng)的時間能見度和時間波形調(diào)試與以前相比快2倍,結(jié)合了從運行時間到調(diào)試周期的軟件和硬件改進,實現(xiàn)了更快可見性時間。