張麗,徐妍,馬麗珍

(中興通訊股份有限公司 上海研發(fā)中心,上海 201203)

摘要:在微波通信系統(tǒng)中,受天氣情況的影響,發(fā)送端的時鐘頻率可能隨時變化。在接收端如何進(jìn)行時鐘恢復(fù)是微波通信的難點。本文給出了一種基于FPGA的微波無線口時鐘恢復(fù)的設(shè)計。該設(shè)計使用FPGA內(nèi)的PLL和FIFO,實時調(diào)整時鐘頻率,保證接收端恢復(fù)時鐘的頻率與發(fā)送端無線口的發(fā)射時鐘信號頻率一致,且減少了PLL個數(shù),避免了PLL失鎖及其引發(fā)的復(fù)位重新鎖定過程。

關(guān)鍵詞:微波通信;時鐘恢復(fù);FPGA;PLL

0引言

微波通信是一種重要的電磁波通信手段,廣泛應(yīng)用于地球與空間站之間、城市兩個建筑物之間以及很大的無法實際布設(shè)電纜的開闊區(qū)域[1]。但是微波通信極易受天氣影響,如風(fēng)沙、雨霧等。微波通信系統(tǒng)需要在不同的天氣情況下選擇不同的工作帶寬和時鐘頻率,以確保傳輸質(zhì)量。對于這種時鐘頻率可能隨時變化的通信系統(tǒng),如何保證發(fā)送端和接收端時鐘信號一致、穩(wěn)定可靠,顯得尤為重要。本文在介紹傳統(tǒng)的微波時鐘恢復(fù)方法的基礎(chǔ)上,給出了一種基于FPGA的微波無線口時鐘恢復(fù)的設(shè)計并對設(shè)計的邏輯控制過程進(jìn)行了詳細(xì)說明。

1現(xiàn)有的時鐘恢復(fù)設(shè)計

微波通信系統(tǒng)在不同的環(huán)境條件下工作在不同的帶寬和時鐘頻率,如時鐘頻率為7 MHz、14 MHz、28 MHz、49 MHz 等。現(xiàn)有的微波時鐘恢復(fù)方法如圖1所示。該設(shè)計中包含時鐘提取模塊、分頻模塊、PLL倍頻模塊、小數(shù)分頻模塊、時鐘選擇模塊、時鐘鑒相模塊、時鐘調(diào)整模塊和監(jiān)控模塊。假設(shè)有N種不同的時鐘頻率,在每種時鐘頻率下,時鐘提取模塊從空中接收的數(shù)據(jù)信號幀中提取出的無線口時鐘信號通常是不均勻的,會存在一定的脈沖缺失[2],然后N個時鐘分頻模塊將其對應(yīng)的不均勻的時鐘信號分頻,將不均勻程度弱化。N個時鐘分頻模塊的分頻系數(shù)可以不同。PLL 倍頻模塊將分頻模塊弱化不均勻程度后得到的時鐘信號倍頻,倍頻系數(shù)也可以不同,接下來小數(shù)分頻模塊要根據(jù)實際應(yīng)用環(huán)境,利用SigmaDelta 算法實現(xiàn)小數(shù)分頻[3],將倍頻后的時鐘信號分頻到一個統(tǒng)一的頻率,如50 Hz。時鐘選擇模塊從多路時鐘信號中選擇一路,如當(dāng)前系統(tǒng)的時鐘頻率為7 MHz,則選擇7 MHz 時鐘對應(yīng)分頻得到的50 Hz信號輸出到時鐘鑒相模塊,時鐘鑒相模塊將50 Hz信號作為參考時鐘,與微波通信系統(tǒng)接收端產(chǎn)生的標(biāo)準(zhǔn)時鐘分頻得到的50 Hz信號比較,得到鑒相值,用鑒相值控制時鐘調(diào)整模塊對接收端產(chǎn)生的標(biāo)準(zhǔn)時鐘進(jìn)行調(diào)整,使其跟蹤上接收的無線口時鐘信號,即發(fā)送端的時鐘。監(jiān)控模塊實時檢測PLL倍頻模塊輸出的時鐘,一旦發(fā)現(xiàn)PLL 異常無時鐘送出時,就復(fù)位PLL。

現(xiàn)有的時鐘恢復(fù)設(shè)計通過PLL直接分頻和倍頻的操作,把不均勻的時鐘信號整合成相對均勻的時鐘。雖然不均勻的脈沖送入FPGA內(nèi)部的PLL之后,可能會導(dǎo)致PLL失鎖,但是只要不會導(dǎo)致PLL異常,從而出現(xiàn)無法恢復(fù)的情況,就能保證恢復(fù)出來的時鐘信號質(zhì)量。同時系統(tǒng)還需要一個監(jiān)控機(jī)制,實時檢測PLL發(fā)送出來的時鐘,一旦發(fā)現(xiàn)PLL異常,無時鐘送出時,就需要復(fù)位PLL,PLL從復(fù)位圖1現(xiàn)有的時鐘恢復(fù)設(shè)計到正常工作一般需要5 ms,這5 ms會導(dǎo)致軟件得到的鑒相值跳變,軟件也需要做相應(yīng)的濾波機(jī)制。

2基于FPGA的時鐘恢復(fù)設(shè)計

2.1設(shè)計組成及功能

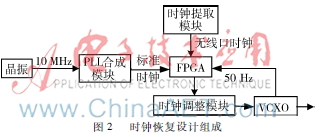

本時鐘恢復(fù)設(shè)計主要由時鐘提取模塊、晶振、PLL合成模塊、FPGA和時鐘調(diào)整模塊等構(gòu)成,如圖2所示。時鐘提取模塊從空中接收的數(shù)據(jù)信號幀中提取出無線口時鐘信號;自由震蕩的晶振輸出10 MHz時鐘;PLL合成模塊根據(jù)接收到的無線口帶寬模式,輸出標(biāo)準(zhǔn)時鐘信號;FPGA完成時鐘恢復(fù),并把恢復(fù)后的時鐘分頻到50 Hz,與本地VCXO分頻得到的50 Hz信號進(jìn)行鑒相,輸出的鑒相值控制時鐘調(diào)整模塊,最終使本地時鐘跟蹤上接收的無線口時鐘信號。

2.2FPGA控制

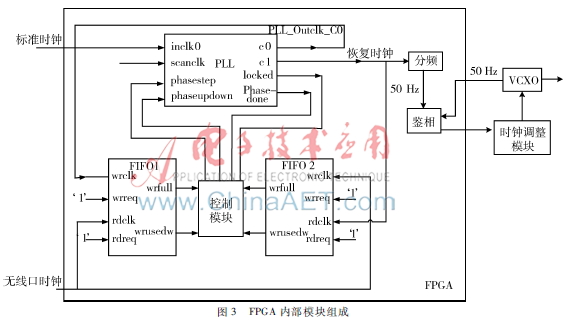

FPGA主要由FIFO模塊、控制模塊、可調(diào)相位PLL模塊、分頻模塊和鑒相模塊組成,如圖3所示。其中,F(xiàn)IFO1的空/滿決定了可調(diào)相位PLL的相位調(diào)整方向;FIFO2的空/滿決定了可調(diào)相位PLL的相位調(diào)整時機(jī);控制模塊根據(jù)兩個FIFO的空/滿以及水位信息輸出調(diào)整信息給可調(diào)相位PLL;可調(diào)相位PLL的輸出即是與無線口時鐘頻率一致的恢復(fù)時鐘;分頻模塊將恢復(fù)時鐘分頻到50 Hz。

這里FPGA選用ALTERA stratix IV 芯片,此系列芯片的可調(diào)相位PLL具有動態(tài)相移功能[4],使單個PLL輸出的輸出相位能夠相對于參考時鐘動態(tài)地被調(diào)整。每次相位調(diào)整只偏移VCO頻率的1/8,并且輸出時鐘在該相位重配置過程中是有效的。PLL的控制端口:PHASESTEP為高電平時使能動態(tài)相移;

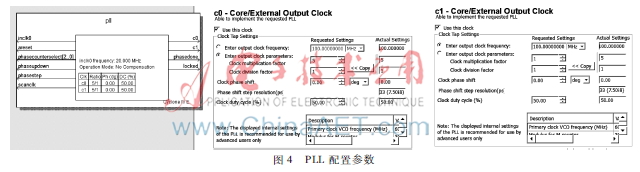

SCANCLK是與PHASESTEP相結(jié)合使用的內(nèi)核自由時鐘,最大100 MHz;PHASEUPDOWN選擇動態(tài)相移方向,1為UP,0為DOWN,且在SCANCLK上升沿寄存在PLL中。 PLL的輸出端口:PHASEDONE從低變高時表示相位調(diào)整完成,可以啟動下一次動態(tài)相移;c0/c1為輸出時鐘端口。在相位可調(diào)PLL IPCORE生成過程中需要配置PLL具有動態(tài)相位配置功能,且c0端口為輸入標(biāo)準(zhǔn)時鐘信號的1倍頻,而c1端口設(shè)置的輸出頻率要與c0端口一致,如圖4所示。

2.3時鐘恢復(fù)調(diào)整過程

可調(diào)相位PLL剛上電時,其輸出就是輸入標(biāo)準(zhǔn)時鐘信號,也就是將標(biāo)準(zhǔn)時鐘信號直接輸出到FIFO1的寫時鐘端口WR_CLK和FIFO2的讀時鐘端口RD_CLK,時鐘提取模塊輸出的無線口時鐘信號則同時輸入到FIFO1的讀時圖4PLL 配置參數(shù)

鐘端口RD_CLK 以及FIFO2的寫時鐘端口WR_CLK。

假設(shè)此時FIFO1中保存的數(shù)據(jù)個數(shù)為n1,F(xiàn)IFO1的存儲深度為m,即0<n1<m。FIFO1在標(biāo)準(zhǔn)時鐘信號上升沿的控制下進(jìn)行數(shù)據(jù)寫操作,同時在無線口時鐘信號上升沿的控制下進(jìn)行數(shù)據(jù)讀操作,如果標(biāo)準(zhǔn)時鐘信號比無線口時鐘信號頻率低,則經(jīng)過一段時間后,F(xiàn)IFO1中存儲的數(shù)圖5恢復(fù)時鐘示意圖

據(jù)個數(shù)會變少,甚至為0(即空);如果標(biāo)準(zhǔn)時鐘信號比無線口時鐘信號頻率高,則經(jīng)過一段時間后,F(xiàn)IFO1中存儲的數(shù)據(jù)個數(shù)會變多,甚至為m(即滿)。而FIFO1通過wrusedw[5]端口實時將其中保存的數(shù)據(jù)個數(shù)上報給相位調(diào)整控制模塊,上報的數(shù)據(jù)個數(shù)就能夠反映無線口時鐘信號與標(biāo)準(zhǔn)時鐘信號的頻率(相位)差異信息。相位調(diào)整控制模塊在收到FIFO1上報的數(shù)據(jù)個數(shù)變少時,據(jù)此判斷出標(biāo)準(zhǔn)時鐘信號比無線口時鐘信號頻率低,則需提高恢復(fù)時鐘信號的頻率;相位調(diào)整控制模塊在收到FIFO1上報的數(shù)據(jù)個數(shù)變多時,據(jù)此判斷出標(biāo)準(zhǔn)時鐘信號比無線口時鐘信號頻率高,則需降低恢復(fù)時鐘信號的頻率,即確定了對恢復(fù)時鐘信號的頻率調(diào)整方向。

假設(shè)FIFO2中保存的數(shù)據(jù)個數(shù)為n2(n2<m),F(xiàn)IFO2在恢復(fù)時鐘信號上升沿的控制下進(jìn)行數(shù)據(jù)讀操作,同時在無線口時鐘信號上升沿的控制下進(jìn)行寫操作,F(xiàn)IFO2通過wrusedw端口實時將其中保存的數(shù)據(jù)個數(shù)上報給相位調(diào)整控制模塊。當(dāng)出現(xiàn)無線口時鐘信號與恢復(fù)時鐘信號的頻率不同時,F(xiàn)IFO2上報的數(shù)據(jù)個數(shù)就會發(fā)生變化,此時需要調(diào)節(jié)。只要相位調(diào)整控制模塊收到FIFO2上報的數(shù)據(jù)個數(shù)不是n2,即發(fā)生了變化,相位調(diào)整控制模塊就會根據(jù)由FIFO1確定的頻率調(diào)整方向?qū)謴?fù)時鐘信號的周期、占空比等進(jìn)行調(diào)整,使恢復(fù)時鐘信號與無線口時鐘信號頻率一致。

例如:圖5中,當(dāng)無線口時鐘信號出現(xiàn)脈沖連續(xù)空缺時,需降低恢復(fù)時鐘信號的頻率,假設(shè)恢復(fù)時鐘信號原來的周期T=10 ns,一個周期內(nèi)高脈沖持續(xù)5 ns,低脈沖持續(xù)5 ns,則每次調(diào)整時鐘頻率的1/8,直到FIFO2上報的數(shù)據(jù)個數(shù)不發(fā)生變化,則停止對恢復(fù)時鐘信號的調(diào)節(jié)。恢復(fù)時鐘信號在經(jīng)過上述調(diào)節(jié)后會逐漸趨近于無線口時鐘信號,如圖5所示,雖然某些經(jīng)過調(diào)整的周期長度與其他周期不同,但是能夠保證在比較長的一段時間內(nèi),恢復(fù)時鐘信號與無線口時鐘信號的脈沖個數(shù)相同,即這兩個信號的頻率相同。實際中,該時間的具體數(shù)值與FIFO1、FIFO2的存儲容量大小有關(guān)。此外,需要說明的是,標(biāo)準(zhǔn)時鐘信號與無線口時鐘信號輸入FIFO1的讀、寫時鐘端口可以交換,恢復(fù)時鐘信號與無線口時鐘信號輸入FIFO2的讀、寫時鐘端口也可以交換。

3結(jié)論

本文給出了一種基于FPGA的微波無線口時鐘恢復(fù)的設(shè)計。該設(shè)計使用FPGA內(nèi)的PLL和FIFO,實時調(diào)整時鐘頻率,減少了PLL個數(shù),避免了PLL失鎖及其引發(fā)的復(fù)位重新鎖定過程,提高了微波通信系統(tǒng)的穩(wěn)定性,降低了系統(tǒng)成本和復(fù)雜度。

參考文獻(xiàn)

[1] 李兵.微波通信技術(shù)的發(fā)展與展望[J].電力系統(tǒng)通信,2011, 32(12):4043.

[2] Provigent Ltd. PVG610 Data Sheet PVG610_DSH_002_I [Z].2009.

[3] 李慧.基于VHDL的小數(shù)分頻器設(shè)計[J].微計算機(jī)信息,2010, 26(10):192193.

[4] Altera Corporation. Stratix IV Device Handbook Volume 1 [Z]. 2015.

[5] Altera Corporation. SCFIFO and DCFIFO IP Cores User Guide [Z]. 2014.