文獻標(biāo)識碼: A

文章編號: 0258-7998(2014)08-0051-03

在數(shù)字通信中,位同步是要在接收端確定每一個碼元的起止時刻,從而在數(shù)據(jù)流中區(qū)分出獨立的碼元,它起著為接收信號提供基準(zhǔn)的作用[1]。主要體現(xiàn)在產(chǎn)生與接收的數(shù)字信號時鐘同頻同相的恢復(fù)時鐘,從而準(zhǔn)確地解出數(shù)據(jù)流中攜帶的數(shù)字信息。

常用的位同步時鐘恢復(fù)電路主要有數(shù)字鎖相環(huán)和1比特位同步器,作為當(dāng)前的主流技術(shù)而廣泛使用,但它們的優(yōu)缺點也是顯而易見的。本文在分析了兩種位同步時鐘恢復(fù)方法的原理及其優(yōu)缺點的基礎(chǔ)上,提出了利用DDS高精度分頻原理實現(xiàn)快速時鐘恢復(fù)的設(shè)計方案,能夠快速穩(wěn)定地從數(shù)據(jù)流中恢復(fù)出時鐘,并且適用于各種頻率要求,通用性強。

1 位同步性能分析

數(shù)字鎖相環(huán)是一種閉環(huán)結(jié)構(gòu)的位同步電路,1比特位同步器則基于開環(huán)結(jié)構(gòu)。下面對這兩種電路原理進行介紹,并分析其優(yōu)缺點。

1.1 數(shù)字鎖相環(huán)法

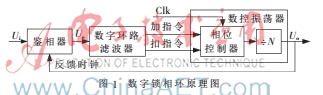

通常數(shù)字鎖相環(huán)主要由鑒相器、數(shù)字環(huán)路濾波器、數(shù)控振蕩器三部分組成,其原理圖如圖1所示。

首先將輸入信號與反饋時鐘進行鑒相,得出時鐘相位的超前滯后信息;然后在環(huán)路濾波器中對超前滯后信息進行計數(shù),當(dāng)達到模值K時產(chǎn)生加扣指令,數(shù)控振蕩器根據(jù)加扣指令插入或扣除一個時鐘脈沖,從而實現(xiàn)時鐘相位的調(diào)整[2]。

數(shù)字鎖相環(huán)是一個閉環(huán)反饋結(jié)構(gòu),這種結(jié)構(gòu)能夠使同步時鐘在碼元相位出現(xiàn)抖動或者碼元消失時不會出現(xiàn)較大變化,仍然可以穩(wěn)定地輸出同步脈沖[3]。也正是因為這種反饋結(jié)構(gòu),使得數(shù)字鎖相環(huán)法的同步建立時間變得很長,往往需要十幾甚至幾十個信號周期。

數(shù)字鎖相環(huán)法的原理也決定了它的同步帶寬較窄,對于寬范圍的不同頻率的信號,需要花大量資源去實現(xiàn)脈沖步長的控制以提高同步速度和精度,造成結(jié)構(gòu)復(fù)雜。

1.2 比特位同步法

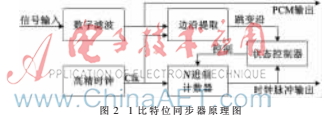

與數(shù)字鎖相環(huán)的閉環(huán)結(jié)構(gòu)不同,1比特位同步法是一種開環(huán)結(jié)構(gòu),它主要由雙邊沿提取電路、狀態(tài)寄存器和N進制計數(shù)器組成,原理圖如圖2所示。

當(dāng)輸入信號發(fā)生跳變時,根據(jù)邊沿脈沖產(chǎn)生一個清零信號,對計數(shù)器進行清零,以輸出一個反映輸入信號相位的時鐘短脈沖。狀態(tài)控制器可以在接收碼元出現(xiàn)連“1”或是連“0”時保證仍然會有固定的反映輸入信號時鐘頻率的短脈沖輸出[4]。

1比特位同步器的這種開環(huán)結(jié)構(gòu)可以在每一個輸入信號跳變沿校準(zhǔn)碼同步時鐘的相位。所以,它的同步建立時間很短,可以在出現(xiàn)第一個跳變的碼元時就輸出正確的碼同步信號。同時,這種結(jié)構(gòu)在輸入信號由交替變化的“0”和“l(fā)”組成時,邊沿脈沖可以有效地校正頻差。

但是由于跳變沿提取電路的每一個邊沿脈沖輸出都會對計數(shù)器清零,如果跳變沿出現(xiàn)嚴(yán)重抖動,則邊沿脈沖信號會與計數(shù)器原本的輸出產(chǎn)生沖突,造成輸出時鐘信號占空比大幅度變化,嚴(yán)重時甚至?xí)霈F(xiàn)毛刺,對后續(xù)電路的功能實現(xiàn)無疑會產(chǎn)生致命的影響。

另外,位同步器輸出的是脈沖信號,所以需要添加一個時鐘整形電路,將輸出時鐘脈沖變?yōu)檎伎毡?0%的時鐘周期信號。

2 DDS高精度分頻設(shè)計

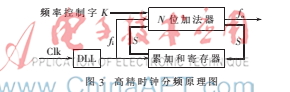

本方案時鐘恢復(fù)的高精度任意分頻利用DDS的相位累加器原理實現(xiàn),原理框圖如圖3所示。

該時鐘分頻器由DLL、頻率控制字寄存器、N位加法器以及累加和寄存器組成。晶振經(jīng)過DLL倍頻后作為分頻器的工作時鐘,在每個時鐘的上升沿,累加的和與頻率控制字進行相加,并將結(jié)果保存到累加和寄存器[5]。這個過程中,累加和S會從0開始逐漸增加直到溢出,然后進行下一輪的累加。當(dāng)頻率控制字和加法器位數(shù)確定以后,累加溢出的頻率就確定了,因為溢出位會按照特定的頻率由“0”和“1”交替變化,所以直接將累加和的溢出位作為時鐘輸出,就可以得到一個占空比為50%的分頻時鐘輸出,而不需要添加時鐘整形電路。

設(shè)輸入時鐘頻率為fi,頻率控制字為K,時鐘輸出為fo,N為累加器字長,則有:

![}K_0XB]%5D0)4KF(HYX4MML.png }K_0XB]%5D0)4KF(HYX4MML.png](http://files.chinaaet.com/images/2017/01/25/6362094075407800003770927.png)

在實際應(yīng)用中,頻率控制字K可由式(1)求出。

當(dāng)分頻系數(shù)確定時,K不可能取得整數(shù),只是一個逼近值。但是由于N的取值關(guān)系,可以達到較高的分辨率。同時分頻系數(shù)越小,精度越低,反之精度越高。

3 基于DDS的時鐘恢復(fù)設(shè)計

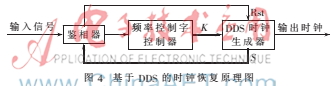

本文設(shè)計的位同步時鐘提取電路結(jié)合了超前滯后鎖相環(huán)與1比特位同步器的優(yōu)點,在使用基于DDS原理分頻的1比特位同步器時鐘恢復(fù)方案的基礎(chǔ)上添加了一個鑒相器,根據(jù)鑒相器的結(jié)果調(diào)整頻率控制字,在一定的周期內(nèi),通過控制頻率控制字來調(diào)節(jié)時鐘頻率和相位,最終實現(xiàn)位同步時鐘的生成。基于DDS的時鐘恢復(fù)設(shè)計原理框圖如圖4所示。

圖4中K為頻率控制字,S為累加和,Rst為復(fù)位信號。其工作原理為:首先根據(jù)待測信號頻率計算出頻率控制字K,當(dāng)有輸入信號出現(xiàn)跳變時,鑒相器啟動DDS時鐘生成器開始生成相應(yīng)頻率的時鐘;然后在每個輸入信號跳變沿,鑒相器讀取相位累加和的值進行判讀,頻率控制字控制器根據(jù)鑒相器判讀結(jié)果改變DDS分頻器的頻率控制字來調(diào)節(jié)相位,從而實現(xiàn)恢復(fù)時鐘的頻率和相位的鎖定。

3.1 鑒相器

鑒相器用來提取輸入數(shù)字信號與時鐘信號相位之差。與常用的對兩個信號進行比較的原理不同,本文設(shè)計的鑒相器是建立在DDS分頻基礎(chǔ)上的。由于DDS分頻原理是通過頻率控制字的累加溢出來生成時鐘信號,所以可以將其累加和S看作是時鐘相位的實時體現(xiàn),鑒相器只需在輸入信號發(fā)生跳變時,讀取此時相位累加器的累加值并進行判斷,就可以得出時鐘信號為超前還是滯后,并能同時確定相位誤差的值。

信號跳變沿到來時,首先根據(jù)此時溢出位的值判斷同步時鐘處于前半周期還是后半周期。當(dāng)溢出位為0時為前半周期,為1時則為后半周期。然后根據(jù)累加和值S的大小判斷相位關(guān)系。

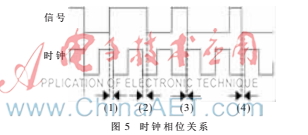

圖5所示為兩種典型的跳變沿到來時信號與時鐘可能的相位關(guān)系,其中(1)所示為前向抖動,此時信號的跳變略早于時鐘信號;(2)為后向抖動,輸入信號的跳變沿略晚于時鐘信號。如果以0~M(N位全為1的數(shù))表示完整的時鐘相位,則(1)所示相位差為M-S,(2)所示相位差為S。

3.2 頻率控制字控制

相位控制以鑒相器輸出的鑒相結(jié)果作為依據(jù)改變頻率控制字來實現(xiàn)。首先設(shè)置一個抖動容限值L,當(dāng)相位差小于L時,表示抖動在允許范圍以內(nèi),不對頻率控制字做改變,即不對時鐘相位做調(diào)整。當(dāng)相位誤差大于L時,如果此時為前向抖動,則將頻率控制字左移1位,使相位累加提前溢出,最終使時鐘相位前移;如果為后向抖動,則不對頻率控制字做改變,而是鑒相器輸出復(fù)位信號到時鐘生成器來快速對齊時鐘相位,與1比特位同步法相同。

4 性能分析及仿真測試

與常用的位同步時鐘恢復(fù)電路相比較,本方案設(shè)計的基于DDS分頻原理的位同步時鐘恢復(fù)電路有以下優(yōu)點:

(1)極大地增加了同步帶寬。基于DDS的任意分頻方法使得本方案設(shè)計的位同步器可以適用于多種頻率要求,只需要改變頻率控制字就可以得到任意頻率的分頻時鐘,而且可以達到很高的頻率分辨率。分頻的分辨率同時也是分頻的最小值,如式(2)所示:

分頻的最大值受限于奈奎斯特定理,理論上為本地高頻時鐘fi的一半,實際中約為40%。

(2)有效降低了頻差的影響。當(dāng)輸入信號出現(xiàn)較長的連續(xù)0或者1時,此時沒有跳變沿來校正時鐘相位,頻差會在連續(xù)時鐘周期內(nèi)疊加。而基于DDS的分頻方法在多個時鐘周期的累加過程中,每一次累加溢出時,其余值會進入下一個周期進行累加,而不是清零,這樣可以使誤差相互抵消,因此即使單個時鐘周期誤差較大,也不會使誤差疊加,將頻差的影響降到最低[6]。

(3)可以實現(xiàn)快速、穩(wěn)定的位同步。當(dāng)時鐘相位誤差較大時,能夠通過改變頻率控制字與復(fù)位時鐘生成電路,在1~2個周期內(nèi)快速實現(xiàn)同步,比鎖相環(huán)法反應(yīng)更加迅速;與開環(huán)結(jié)構(gòu)的1比特位同步方法相比,在大幅相位抖動時不會產(chǎn)生毛刺,時鐘更加穩(wěn)定。

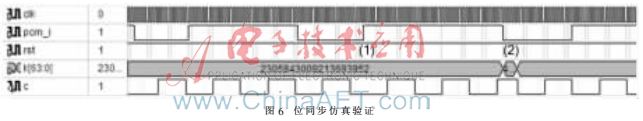

本文在ISE環(huán)境下采用VHDL語言設(shè)計了位同步提取電路,使用Xilinx公司的Spartan3E系列FPGA芯片XC3S250E予以實現(xiàn),并進行了仿真實驗驗證,如圖6所示。

圖6中clk為本地時鐘,pcm_i為輸入信號,K[63:0]為頻率控制字,c為恢復(fù)時鐘輸出。可以看出,當(dāng)輸入信號跳變時時鐘生成電路開始工作,生成固定頻率的時鐘信號,時鐘上升沿位于碼元周期的中間位置,可以更準(zhǔn)確地讀取碼元。在輸入信號的跳變沿,會根據(jù)時鐘信號與輸入信號的相差來調(diào)整時鐘相位,圖中(1)所示位置為后向抖動,時鐘生成器被復(fù)位,以對齊時鐘相位;(2)所示為大幅度的前向抖動,此時頻率控制字被左移1位,使時鐘信號相位前移。

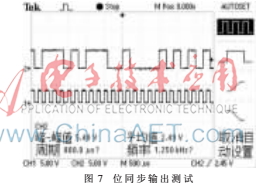

在實際工作時根據(jù)需要的頻率計算出頻率控制字即可,圖7所示為實際測試時使用示波器測量的位同步情況,圖中上面為輸入信號,下面為位同步時鐘。結(jié)果表明,本方案設(shè)計的電路能夠?qū)崿F(xiàn)時鐘恢復(fù)的功能,其性能穩(wěn)定。

本文提出了一種基于DDS高精度任意分頻的時鐘恢復(fù)方案,與常用的位同步方法相比,具有時鐘分頻精度高、適用頻率范圍寬、同步速度快、同步時鐘穩(wěn)定度好以及設(shè)計簡單等優(yōu)點。并且該方案經(jīng)過仿真以及實際測試驗證其正確可行,是數(shù)字時鐘恢復(fù)方案的一種很好的選擇。

參考文獻

[1] 李超,謝雪松,張小玲.一種DDS任意波形發(fā)生器的ROM優(yōu)化方法[J].電子技術(shù)應(yīng)用,2013,39(2):12-21.

[2] 陳華君,楊濤.一種基于FPGA的全數(shù)字鎖相環(huán)設(shè)計[J].物聯(lián)網(wǎng)技術(shù),2011,1(10):76-78.

[3] 張志文,曾志兵,羅隆福,等.基于新型全數(shù)字鎖相環(huán)的同步倍頻技術(shù)[J].電力自動化設(shè)備,2010,30(2):123-126.

[4] 靖文,李斌,屈薇,等.一種快速位同步時鐘提取方案及實現(xiàn)[J].電子設(shè)計應(yīng)用,2007(12):84-87.

[5] 柳春,甘泉.基于FPGA的雷達信號源設(shè)計[J].電子技術(shù)應(yīng)用,2013,39(11):47-49.7

[6] 黃守麟.基于FPGA的超高精度任意小數(shù)分頻器的設(shè)計[C].第二屆全國信號處理與應(yīng)用學(xué)術(shù)會議,2008:485-487.