文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.006

中文引用格式: 吳均,陳德恒,莊哲民. 高速串行總線無源通道建模及校準(zhǔn)[J].電子技術(shù)應(yīng)用,2016,42(8):33-36,40.

英文引用格式: Wu Jun,Chen Deheng,Zhuang Zhemin. Modeling and calibration of high-speed passive channel[J].Application of Electronic Technique,2016,42(8):33-36,40.

0 引言

高速串行總線的速率越來越高,從前幾年大家關(guān)心的10Gbase-KR到現(xiàn)在更高速率的25\28G傳輸,高速串行總線帶來的設(shè)計挑戰(zhàn)也越來越多。

從傳輸通道來說,挑戰(zhàn)主要來自于信號的波長和通道上各元素的物理尺寸越來越接近。

無源通道的性能對高速串行總線的信號傳輸至關(guān)重要,而我們要優(yōu)化無源通道的性能,就需要能對通道進(jìn)行準(zhǔn)確的建模。而要驗證通道建模的準(zhǔn)確性,我們就得先對通道進(jìn)行準(zhǔn)確的測試,然后通過仿真測試校準(zhǔn)來驗證仿真建模的準(zhǔn)確性。

1 TRL技術(shù)簡介

我們可以通過網(wǎng)絡(luò)分析儀來得到待測物(DUT)的通道特性(S參數(shù))。但如果DUT是非同軸接口的元器件,如PCB板上的一段走線、各種表貼器件等,則需要通過夾具將被測物與網(wǎng)絡(luò)分析儀的同軸接口進(jìn)行連接。

圖1中,測試的結(jié)果是圖中所示區(qū)域,而我們最終想要得到的數(shù)據(jù)是真實DUT的數(shù)據(jù)。從測到的區(qū)域數(shù)據(jù)最終得到DUT的參數(shù),這個過程,我們就叫做去嵌。嚴(yán)格來說,去嵌也是校準(zhǔn)的一種,只不過通常的儀器校準(zhǔn),是去掉儀器本身與線纜的影響;而去嵌,則是去掉儀器本身、線纜以及夾具的影響。

去嵌的方法很多,TRL是相對來說精度比較高,也具備一定難度的一種方法,也是行業(yè)里面普遍認(rèn)可的一種方法,可以用來研究走線的細(xì)節(jié)差異。

1.1 TRL技術(shù)及原理簡介

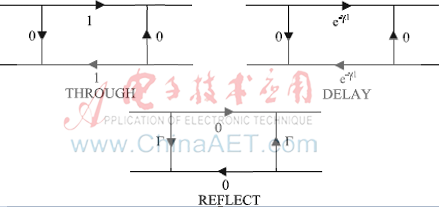

現(xiàn)在的校準(zhǔn)技術(shù)中,通常是對傳輸參數(shù)、反射參數(shù)、隔離參數(shù)進(jìn)行測量,確定一些誤差模型,再通過這些模型進(jìn)行矩陣計算。誤差模型如圖2所示。

圖2 誤差模型示意圖

TRL校準(zhǔn)方式通過測量2個傳輸標(biāo)準(zhǔn)件(Thru、Line/match)和一個反射標(biāo)準(zhǔn)件(Reflect)來確定10項誤差模型,從而進(jìn)行校準(zhǔn),并且可以通過load的測量將誤差模型增加至12個。使用不同頻段的多條延時線來避免了低頻與高頻不一致所帶來的誤差,所以在大部分情況下TRL比SOLT的校準(zhǔn)效果更好。但由于不同場景下使用的測試夾具不同,所以通常需要根據(jù)測試夾具的情況設(shè)計相應(yīng)的TRL校準(zhǔn)件。TRL誤差模型示意圖如圖3所示。

圖3 TRL誤差模型示意圖

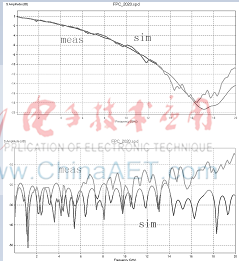

1.2 測試精度展示

TRL校準(zhǔn)的第一個指標(biāo)就是TRL校準(zhǔn)的精度,通過校準(zhǔn)完后測量直通校準(zhǔn)件來驗證。由于夾具已經(jīng)被去嵌,此時測量直通件的插損應(yīng)該無限趨近于0,回?fù)p應(yīng)該盡量小。圖4為一博科技某款測試板的校準(zhǔn)精度。

圖4 測試結(jié)果示例

可以看到,回?fù)p基本小于-50 dB,插損在20 GHz內(nèi)也小于±0.02 dB,屬于較好的校準(zhǔn)結(jié)果。

2 仿真介紹及仿真測試校準(zhǔn)

除了測試的方式,我們還可以通過仿真來取得無源通道的參數(shù),Cadence的Power SI及Power SI 3D-EM就是這樣的仿真工具。

2.1 三維場仿真算法簡介

2.1.1 FEM算法簡介

(1)3D-EM使用有限元算法求解,支持零階和一階的有限元網(wǎng)格邊界條件。

①零階:電場在網(wǎng)格各邊上保持恒定,在網(wǎng)格內(nèi)部線性變化。

②一階:電場在網(wǎng)格各邊上線性變化,在網(wǎng)格內(nèi)部以多階趨勢變化(相同網(wǎng)格條件下,一階精度比零階更高)。

(2)支持自適應(yīng)網(wǎng)格,確保求解收斂性和精度。

(3)使用先進(jìn)的頻率掃描方法,比傳統(tǒng)方法求解快一個量級。

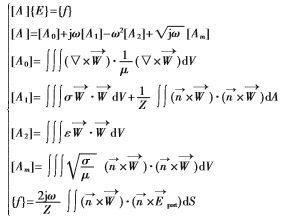

(4)典型的有限元求解表達(dá)式如下所示:

其中,[A]表示已知的有限元系數(shù)矩陣;{E}表示需要求解的電磁場矩陣;{f}標(biāo)識激勵向量。

如上所示,系數(shù)矩陣通常可以分成4組隨頻率變化的參數(shù),如下:

:角頻率(angular frequency)

:角頻率(angular frequency)

μ:磁導(dǎo)率(permeability)

σ:電導(dǎo)率(conductivity)

Z:表面阻抗(surface impedance)

ε:介電常數(shù)(permittivity)

n:表面的外方向法向量(outer normal of a surface)

W:有限元基函數(shù)(finite element basis function)

Eport:端口位置添加的激勵(port excitation)

2.1.2 自適應(yīng)網(wǎng)格剖分算法

(1)3D-EM使用自適應(yīng)網(wǎng)格剖分算法以保證仿真精度和更好的內(nèi)存利用效率;

(2)自適應(yīng)網(wǎng)格剖分算法根據(jù)上一次的網(wǎng)格結(jié)果求解得到的電磁場,對關(guān)鍵區(qū)域的網(wǎng)格進(jìn)行更精細(xì)的劃分;

(3)迭代直至得到收斂的網(wǎng)格。

自適應(yīng)網(wǎng)格剖分次數(shù)對插入損耗結(jié)果的影響示例如圖5所示。

圖5 自適應(yīng)網(wǎng)格剖分次數(shù)對插入損耗結(jié)果的影響

在這個例子中,自適應(yīng)網(wǎng)格剖分算法在第3次迭代時,求解頻率(1 000 MHz)對應(yīng)的S參數(shù)與前一次網(wǎng)格剖分的結(jié)果差異小于設(shè)定的收斂判斷依據(jù)(0.01),到達(dá)收斂要求,網(wǎng)格剖分完成。

2.2 仿真測試校準(zhǔn)結(jié)論

2.2.1 跨分割結(jié)構(gòu)

該結(jié)構(gòu)的難點在與分割區(qū)域的諧振對傳輸性能的影響,以及旁邊區(qū)域的過孔個數(shù)以及分布都會影響回流的分布,從而影響諧振的幅值。結(jié)構(gòu)示意圖如圖6所示。

圖6 跨分割結(jié)構(gòu)示意圖

跨分割結(jié)構(gòu)仿真結(jié)果如圖7所示,這樣的仿真結(jié)果較為精確。

圖7 跨分割結(jié)構(gòu)仿真結(jié)果

2.2.2 走線與過孔結(jié)構(gòu)

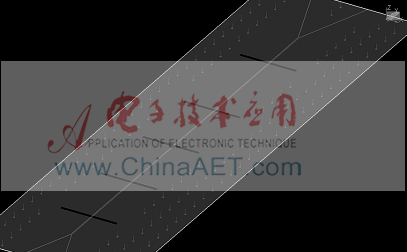

過孔在仿真中天然就是比較難的部分,并且在該模型中有微帶線的存在,微帶線仿真比帶狀線仿真更加不容易做準(zhǔn)確。該結(jié)構(gòu)示意圖如圖8所示。

圖8 走線與過孔結(jié)構(gòu)示意圖

走線與過孔結(jié)構(gòu)仿真結(jié)果如圖9所示,仿真精度較高,與業(yè)界標(biāo)桿區(qū)別不大。

圖9 走線與過孔結(jié)構(gòu)仿真結(jié)果

2.2.3 20*20網(wǎng)格銅

由于網(wǎng)格銅的存在,對于信號回流的計算更加復(fù)雜,該仿真難度較大。網(wǎng)格銅結(jié)構(gòu)示意圖如圖10所示。網(wǎng)格銅結(jié)構(gòu)仿真結(jié)果如圖11所示,可以看到,仿真精度也非常高。

圖10 網(wǎng)格銅結(jié)構(gòu)示意圖

圖11 網(wǎng)格銅結(jié)構(gòu)仿真結(jié)果

3 提高仿真效率

仿真除了精度之外,仿真所用的時間與資源也是一個重要的指標(biāo)。3D-EM提供了cut-and-stitch 流程,可以將一個長鏈路切分成若干段分別進(jìn)行求解,再自動合并成一個完整的S參數(shù),而且可以選擇每段分別用3D-EM的3D算法或者PowerSI的2.5D算法求解,可以極大的提高仿真效率。

另外,3D-EM還支持多機分布式計算,可以進(jìn)一步提高仿真效率。本例由于資源限制,沒有使用分布式計算。

使用cut-and-stitch 流程和直接求解整個鏈路的仿真結(jié)果和仿真效率對比如圖12所示。

圖12 仿真結(jié)果及仿真效率對比

可以看到,使用cut-and-stitch流程仿真結(jié)果和整個鏈路直接求解的精度非常接近,但是仿真時間可以從8個多小時減少到2個小時,如果某幾段均勻傳輸線部分使用2.5D算法求解,總的仿真時間可以進(jìn)一步減小到35分鐘,大大提高了效率。

4 結(jié)論

本文得出以下主要結(jié)論:

(1)精確的測試才能對設(shè)計與仿真提供真正有指導(dǎo)意義的結(jié)果。使用TRL校準(zhǔn)可以大幅提高測試結(jié)果的精度。

(2)精確的仿真可以大大提高設(shè)計的效率,使用PowerSI 3D-EM可以得出精確的仿真結(jié)果。

(3)3D-EM的cut-and-stitch流程可以大大提高仿真的效率,并且保證結(jié)果的精度。

參考文獻(xiàn)

[1] 吳均,王輝,周佳永.Cadence印刷電路板設(shè)計:Allegro PCB Editor設(shè)計指南[M].北京:電子工業(yè)出版社,2012.

[2] 鐘章民,肖定如,王輝.Cadence高速電路設(shè)計:Allegro Sigrity SI/PI/EMI設(shè)計指南[M].北京:電子工業(yè)出版社,2014.

[3] MORGAN C W.Obtaining accurate device-only S-parameter data to 15-20 GHz using In-Fixture measurement techniques.DESIGNCON 2004.

[4] Liu Di.How to design and verify TRL cal kit also implementation of TRL calibration.

[5] An-Yu Kuo.PowerSI-3DFEM Theory, Accuracy & Performance.