陳術(shù)濤,俞鵬先,沈志,王春聯(lián),金敏

(中國航天科工集團第九總體設(shè)計部,湖北 武漢 430040)

摘要:詳細介紹了TI公司TMS320C6678多核DSP高速外設(shè)模塊EMIF16(外部存儲器接口)的功能及特性,利用EMIF模塊擴展存儲空間大、通信速度快、硬件接口電路簡單、性能穩(wěn)定等特點,設(shè)計并實現(xiàn)了一種基于EMIF模塊的DSP與FPGA異步通信接口,重點描述了接口通信系統(tǒng)架構(gòu)設(shè)計和具體軟件實現(xiàn)。測試驗證表明基于該接口可進行DSP與FPGA之間多種格式數(shù)據(jù)傳輸,接口運行穩(wěn)定可靠,擴展了TMS320C6678多核DSP處理芯片與外部器件通信系統(tǒng)接口的設(shè)計方式。

關(guān)鍵詞:EMIF;DSP;FPGA;異步接口

中圖分類號:TN911; TP39文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2017.07.007

引用格式:陳術(shù)濤,俞鵬先,沈志,等.基于高速外設(shè)模塊的多核DSP與FPGA通信系統(tǒng)設(shè)計[J].微型機與應用,2017,36(7):22-25.

0引言

隨著信息與通信技術(shù)的快速發(fā)展和進步,其在圖像處理、模式識別、雷達信號處理、電子對抗、無線通信、導航定位等領(lǐng)域得到越來越深入的應用,隨之而來的對硬件平臺高效穩(wěn)定通信能力的需求也在同步增長。目前,信號處理系統(tǒng)的硬件平臺大多采用高度集成的嵌入式系統(tǒng),基于DSP+FPGA的硬件架構(gòu)設(shè)計憑借其超強的處理能力和廣泛的工程應用等優(yōu)勢,已經(jīng)成為當前通用數(shù)字信號處理平臺的首選。TMS320C6678多核高速DSP芯片是目前TI公司最新推出的高性能數(shù)字信號處理芯片,處理能力領(lǐng)先,基于該芯片的硬件處理平臺市場應用前景廣泛。本文針對TMS320C6678DSP芯片和Xilinx公司Kintex7系列FPGA組成的信號處理系統(tǒng)進行研究,設(shè)計了一種基于EMIF16模塊的DSP與FPGA通信接口。該接口充分利用EMIF接口高速、穩(wěn)定、設(shè)計簡單等特性,同時配合FPGA邏輯處理能力強、可編程等優(yōu)點進行接口邏輯設(shè)計,工作性能穩(wěn)定,數(shù)據(jù)處理能力強,功能靈活可擴展,可適應多種通信需求,很好地解決了DSP與FPGA之間的通信問題。

1EMIF16接口模塊特征

1.1EMIF16接口簡介

圖1EMIF16接口模塊框圖EMIF16是DSP芯片自帶的外部存儲器接口模塊,其主要功能是支持內(nèi)核CPU對外部擴展存儲空間的訪問,EMIF16可與ASRAM、NOR Flash、NARD Flash等類型的異步存儲設(shè)備連接,異步訪問地址空間最大可擴展為256 MB,接口模塊提供4個片選信號,每個片選信號可選中64 MB獨立存儲空間。該接口模塊具有可編程能力,通過設(shè)置模塊控制寄存器的不同參數(shù)可調(diào)節(jié)接口讀寫時序和傳輸數(shù)據(jù)寬度等傳輸特性,EMIF16模塊接口結(jié)構(gòu)如圖1所示[1]。

由圖1可見,EMIF16模塊框圖主要由一系列信號引腳組成,各接口管腳功能如下:EMIFD[15:0]表示EMIF模塊讀寫數(shù)據(jù)的16位數(shù)據(jù)總線;EMIFA[23:0]表示EMIF模塊訪問存儲空間的24位地址總線;EMIFCE[3:0]表示EMIF模塊片選信號,低電平有效,分別對應DSP的CE0~CE3片選區(qū)間;EMIFBE[1:0]表示EMIF模塊字節(jié)使能信號;EMIFWE表示EMIF模塊寫操作使能信號,低電平有效;EMIFOE表示EMIF模塊輸出使能信號,低電平有效;EMIFWAIT[1:0]表示EMIF模塊等待信號;EMIFRnW表示EMIF模塊的讀寫使能信號[2]。通過對上述的數(shù)據(jù)總線、地址總線及控制信號的編程設(shè)計實現(xiàn)EMIF16接口與外部存儲器的通信功能。

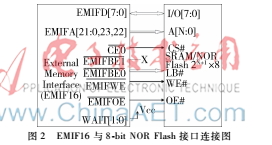

1.2EMIF16接口連接及異步讀寫時序

EMIF16模塊外接不同類型存儲芯片時信號管腳的接口設(shè)置也不相同,本系統(tǒng)設(shè)計的通信系統(tǒng)中多核DSP的EMIF16模塊接口直接與FPGA連接,由FPGA端設(shè)計多個FIFO空間供DSP進行讀寫,EMIF16模塊外接時序設(shè)計采用8-bit NOR Flash接口時序,具體接口框圖如圖2所示[3]。

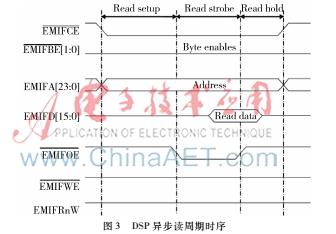

EMIF16接口的每個讀/寫周期分為三個階段:建立時間(Setup)、觸發(fā)時間(Strobe)和保持時間(Hold),每個階段的相應參數(shù)都可通過對EMIF16模塊控制寄存器編程進行設(shè)置,具體參數(shù)設(shè)置在接口驅(qū)動程序中實現(xiàn)。接口讀寫時序參數(shù)是EMIF接口設(shè)計中較為重要的參數(shù),DSP端與FPGA端接口時序必須保持一致才能實現(xiàn)數(shù)據(jù)穩(wěn)定傳輸,EMIF異步讀時序如圖3所示,EMIF異步寫時序如圖4所示。

圖3、圖4中Setup、Strobe、Hold等參數(shù)設(shè)置皆以EMIF16時鐘周期為基準,本系統(tǒng)設(shè)計中EMIF16模塊默認使用DSP系統(tǒng)輸出時鐘中的SysClk7時鐘信號,該時鐘頻率為芯片主頻的1/6分頻,本系統(tǒng)中使用的TMS320C6678多核DSP主頻配置為1 GHz,所以EMIF16接口時鐘頻率可達到166.67 MHz,能夠滿足高速串行通信需求[4]。

2DSP與FPGA通信系統(tǒng)設(shè)計

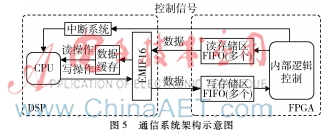

本文設(shè)計的DSP與FPGA通信接口基于圖2所示的異步 8bit NOR Flash接口連接圖要求進行硬件電路設(shè)計,同時,基于該硬件平臺設(shè)計一種通信應用系統(tǒng),實現(xiàn)DSP與FPGA之間數(shù)據(jù)的穩(wěn)定快速傳輸,本系統(tǒng)所設(shè)計的通信系統(tǒng)架構(gòu)如圖5所示。

圖5描述了一種基于EMIF16接口模塊的DSP與FPGA通信系統(tǒng)應用框圖。FPGA端提供多個8 bit寬的FIFO供DSP進行讀寫,DSP端除了使用EMIF模塊外,同時調(diào)用了CPU中斷系統(tǒng)資源配合消息傳輸。FPGA將消息寫入FIFO后發(fā)送相應控制信號觸發(fā)DSP中斷,DSP收到讀消息中斷后啟動EMIF接口讀取消息;DSP端發(fā)送消息時可直接將數(shù)據(jù)寫入EMIF模塊對應的寄存器,EMIF模塊在異步寫周期內(nèi)將數(shù)據(jù)寫入FPGA提供的存儲FIFO中。此框架中FPGA端的讀/寫存儲區(qū)分別提供多個FIFO進行通信,從而使該系統(tǒng)可進行多種類別或者多協(xié)議的消息通信,提高了系統(tǒng)應用的適應性;在DSP數(shù)據(jù)接收端使用了緩存機制設(shè)計,EMIF接口模塊接收的每一條消息首先存入緩存區(qū),然后再由CPU對緩存區(qū)消息逐條進行校驗和處理,這樣操作不僅提高了EMIF模塊接收消息的效率,而且將接收消息和處理消息兩個CPU主要線程進行了分離,防止消息在未處理時被覆蓋或者篡改,保證了緩沖區(qū)數(shù)據(jù)的完整性和正確性,從而提高信號處理的穩(wěn)定與可靠性。

3通信系統(tǒng)軟件設(shè)計與實現(xiàn)

3.1通信接口軟件設(shè)計

根據(jù)EMIF16模塊接口特性,系統(tǒng)可擴展訪問地址空間最大為256 MB, 存儲地址范圍為0x70000000~0x7FFFFFFF,平均分為4個CE地址空間,每個CE空間支持外接NAND、NOR及SRAM存儲器,每個CE空間都有單獨的異步配置寄存器(ACR)對其使用配置,EMIF16模塊寄存器地址空間為0x20C00000~0x20C00FF,共256 B,該地址空間內(nèi)包括EMIF16模塊的版本及狀態(tài)寄存器(RCSR)、異步等待周期寄存器 (AWCCR)、4個異步配置寄存器(ACR)及EMIF模塊中斷相關(guān)寄存器(IRR、IMR、IMSR、IMCR)等。要實現(xiàn)本系統(tǒng)所設(shè)計的通信接口功能,首先需對DSP的EMIF16模塊進行驅(qū)動初始化編程,即對上述相應寄存器進行編程配置,寄存器編程配置時可根據(jù)需要進行重點位域編碼,與系統(tǒng)功能實現(xiàn)無關(guān)的寄存器位域可選擇默認值配置。驅(qū)動配置完成后方可進行上層應用系統(tǒng)的設(shè)計及實現(xiàn),本系統(tǒng)所設(shè)計的基于EMIF16接口的DSP與FPGA異步通信系統(tǒng)軟件流程如圖6所示。

如圖6所示,基于EMIF的接口通信程序完成系統(tǒng)初始化后即可與外界進行通信,本文所設(shè)計的通信系統(tǒng)主要完成消息的接收與發(fā)送功能:接收端采用被動接收模式,需依靠系統(tǒng)告知EMIF模塊進行數(shù)據(jù)接收,本系統(tǒng)設(shè)計中使用中斷輔助實現(xiàn)數(shù)據(jù)接收功能,系統(tǒng)中使用GPIO9管腳上升沿信號作為中斷事件觸發(fā)CPU中斷,當FPGA端將數(shù)據(jù)準備好后即對GPIO9管腳進行拉高電平操作,DSP端收到GPIO9上升沿信號后觸發(fā)INT9,CPU收到中斷信號后執(zhí)行中斷服務函數(shù),在中斷服務函數(shù)中對消息接收控制寄存器(RCR)進行判斷并執(zhí)行相應消息接收操作;發(fā)送端采用主動發(fā)送模式,由CPU直接操作EMIF模塊進行數(shù)據(jù)發(fā)送,為了保證DSP與FPGA發(fā)送消息的穩(wěn)定性,每次DSP發(fā)送消息時需查詢FPGA端對應準備狀態(tài),當消息發(fā)送控制寄存器(TCR)對應狀態(tài)準備完成時才能進行消息發(fā)送。

3.2通信控制寄存器設(shè)計

消息接收控制寄存器(RCR)和發(fā)送控制寄存器(TCR)是通信系統(tǒng)中為保障系統(tǒng)穩(wěn)定執(zhí)行而設(shè)計的輔助寄存器,并非芯片內(nèi)部固有寄存器,輔助寄存器RCR和TCR由FPGA芯片設(shè)計提供,具體位域所表示的信息根據(jù)系統(tǒng)需求制定。DSP芯片端在進行讀寫操作時對指定地址進行訪問即可獲得寄存器當前有效信息,通過輔助寄存器的實時值分析可以判定系統(tǒng)當前通信過程中消息類型及系統(tǒng)工作狀態(tài)等信息,從而保證通信過程的可控性與穩(wěn)定性。

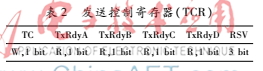

接收消息控制寄存器如表1所示,當某類消息已經(jīng)準備好接收時,其對應的標志位RxTypeX會被FPGA置1,反之則置0;發(fā)送端采用主動發(fā)送模式,由CPU直接操作EMIF模塊進行數(shù)據(jù)發(fā)送,為了保證DSP與FPGA發(fā)送消息的穩(wěn)定性,每次DSP發(fā)送消息時需查詢FPGA端對應準備狀態(tài),當發(fā)送控制寄存器(TCR)對應狀態(tài)準備完成時才能進行消息發(fā)送,發(fā)送控制寄存器如表2所示,當某類消息準備好發(fā)送時,其對應的標志位TxRdyX會被FPGA置1,反之則置0。

RC:接收消息總標志。

RxTypeA:1:消息類型為A;0:無該類型消息。

RxTypeB:1:消息類型為B;0:無該類型消息。

RxTypeC:1:消息類型為C;0:無該類型消息。

RxTypeD:1:消息類型為D;0:無該類型消息。

RSV:保留。

TC:發(fā)送消息準備狀態(tài)總標志。

TxRdyA:1:A類消息準備好;0:未準備好。

TxRdyB:1:B類消息準備好;0:未準備好。

TxRdyC:1:C類消息準備好;0:未準備好。

TxRdyD:1:D類消息準備好;0:未準備好。

RSV:保留。

3.3接口測試與驗證

針對上文所設(shè)計的接口和系統(tǒng)流程進行了測試與驗證,選取CE0空間地址設(shè)置多個8 bit寬的FIFO,其中FIFO0地址為0x71000000,用于接收DSP端發(fā)送來的數(shù)據(jù),數(shù)據(jù)流向為從DSP到FPGA,測試數(shù)據(jù)采用升序;FIFO1地址為0x71010000,用于向DSP端發(fā)送數(shù)據(jù),數(shù)據(jù)流向為從FPGA到DSP,測試數(shù)據(jù)采用降序。測試結(jié)果如圖7、圖8所示。

實驗結(jié)果表明,本文設(shè)計的DSP與FPGA之間的通信系統(tǒng)能夠按照設(shè)計要求工作,傳輸數(shù)據(jù)長度及地址可以根據(jù)需要進行多種配置,經(jīng)過多次測試,數(shù)據(jù)讀寫正確,接口工作穩(wěn)定,滿足系統(tǒng)設(shè)計需求。

4結(jié)束語

本系統(tǒng)實現(xiàn)了基于EMIF16模塊的DSP與FPGA異步通信接口,系統(tǒng)設(shè)計簡單、性能穩(wěn)定,實現(xiàn)了DSP與FPGA之間的雙向高速通信,擴展了多核DSP處理芯片與外圖界的通信方式。采用DSP與FPGA聯(lián)合設(shè)計的方式,可實現(xiàn)多種格式的高速數(shù)據(jù)傳輸,同時軟件架構(gòu)設(shè)計簡潔穩(wěn)定,有利于工程實現(xiàn)及應用。

參考文獻

[1] Texas Instruments. TMS320C6678 multicore fixed and floatingpoint digital signal processor[S].2014.

[2] 卞紅雨.TMS320C6000系列DSP的CPU與外設(shè)[M].北京:清華大學出版社,2007.

[3] Texas Instruments.External Memory Interface (EMIF16) for KeyStone devices user guide[S].2011.

[4] Texas Instruments.KeyStone architecture external memory interface (EMIF16) user guide[S].2011.