前言:

近年來摩爾定律增速不斷放緩,而新型應(yīng)用對(duì)高效節(jié)能芯片的要求越來越強(qiáng)烈,半導(dǎo)體業(yè)界正在積極探索解決方案,包括3D封裝等技術(shù)。

發(fā)展技術(shù)才是硬道理

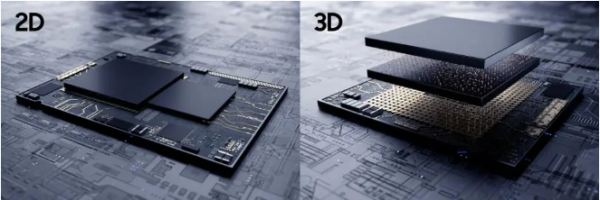

作為全球先進(jìn)芯片生產(chǎn)廠商,三星已經(jīng)在制程工藝上取得了很大的成功。近日,三星又對(duì)外宣布其全新的芯片封裝技術(shù)X-Cube,稱該技術(shù)可以使封裝完成的芯片擁有更強(qiáng)大的性能以及更高的能效比。目前現(xiàn)有的芯片都是2D平面堆疊的,隨著芯片數(shù)量的增多,占用的面積越來越大,不利于提高集成度。關(guān)于3D芯片封裝,就是將芯片從平面堆疊變成了垂直堆疊,類似搭積木那樣一層層疊加,減少了芯片面積,提高了集成度。

衡量一個(gè)芯片封裝技術(shù)先進(jìn)與否的重要指標(biāo)是:芯片面積與封裝面積之比,這個(gè)比值越接近1越好,封裝時(shí)主要考慮的因素:

①芯片面積與封裝面積之比,為提高封裝效率,盡量接近1:1。

②引腳要盡量短以減少延遲,引腳間的距離盡量遠(yuǎn),以保證互不干擾,提高性能。

③基于散熱的要求,封裝越薄越好。

先進(jìn)封裝技術(shù)受到熱捧

目前業(yè)界領(lǐng)頭羊都在3D封裝技術(shù)上面努力著,在三星推出X-Cube時(shí),全球主要的三家半導(dǎo)體代工廠均已經(jīng)擁有3D或2.5D的封裝技術(shù)了。前有臺(tái)積電的CoWoS,Intel的Foveros,現(xiàn)在三星也公布了自家的3D封裝技術(shù)X-Cube。顯而易見的是,未來我們買到的電子產(chǎn)品中,使用3D封裝技術(shù)的芯片比例會(huì)越來越高。

臺(tái)積電的CoWoS封裝是一項(xiàng)2.5D封裝技術(shù),它可以把多個(gè)小芯片封裝到一個(gè)基板上,這項(xiàng)技術(shù)有許多優(yōu)點(diǎn),但主要優(yōu)勢(shì)是節(jié)約空間、增強(qiáng)芯片之間的互聯(lián)性和功耗降低,AMD的Fury和Vega系列顯卡就是使用這一技術(shù)把GPU和HBM顯存封裝在一起的,NVIDIA的高端Tesla計(jì)算卡也是用這種封裝。

英特爾Foveros3D堆疊封裝技術(shù),可以通過在水平布置的芯片之上垂直安置更多面積更小、功能更簡(jiǎn)單的小芯片來讓方案整體具備更完整的功能。官方表示,除了功能性的提升之外,F(xiàn)overos技術(shù)對(duì)于產(chǎn)業(yè)來說最吸引的地方在于他可以將過去漫長(zhǎng)的重新設(shè)計(jì)、測(cè)試、流片過程統(tǒng)統(tǒng)省去,直接將不同IP、不同工藝的各種成熟方案封裝在一起,從而大幅降低成本并提升產(chǎn)品上市速度。

X-Cube 3D可大規(guī)模投產(chǎn)

而三星的X-Cube意為拓展的立方體。不同于以往多個(gè)芯片平行封裝,全新的X-Cube3D封裝允許多枚芯片堆疊封裝,使得成品芯片結(jié)構(gòu)更加緊湊。而芯片之間的通信連接采用了TSV技術(shù),而不是傳統(tǒng)的導(dǎo)線。

據(jù)三星介紹,目前該技術(shù)已經(jīng)可以將SRAM存儲(chǔ)芯片堆疊到主芯片上方,以騰出更多的空間用于堆疊其他組件,目前該技術(shù)已經(jīng)可以用于7nm甚至5nm制程工藝的產(chǎn)品線,也就是說離大規(guī)模投產(chǎn)已經(jīng)十分接近。

三星封裝將發(fā)展更多領(lǐng)域

三星表示,TSV技術(shù)可以大幅減少芯片之間的信號(hào)路徑,降低功耗的同時(shí)提高了傳輸?shù)乃俾省T摷夹g(shù)將會(huì)應(yīng)用于最前沿的5G、AI、AR、HPC、移動(dòng)芯片已經(jīng)VR領(lǐng)域,這些領(lǐng)域也都是最需要先進(jìn)封裝工藝的地方。

至于芯片發(fā)展的路線,三星與各大芯片廠商保持一致,將會(huì)跳過4nm的制程工藝,直接選用3nm作為下一代產(chǎn)品的研發(fā)目標(biāo)。目前三星計(jì)劃和無晶圓廠的芯片設(shè)計(jì)公司繼續(xù)合作,推進(jìn)3D封裝工藝在下一代高性能應(yīng)用中的部署。

結(jié)尾:

無論從哪個(gè)層面來看,封裝技術(shù)在很大程度上都能夠成為推動(dòng)摩爾定律繼續(xù)向前發(fā)展的第二只輪子。這也讓整個(gè)半導(dǎo)體行業(yè)開辟了全新的發(fā)展路徑和空間。