6月11日,東芝電子器件與存儲(chǔ)株式會(huì)社(東芝)和日本半導(dǎo)體株式會(huì)社(日本半導(dǎo)體)共同展示了一種改進(jìn)方法,可提高高壓橫向雙擴(kuò)散MOS (Laterally Double Diffused MOS,LDMOS)的可靠性和性能。其中,LDMOS是在電機(jī)控制驅(qū)動(dòng)程序等大量汽車(chē)應(yīng)用中使用的模擬IC的核心組件。隨著車(chē)輛電氣化的不斷發(fā)展,包括更廣泛地部署高級(jí)駕駛輔助系統(tǒng)(ADAS),東芝和日本半導(dǎo)體將能夠根據(jù)所需電壓提供改進(jìn)的LDMOS單元設(shè)計(jì)。

(圖片來(lái)源:東芝)

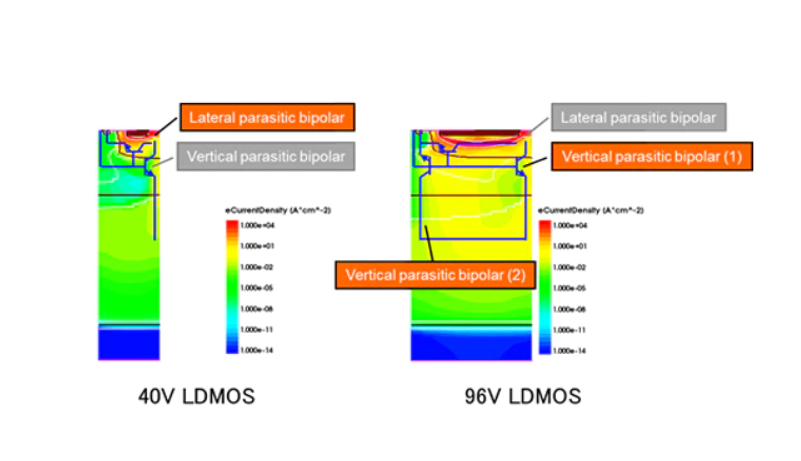

眾所周知,設(shè)計(jì)LDMOS時(shí)經(jīng)常需要在可靠性和性能間進(jìn)行取舍。橫向寄生雙極效應(yīng)通常會(huì)降低人體模型(HBM)容差。而通過(guò)增加背柵比(backgate ratio)抑制橫向寄生雙極效應(yīng),HBM測(cè)量的靜電放電(ESD)的容差會(huì)得到改善。然而,增加背柵比也會(huì)增加導(dǎo)通電阻,從而降低性能。截至目前,LDMOS設(shè)計(jì)人員仍然必須在HBM容差與更高的導(dǎo)通電阻之間取得平衡。

東芝和日本半導(dǎo)體對(duì)LDMOS中的HBM容差進(jìn)行了評(píng)估,發(fā)現(xiàn)即使背柵比增加,在80V以上時(shí)容差也沒(méi)有增加。他們發(fā)現(xiàn)這是因?yàn)樵?D TCAD模擬中,垂直寄生雙極效應(yīng)與橫向寄生雙極效應(yīng)一起出現(xiàn),使設(shè)計(jì)人員在設(shè)置HBM和背柵比參數(shù)時(shí)具有更大的自由度。

東芝公司開(kāi)發(fā)出一種技術(shù),可優(yōu)化除了背柵比(背柵的總寬度與源和背柵的總寬度之比)之外的單元設(shè)計(jì)參數(shù)。而將該技術(shù)與此次的發(fā)現(xiàn)相結(jié)合,東芝和日本半導(dǎo)體提出一種改善HBM容差并抑制80V及更高LDMOS導(dǎo)通電阻的方法,從而使得LDMOS可具有HBM容差,且不依賴背柵比。該方法可應(yīng)用于發(fā)動(dòng)機(jī)、轉(zhuǎn)向系統(tǒng)等其他汽車(chē)系統(tǒng)中,將有助于提高可靠性和功率效率。

東芝擁有適用于各種應(yīng)用、各種電壓的LDMOS廣泛產(chǎn)品陣容,并且正在開(kāi)發(fā)可集成嵌入式非易失性存儲(chǔ)器(eNVM)和高壓模擬IC的第五代工藝技術(shù)。東芝和日本半導(dǎo)體致力于半導(dǎo)體工藝研發(fā),為低功耗和高可靠性做出貢獻(xiàn)。

來(lái)源:蓋世汽車(chē)

作者:劉麗婷