1nm制程可能不再遙遠(yuǎn)。

作者 | 來(lái)自鎂客星球的家衡

將芯片越做越薄,一直都是科學(xué)家們的夢(mèng)想。

但我們都知道,現(xiàn)有的硅晶體已經(jīng)越來(lái)越接近物理極限。

想要從“納米級(jí)”突破到“原子級(jí)”,只能靠二硫化鉬等超薄半導(dǎo)體材料來(lái)幫忙。

近日,來(lái)自瑞士巴塞爾大學(xué)的研究人員宣布,他們成功在二硫化鉬材料上加入了超導(dǎo)體觸點(diǎn),從而展示與硅晶體類(lèi)似的特性。

這次實(shí)驗(yàn)的成功,驗(yàn)證了超薄半導(dǎo)體材料制造半導(dǎo)體元器件的可行性。

實(shí)驗(yàn)展示超薄半導(dǎo)體材料的新特性

本次實(shí)驗(yàn)由Andreas Baumgartner博士領(lǐng)導(dǎo),其領(lǐng)導(dǎo)的研究小組計(jì)劃將一些具有半導(dǎo)體性質(zhì)的天然材料層疊形成三維晶體,再與超導(dǎo)體結(jié)合起來(lái),繼而探究新材料的特性。

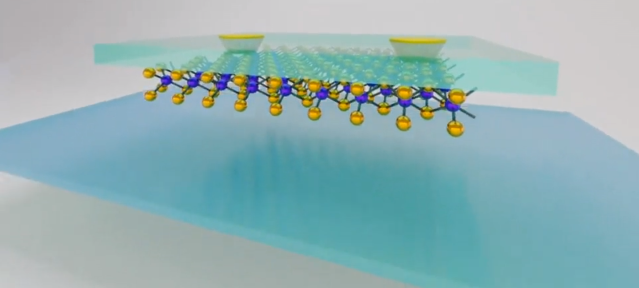

在實(shí)驗(yàn)開(kāi)始,研究人員先將二硫化鉬分離成單獨(dú)的層,這些單層的厚度不超過(guò)一個(gè)分子。

接著,研究人員像“制作三明治”一樣在單層的二硫化鉬兩側(cè)加入兩層薄薄的氮化硼。在手套箱中的保護(hù)性氮?dú)獗Wo(hù)下,研究人員將氮化硼層堆疊在二硫化鉬層上,并將底部與另一層氮化硼以及一層石墨烯結(jié)合。

然后,研究人員將這種復(fù)雜的范德華異質(zhì)結(jié)構(gòu)(一種特殊的三維結(jié)構(gòu))放置在硅/二氧化硅晶片的頂部。

這樣就堆疊出一個(gè)類(lèi)似于半導(dǎo)體元件的全新合成材料。

在堆疊完成后,研究人員開(kāi)始在絕對(duì)零度以上(-273.15攝氏度)的低溫下進(jìn)行實(shí)現(xiàn)觀察。

最后他們發(fā)現(xiàn),在超低溫的條件下,超導(dǎo)電測(cè)量清楚地顯示了超導(dǎo)引起的效應(yīng);例如,單電子不再被允許通過(guò)。此外,研究人員還發(fā)現(xiàn)了半導(dǎo)體層和超導(dǎo)體之間存在強(qiáng)耦合的跡象。這些特性與目前半導(dǎo)體芯片的物理特性十分相似。

研究項(xiàng)目經(jīng)理鮑姆加特納解釋說(shuō):“在超導(dǎo)體中,電子將自己排列成成對(duì),就像舞伴一樣,產(chǎn)生了奇怪而奇妙的結(jié)果,比如電流的流動(dòng)沒(méi)有電阻。另一方面,在半導(dǎo)體二硫化鉬中,電子表演一種完全不同的舞蹈,一種奇怪的獨(dú)舞,也包含了它們的磁矩。現(xiàn)在,如果我們把這些材料結(jié)合起來(lái),我們想親自看到這奇異的舞蹈。”

簡(jiǎn)單來(lái)說(shuō),本次實(shí)驗(yàn)驗(yàn)證了超薄半導(dǎo)體材料代替硅晶體的可行性,為下一代半導(dǎo)體制造器件提供了新的思路。

二維材料為“摩爾定律”續(xù)命

如今的芯片制程工藝,已經(jīng)完成了5nm的突破,科學(xué)家們發(fā)力向1nm的極限沖刺,今年5月6日,IBM率先宣布造出2nm芯片,頓時(shí)讓整個(gè)半導(dǎo)體圈子歡欣鼓舞。

但由于摩爾定律的存在,即使單位面積容納的晶體管數(shù)量逐步提前,但是效能無(wú)法得到顯著提升,在硅晶片的物理特性即將達(dá)到極限的背景下,1nm工藝像一座大山擋在硅技術(shù)面前。

此外,在目前的先進(jìn)制程里,都需要絕緣體的存在,他們存在的意義是要協(xié)助電子能順利通過(guò)晶體管里的通道,當(dāng)制程持續(xù)向下走,通道勢(shì)必越來(lái)越小,晶體管之間的串?dāng)_會(huì)很大,芯片的效能表現(xiàn)也會(huì)大打折扣。

例如一顆5nm工藝材料的芯片里,已經(jīng)塞下太多的晶體管,一旦電子黏在芯片內(nèi)部的氧化物絕緣體上,就會(huì)導(dǎo)致電流不易通過(guò),最終引起功耗增加、芯片發(fā)熱等問(wèn)題。

這也是為什么我們會(huì)吐槽臺(tái)積電和三星5nm工藝紛紛“翻車(chē)”,因?yàn)檫@真的太考慮后期的打磨。

既然三維的材料會(huì)讓電荷依附在上面,那么用二維材料作為替代品,可以完美避免電流通過(guò)的問(wèn)題。

目前,業(yè)內(nèi)普遍采用二硫化鉬作為二維超薄單層材料,這也是被認(rèn)為是突破硅晶片小型化限制的最有力替代品。

臺(tái)積電押注鉍(Bi)材料

事實(shí)上,除了此次瑞士巴塞爾大學(xué)的研究以外,學(xué)術(shù)界早已在二維材料連接上有所突破。

早前,麻省理工學(xué)院(MIT)的孔靜教授領(lǐng)導(dǎo)的國(guó)際聯(lián)合攻關(guān)團(tuán)隊(duì)宣布與臺(tái)大、臺(tái)積電共同完成合作,使用原子級(jí)薄材料鉍(Bi)代替硅,有效地將這些2D材料連接到其他芯片元件上。

當(dāng)鉍(Bi)材料被作為二維材料的接觸電極時(shí),可以大幅度降低電阻并且提升電流。

正如前文所說(shuō),金屬和半導(dǎo)體材料之間的界面會(huì)產(chǎn)生了一種叫做金屬誘導(dǎo)的間隙(MIGS)狀態(tài)現(xiàn)象,抑制電荷載體的流動(dòng)。而屬于半金屬的鉍(Bi)材料,電子特性介于金屬和半導(dǎo)體之間,可以有效消除了電荷流通的問(wèn)題。

目前,臺(tái)積電技術(shù)研究部門(mén)已經(jīng)開(kāi)始“鉍(Bi)沉積制程”技術(shù)的研究,這項(xiàng)研究已經(jīng)成為未來(lái)1nm工藝的突破所在。

通過(guò)這項(xiàng)技術(shù),研究人員可以設(shè)計(jì)出具有非凡性能的微型化晶體管,可以有效滿足了未來(lái)晶體管和芯片技術(shù)路線圖的要求。

1nm正慢慢成為現(xiàn)實(shí)

超薄半導(dǎo)體材料的成功驗(yàn)證,給我們展現(xiàn)出下一代半導(dǎo)體的無(wú)限潛力,未來(lái)的計(jì)算機(jī)或者會(huì)隨著超薄半導(dǎo)體材料的成熟展現(xiàn)出全新的姿態(tài)。

同時(shí)我們也要看到,臺(tái)積電、IBM都在積極搶占1nm先進(jìn)制程工藝。

關(guān)于下一

代半導(dǎo)體的競(jìng)爭(zhēng)已經(jīng)悄然開(kāi)始。