代工之爭拓展到封裝技術(shù)

臺積電和三星之間的代工之爭,正從先進(jìn)制造工藝擴(kuò)展到封裝技術(shù)。

近年來,代工業(yè)務(wù)從簡單的基于設(shè)計的芯片制造發(fā)展到提供代工前、后流程,如電子設(shè)計自動化、知識產(chǎn)權(quán)、設(shè)計和封裝。

封裝技術(shù)是三星和臺積電將在相當(dāng)長一段時間內(nèi)展開激烈競爭的領(lǐng)域。

現(xiàn)在看來,三星和臺積電都試圖抓住眼前千載難逢的機(jī)遇。三星在2017年開始支出激增的同時,臺積電將在2021年開始大規(guī)模的多年支出增長。

據(jù)IC Insights預(yù)計,三星和臺積電今年的資本支出將至少達(dá)到555億美元,占全球總支出的5%。

先進(jìn)制程工藝對封裝提出了更高要求,或者說,先進(jìn)封裝在一定程度上可以彌補(bǔ)制程工藝的不足。

臺積電2021年3月在日本成立了子公司「TSMC日本3D IC研究開發(fā)中心」。經(jīng)產(chǎn)省5月31日更宣布,臺積電將在茨城縣筑波市產(chǎn)業(yè)技術(shù)綜合研究所的無塵室,興建研究用生產(chǎn)線。2021年夏季開始整建,2022年正式投入研發(fā)。

三星韓國華城晶圓廠V1的不良率過高,仍需克服良率問題。該廠是目前三星最先進(jìn)的晶圓廠,于2020年2月啟動生產(chǎn),是全球首座將EUV設(shè)備導(dǎo)入7nm制程的產(chǎn)線。

不過,該廠自量產(chǎn)以來,先進(jìn)制程的良率提升速度遲緩,部分5nm芯片的良率甚至不到50%。

業(yè)界認(rèn)為,三星的晶圓代工業(yè)務(wù)有先天弱點,即旗下設(shè)有負(fù)責(zé)手機(jī)AP設(shè)計的系統(tǒng)LSI部門,為避免技術(shù)外流,高通和英偉達(dá)等客戶較傾向委托臺積電代工。

7nm及更先進(jìn)制程量產(chǎn)情況

7nm制程方面,在2020年,三星每月的產(chǎn)能約為2.5萬片晶圓,而臺積電每月約為14萬片;

而在5nm方面,雙方的差距更大,三星每月約為5000片晶圓,而臺積電每月約為9萬片。

由此看來,在先進(jìn)制程產(chǎn)能方面,臺積電明顯領(lǐng)先于三星。

而在制程工藝方面,三星一直在追趕臺積電,特別是在5nm方面,三星的低功耗版本5LPE性能比7nm的提升了10%,而在相同的時鐘和復(fù)雜度下,功耗可降低20%。

另外,三星已完成第二代5nm和第一代4nm產(chǎn)品的設(shè)計。

臺積電5nm系列在2021年的產(chǎn)能擴(kuò)充計劃比2020年會翻倍,2022年比2020年增長3.5倍以上,并在2023年達(dá)到2020年的4倍以上。

4nm方面,臺積電與5nm設(shè)計法則幾近兼容的4nm加強(qiáng)版減少了光罩層,進(jìn)一步提升了效能、功耗效率、以及晶體管密度,預(yù)計于2021年第3季度開始試產(chǎn)。

3nm方面,臺積電將于下半年試產(chǎn),預(yù)計2022年實現(xiàn)量產(chǎn);而三星于近期成功流片,但量產(chǎn)時間恐怕要晚于臺積電。

聚焦先進(jìn)封裝的必要性

無論是臺積電,還是三星甚至英特爾,都把先進(jìn)封裝當(dāng)做公司的一大工作重點,這主要是在日益增長的性能需求與摩爾定律的逐漸失效的矛盾影響下所演進(jìn)出來的折中結(jié)果。

但是,這些方法仍然是非常特定于客戶的,并且會花費大量的開發(fā)時間和成本。

折中通過在封裝中組裝不同且先進(jìn)的芯片是推進(jìn)芯片設(shè)計的方法之一,但由于成本的原因,高級封裝主要用于高端,面向利基市場的應(yīng)用。

但是隨著芯片開發(fā)步伐的放慢,縮小晶體管之間的空間并在芯片上放置更多晶體管的難度變得越來越大,為此新的封裝方式走向臺前。

臺積電與三星在封裝技術(shù)領(lǐng)域展開競爭

臺積電近幾年所推出「CoWoS」IC晶片封裝架構(gòu),以及「整合扇出型」封裝制程等,原本就是為了透過IC芯片的堆疊工藝、封裝制程。

在蘋果秋季發(fā)布會上,由臺積電最先進(jìn)5nm納米制程所代工打造的蘋果A14 Bionic處理器已先亮相,預(yù)計將搭載在蘋果的新款iPhone手機(jī)與新一代iPad Air平板電腦上。

臺積電推出了3D Fabric系統(tǒng)整合方案,其針對高效能運算應(yīng)用,將于2021年提供更大的光罩尺寸,以支持整合型扇出封裝(InFO),以及CoWoSR封裝方案,運用范圍更大的布局布線來整合小芯片及高帶寬內(nèi)存。

此外,芯片堆棧于晶圓之上(CoW)的版本預(yù)計今年完成7nm的驗證,并于2022年在新的全自動化晶圓廠開始生產(chǎn)。

針對移動應(yīng)用,臺積電推出了InFO_B,將移動處理器整合于輕薄精巧的封裝中,提供強(qiáng)化的效能與功耗效率,并支持移動應(yīng)用器件封裝時所需的動態(tài)隨機(jī)存取內(nèi)存堆棧。

特殊制程方面,臺積電推出N12e技術(shù),擁有更低功耗,保有高效能運算能力,將推廣應(yīng)用于新世代物聯(lián)網(wǎng)領(lǐng)域。

日前,韓國供應(yīng)鏈就指出,三星自上個月開始已經(jīng)部署3D芯片封裝技術(shù),目的便是尋求在2022年跟臺積電在芯片先進(jìn)封裝領(lǐng)域展開競爭。

三星的3D芯片先進(jìn)封裝技術(shù)訂名為「eXtended-Cube」,簡稱「X-Cube」,在8 月中旬已經(jīng)進(jìn)行展示,在當(dāng)中將采用7納米制程技術(shù),來為客戶提供相關(guān)的產(chǎn)品。

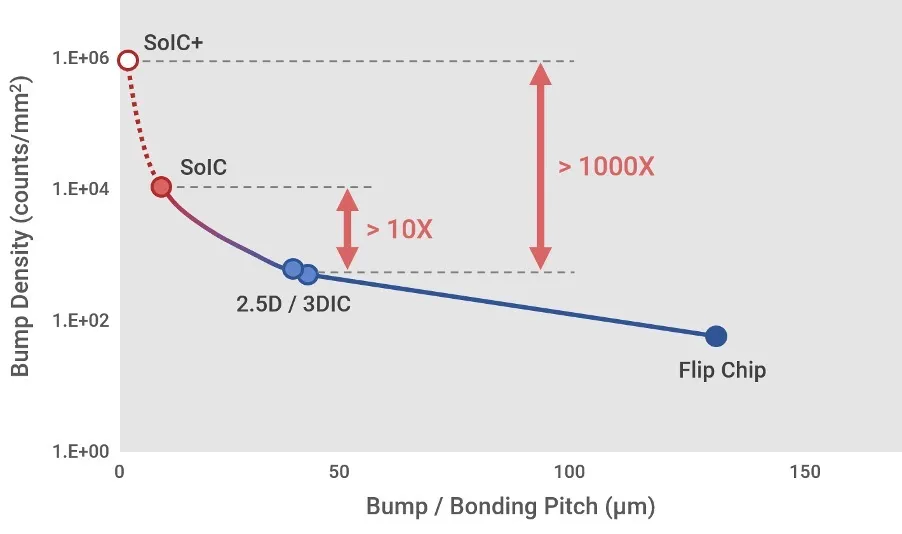

三星在7nm制程的測試過程中,利用TSV 技術(shù)將SRAM 堆疊在邏輯芯片頂部,這也使得在電路板的配置上,可在更小的面積上裝載更多的存儲單元。

X-Cube還有諸多優(yōu)點,如芯片間的信號傳遞距離更短,以及將數(shù)據(jù)傳送、能量效率提升到最高。

龐大的市場發(fā)展規(guī)模成大廠大力推進(jìn)的原因

根據(jù)Yole最新預(yù)測,從2018-2024年,整個半導(dǎo)體封裝市場的營收將以5%的復(fù)合年增長率增長,而先進(jìn)封裝市場將以8.2%的復(fù)合年增長率增長,市場規(guī)模到2024年將增長至436億美元。

在各種先進(jìn)封裝平臺中,3D硅通孔(TSV)和扇出型(Fan-out)封裝,將分別以29%和15%的速度增長。

而占據(jù)先進(jìn)封裝市場主要市場份額的倒裝芯片(Flip-chip)封裝,將以約7%的復(fù)合年增長率增長。

與此同時,扇入型晶圓級封裝(Fan-in WLP)主要受到移動市場驅(qū)動,也將以7%的復(fù)合年增長率增長。

結(jié)尾

由于目前尚無其他公司能夠與這一龐大的支出相匹敵,因此三星和臺積電今年可能會在先進(jìn)集成電路制造技術(shù)方面與競爭對手之間拉開更大的差距。

先進(jìn)封裝技術(shù)已成為了競爭焦點,臺積電、英特爾都在不斷豐富自己的先進(jìn)封裝技術(shù),引領(lǐng)先進(jìn)封裝技術(shù)發(fā)展,未來封裝技術(shù)與前道技術(shù)將相互融合。