EDA進(jìn)入AI設(shè)計(jì)新紀(jì)元:新思科技、Cadence、谷歌和英偉達(dá)開(kāi)始借助AI進(jìn)行復(fù)雜芯片設(shè)計(jì)

2021-10-09

來(lái)源: 電子工程專輯

現(xiàn)今先進(jìn)的芯片設(shè)計(jì)可能需要數(shù)百名設(shè)計(jì)工程師,配備最先進(jìn)的 EDA 設(shè)計(jì)工具,耗費(fèi)2-4年時(shí)間才能完成。EDA開(kāi)發(fā)廠商和先進(jìn)AI芯片設(shè)計(jì)企業(yè)開(kāi)始考慮,讓AI來(lái)輔助芯片設(shè)計(jì)是否可以加快設(shè)計(jì)流程,減少人工和時(shí)間等資源的投入?答案是肯定的,如果硬件開(kāi)發(fā)變得更加敏捷和自主,那么昂貴且漫長(zhǎng)的芯片設(shè)計(jì)流程可能會(huì)從 2-3 年縮短到 2-3個(gè)月。在新一代EDA設(shè)計(jì)工具中,AI扮演著至關(guān)重要的角色。新思科技和Cadence等EDA廠商,以及谷歌和英偉達(dá)等AI芯片設(shè)計(jì)公司已經(jīng)開(kāi)始借助AI進(jìn)行復(fù)雜的芯片設(shè)計(jì),而且取得了驚人的效果。

芯片設(shè)計(jì)AI化

去年,新思科技發(fā)布DSO.ai(Design Space Optimization AI)軟件,可以讓IC設(shè)計(jì)工程師更自主地確定在芯片上排列布局的最佳方式以減少面積和降低功耗,由此開(kāi)始了EDA設(shè)計(jì)的人工智能化進(jìn)程。利用強(qiáng)化學(xué)習(xí)(reinforcement learning),DSO.ai 可以根據(jù)設(shè)計(jì)目標(biāo)來(lái)評(píng)估數(shù)十億個(gè)替代方案,并快速產(chǎn)生明顯優(yōu)于優(yōu)秀工程師的設(shè)計(jì)方案。DSO.ai能夠解決的問(wèn)題/方案的潛力是巨大的:在芯片上排放各種組件的可能方案數(shù)量大約有10的9萬(wàn)次方個(gè)(1090,000)。相比之下,谷歌AI在2016 年掌握的圍棋走法只有10的360次方個(gè)(10360 )。既然利用強(qiáng)化學(xué)習(xí)的AI下棋可以比世界冠軍更好,如果愿意花計(jì)算時(shí)間去做,AI應(yīng)該可以設(shè)計(jì)出比天才工程師更好的芯片來(lái)。DSO.ai的試驗(yàn)結(jié)果令人印象深刻,實(shí)現(xiàn)了18% 的工作頻率提高,而且功耗降低了 21%,同時(shí)將工程時(shí)間從六個(gè)月縮短到一個(gè)月。

最近谷歌和英偉達(dá)也發(fā)布了類似的結(jié)果。另一家EDA開(kāi)發(fā)廠商Cadence也發(fā)布了Cerebrus智能芯片探索器工具,這是一個(gè)類似于新思DSO.ai 的AI優(yōu)化設(shè)計(jì)平臺(tái)。在探討這些最新AI設(shè)計(jì)趨勢(shì)之前,讓我們先看一下半導(dǎo)體設(shè)計(jì)空間的變化。

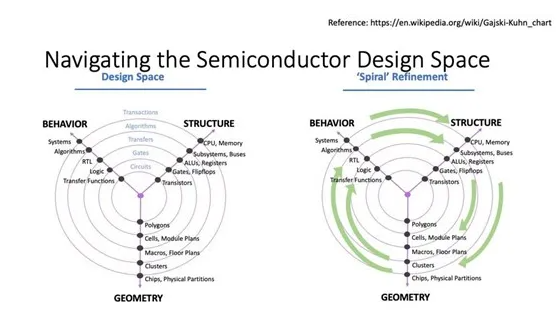

Gajski-Kuhn圖是一個(gè)很好的起點(diǎn),它描繪了芯片設(shè)計(jì)沿三個(gè)軸進(jìn)行的所有步驟:

第一個(gè)軸是行為級(jí)別(Behavioral),在此軸上架構(gòu)師定義芯片要做什么,具體包括轉(zhuǎn)移功能、邏輯、RTL、算法和系統(tǒng)。

第二個(gè)軸是結(jié)構(gòu)級(jí)別(Structural),在此軸上架構(gòu)師確定芯片如何進(jìn)行組織安排,包括晶體管、門陣列和反轉(zhuǎn)觸發(fā)器、ALU和寄存器、子系統(tǒng)和總線、CP和存儲(chǔ)器。

第三個(gè)軸是幾何級(jí)別(Geometry),在此軸上工程師定義芯片如何布局,包括多邊形、單元和模塊規(guī)劃、宏和平面規(guī)劃、集群、芯片和物理分割。

所有芯片設(shè)計(jì)團(tuán)隊(duì)都圍繞這三個(gè)軸上的規(guī)范和步驟工作,每一步都是向著中心目標(biāo)(即交付給晶圓代工廠進(jìn)行流片),按順時(shí)針?lè)较蛲七M(jìn)下一階段的工作。迄今為止,AI的所有應(yīng)用都是在幾何空間或物理設(shè)計(jì)軸上,以解決摩爾定律的延緩問(wèn)題。

新思的DSO.ai是第一個(gè)將AI應(yīng)用到物理設(shè)計(jì)過(guò)程的嘗試者,它生成的平面規(guī)劃圖功耗更低,運(yùn)行頻率更高,并且占用的空間比經(jīng)驗(yàn)豐富的設(shè)計(jì)所能規(guī)劃的最佳空間還要小。AI對(duì)生產(chǎn)力的深遠(yuǎn)影響值得關(guān)注,DSO.ai用戶能夠在幾天內(nèi)實(shí)現(xiàn)過(guò)去需要專家團(tuán)隊(duì)花費(fèi)數(shù)周才能完成的工作。

谷歌和英偉達(dá)的研究團(tuán)隊(duì)都發(fā)表了利用強(qiáng)化學(xué)習(xí)進(jìn)行物理設(shè)計(jì)的研究論文。谷歌利用AI對(duì)其下一代 TPU芯片設(shè)計(jì)進(jìn)行平面布局規(guī)劃,而且正在研究AI在架構(gòu)優(yōu)化方面的作用。英偉達(dá)同樣專注于容易實(shí)現(xiàn)的成果:布局規(guī)劃。他們將會(huì)利用其內(nèi)部擁有的所有GPU計(jì)算能力,并使用人工智能來(lái)設(shè)計(jì)更好的AI芯片。

Cerebrus智能芯片探索器

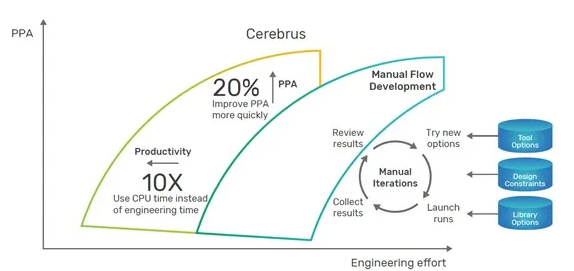

Cadence 最近推出了名為 Cerebrus 的“智能芯片探索器”,通過(guò)強(qiáng)化學(xué)習(xí)來(lái)優(yōu)化物理設(shè)計(jì)流程。Cerebrus在功能上與新思的DSO.ai 類似,專注于物理設(shè)計(jì)。雖然谷歌和英偉達(dá)可能有足夠的資源和知識(shí)來(lái)開(kāi)發(fā)自己的 AI 以進(jìn)行芯片設(shè)計(jì)優(yōu)化,但他們可能只是為自己所用,而大多數(shù)芯片設(shè)計(jì)公司和項(xiàng)目仍會(huì)選擇來(lái)自EDA 供應(yīng)商的工具。Cadence Cerebrus的發(fā)布似乎進(jìn)一步驗(yàn)證了強(qiáng)化學(xué)習(xí)技術(shù)作為芯片設(shè)計(jì)方法論的下一個(gè)重大轉(zhuǎn)變。我們相信,隨著設(shè)計(jì)師越來(lái)越習(xí)慣讓機(jī)器決定布局,以及競(jìng)爭(zhēng)壓力的增加,AI將逐漸滲透到IC設(shè)計(jì)流程的各個(gè)部分。

圖片提高生產(chǎn)力一直是芯片設(shè)計(jì)歷史演進(jìn)中的主旋律。在芯片設(shè)計(jì)的初級(jí)階段,每個(gè)晶體管都要單獨(dú)創(chuàng)建,并在完全自定義的布局編輯器中手動(dòng)連接,這是一個(gè)非常耗時(shí)的過(guò)程。為了提高效率,數(shù)字芯片設(shè)計(jì)開(kāi)始采用標(biāo)準(zhǔn)單元和原理圖網(wǎng)表方法,這使得工程師實(shí)現(xiàn)數(shù)字邏輯

設(shè)計(jì)的速度更快,但手動(dòng)創(chuàng)建原理圖網(wǎng)表需要花費(fèi)大量精力。當(dāng)桌面Unix工作站出現(xiàn)后,每個(gè)工程師都開(kāi)始擁有更大的計(jì)算能力,因此RTL綜合變得流行起來(lái)。芯片設(shè)計(jì)人員可以使用 VHDL 和 Verilog 等高級(jí)語(yǔ)言捕獲數(shù)字邏輯功能,并輕松合成包括數(shù)百萬(wàn)門的網(wǎng)表。然而,生產(chǎn)力的巨大飛躍帶來(lái)了另一個(gè)問(wèn)題,即如何布局?jǐn)?shù)百萬(wàn)的標(biāo)準(zhǔn)單元? 因此,繼RTL 綜合之后,自動(dòng)布局布線系統(tǒng)被開(kāi)發(fā)出來(lái)。現(xiàn)在大型網(wǎng)表也可以迅速實(shí)施,EDA又一次顯著提高了生產(chǎn)力。

Cadence的Cerebrus建立在大規(guī)模計(jì)算和機(jī)器學(xué)習(xí)架構(gòu)之上,并充分利用了完整的 Cadence數(shù)字全流程解決方案。Cerebrus借助獨(dú)特的強(qiáng)化機(jī)器學(xué)習(xí)引擎來(lái)提供更好的設(shè)計(jì) PPA 結(jié)果(性能、功耗和面積)。通過(guò)使用完全自動(dòng)化、機(jī)器學(xué)習(xí)驅(qū)動(dòng)的 RTL-to-GDS 全流程優(yōu)化技術(shù),Cerebrus 可以比手動(dòng)調(diào)整的流程更快地交付這些更好的 PPA 結(jié)果,從而極大提高工程設(shè)計(jì)團(tuán)隊(duì)的生產(chǎn)力。

Cerebrus 使用可擴(kuò)展分布式計(jì)算技術(shù)資源,無(wú)論是本地還是云端,都可以加速?gòu)?fù)雜SoC設(shè)計(jì)的流程。

結(jié)語(yǔ)

無(wú)論是AI芯片設(shè)計(jì)企業(yè)(NVIDIA 和 Google),還是EDA工具開(kāi)發(fā)商(新思科技和Cadence),都在嘗試以AI為主導(dǎo)的芯片設(shè)計(jì)優(yōu)化,以改善性能、成本和能耗。毫無(wú)疑問(wèn),NVIDIA 和谷歌正在集中精力設(shè)計(jì)開(kāi)發(fā)更好的GPU和Cloud TPU,以提高他們各自的市場(chǎng)競(jìng)爭(zhēng)優(yōu)勢(shì)。但是,AI 優(yōu)化只是他們用來(lái)幫助改進(jìn)自己產(chǎn)品和服務(wù)的工具。

全球EDA的領(lǐng)導(dǎo)者已經(jīng)開(kāi)啟AI設(shè)計(jì)的新紀(jì)元,新思的DSO.ai和Cadence的Cerebrus平臺(tái)將率先在物理設(shè)計(jì)中發(fā)揮超越人類工程師的AI優(yōu)勢(shì),加速當(dāng)今最復(fù)雜芯片的設(shè)計(jì)流程。

在即將于10月12號(hào)舉行的Cadence Live中國(guó)區(qū)線上用戶大會(huì)上,Cadence公司CEO陳立武、Cadence總裁Anirudh Devgan 博士、芯原公司董事長(zhǎng)/總裁兼CEO戴偉民博士將為觀眾帶來(lái)復(fù)雜芯片設(shè)計(jì)和最新EDA技術(shù)趨勢(shì)的主題演講,感興趣的朋友請(qǐng)即報(bào)名參會(huì)。