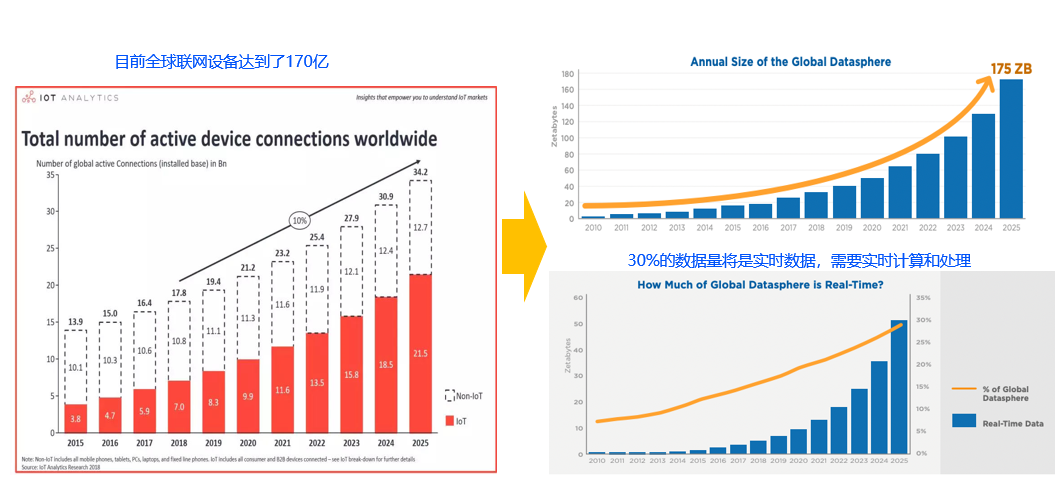

近年來隨著5G,人工智能等新興產(chǎn)業(yè)的發(fā)展,全球聯(lián)網(wǎng)設(shè)備數(shù)高速增長。據(jù)IDC和Statista數(shù)據(jù)顯示,2021年全球聯(lián)網(wǎng)設(shè)備已達(dá)到170億,大量設(shè)備的聯(lián)網(wǎng)帶來了數(shù)據(jù)量的爆發(fā),預(yù)計到2025年全球數(shù)據(jù)量將高達(dá)175ZB(1ZB約等于1萬億GB),其中30%的數(shù)據(jù)需要實時的計算和處理,所以我們正面臨數(shù)據(jù)增長給處理器計算能力帶來的巨大挑戰(zhàn)。奎芯科技將會用兩篇文章來詳細(xì)介紹處理器計算性能提升遇到的挑戰(zhàn)和后摩爾時代解決性能提升瓶頸的方法及相關(guān)IP的突破和創(chuàng)新,特別是以奎芯為代表的國產(chǎn)化的IP創(chuàng)新。

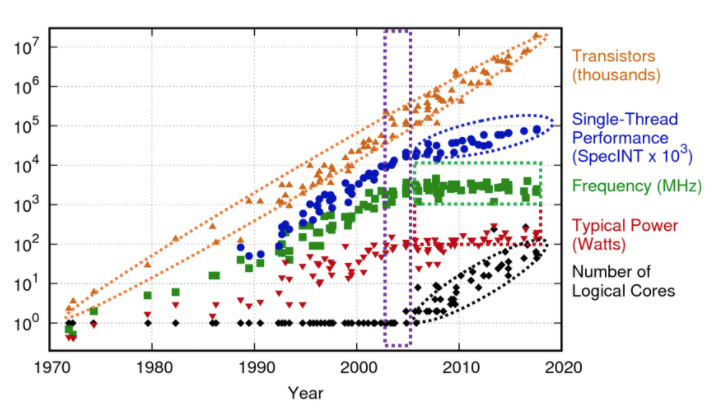

挑戰(zhàn)一:登納德縮放定律失效,摩爾定律放緩

自2015年起,通用CPU的發(fā)展遇到了一系列技術(shù)瓶頸,其單核性能提升比例由上世紀(jì)80年代的每年22%降低至現(xiàn)在的3%,處理器性能提升速度逐年放緩,摩爾定律放緩已經(jīng)成為事實。另外,Denard Scaling定律也在2005年左右就已失效。單核性能的增加很大程度上并不是由過去所簡單依賴的頻率提升帶來的,而是通過架構(gòu)和編譯器的優(yōu)化以實現(xiàn)指令自動并行化,數(shù)據(jù)向量化等方式實現(xiàn)。(同時Amdahl's Law提示多核架構(gòu)的速度提升取決于程序中有多少部分無法并行,多核架構(gòu)目前的性能提升也會變得越來越慢)。即便如此,目前通過指令并行方式來榨取處理器性能的增加也達(dá)到了瓶頸。

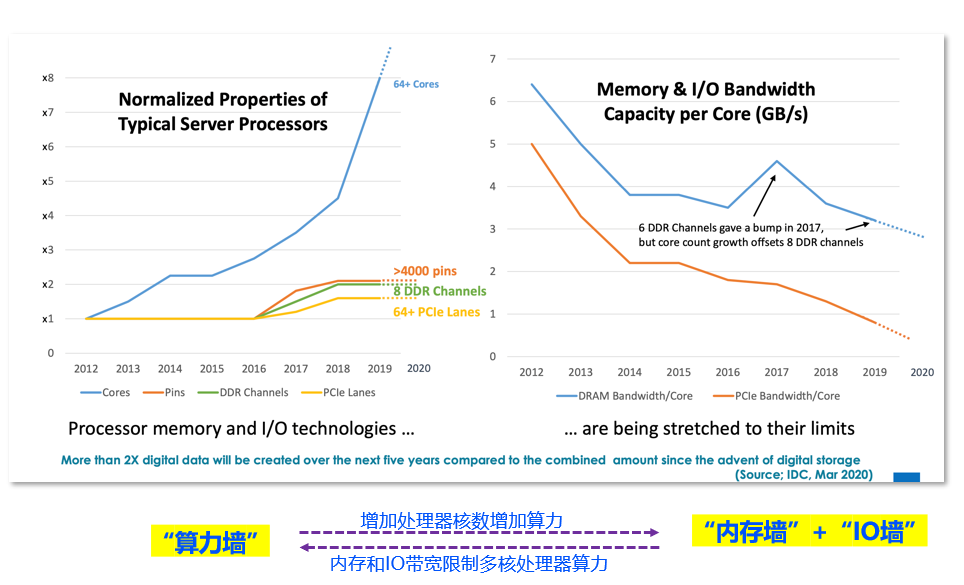

挑戰(zhàn)二:內(nèi)存和IO帶寬發(fā)展跟不上處理器核數(shù)增長

由于單核性能限制(算力墻+功耗墻),目前通用的做法是增加處理器核數(shù)來增加數(shù)據(jù)處理能力,但問題是我們在增加處理器核心數(shù)的同時,又面臨著內(nèi)存容量和帶寬的不足,以及IO的帶寬瓶頸(內(nèi)存墻+IO墻)。從上圖可以看到,左邊顯示從2012-2019年服務(wù)器CPU核數(shù)(從8核到64核)增長了8倍,而Pin針腳數(shù)量(從LGA-2011到4094/4189)和內(nèi)存通道數(shù)(從4到8)僅增長了2倍,PCIe lane 數(shù)增加(從40到64,如果是AMD則按照雙路中每CPU支持來算)甚至還不到2倍,可以看出內(nèi)存和I/O帶寬跟不上計算密度的增長。同時,通過計算得出,平均每核心DRAM內(nèi)存帶寬,以及每核心PCIe帶寬,都是呈不斷下降趨勢。

所以,未來算力的持續(xù)增長需要通過多元化的方式來實現(xiàn),在底層材料技術(shù)沒有實質(zhì)性突破、縱向擴(kuò)展到達(dá)極限的情況下,需要上層的架構(gòu)革新來采用更大規(guī)模的并行或異構(gòu)計算等方式去橫向擴(kuò)展來滿足需求。未來的計算領(lǐng)域?qū)⒅饾u從以計算為中心轉(zhuǎn)向為以數(shù)據(jù)為中心,因此如何高效的傳輸數(shù)據(jù)將成為關(guān)鍵。

現(xiàn)在,我們有機(jī)會通過一系列的技術(shù)創(chuàng)新,打破能效墻、散熱墻、優(yōu)化墻、內(nèi)存墻和高速IO墻,進(jìn)一步釋放計算潛能,計算產(chǎn)業(yè)已進(jìn)入架構(gòu)創(chuàng)新的黃金時代!

下一篇我們將會給大家?guī)砗竽枙r代解決性能提升瓶頸的方法及相關(guān)IP的突破與創(chuàng)新,特別是以奎芯為代表的國產(chǎn)化IP創(chuàng)新,敬請大家期待。

關(guān)于奎芯科技(MSQUARE):

奎芯科技(M SQUARE)于2021年在上海注冊成立,是一家專業(yè)的集成電路IP供應(yīng)商。作為芯片產(chǎn)業(yè)鏈上游關(guān)鍵技術(shù)環(huán)節(jié)的企業(yè),公司推出的高速接口IP,涵蓋USB、PCIe、SATA、SerDes、MIPI、DDR、HDMI、DP、HBM等產(chǎn)品,聚焦高性能計算、人工智能、消費(fèi)類電子、汽車電子、物聯(lián)網(wǎng)等領(lǐng)域,致力于通過先進(jìn)半導(dǎo)體IP研發(fā)與定制服務(wù),打造市場急需的IP組合,積極響應(yīng)中國快速發(fā)展的芯片和應(yīng)用需求﹐全面賦能芯片設(shè)計產(chǎn)業(yè)。