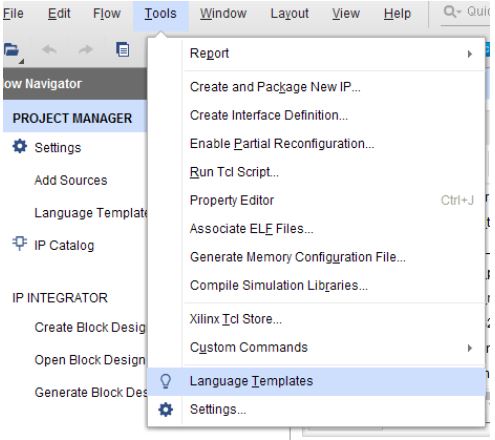

首先,什么是XPM?可能很多人沒聽過也沒用過,它的全稱是Xilinx Parameterized Macros,也就是Xilinx的參數(shù)化的宏,跟原語的例化和使用方式一樣。可以在Vivado中的Tools->Language Templates中查看都有哪些XPM可以例化。

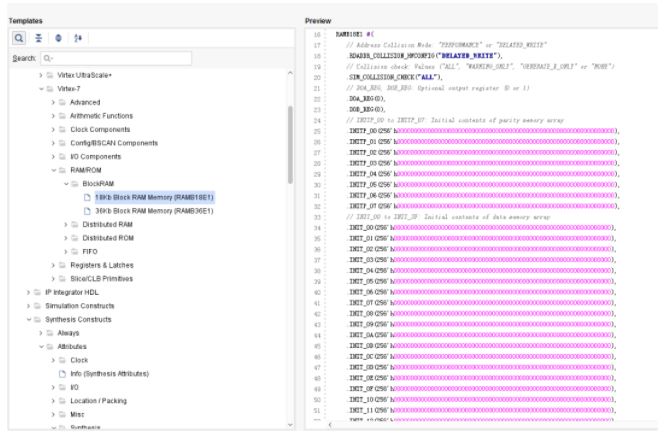

從上圖中可以看出,目前可以例化的XPM主要有三種:跨時(shí)鐘域處理、FIFO和MEMORY。

我們以MEMORY為例,在Vivado中可以通過下面四種方式調(diào)用FPGA中的存儲(chǔ)單元,均可以選擇是Block RAM還是Distributed RAM.

方法1:RTL代碼

我們?cè)诙x一個(gè)memory變量后,可以在前面指定其資源類型:

(*ram_style = “block” *)reg [3:0] mem_bram [15:0] ;

(*ram_style = “distributed” *)reg [3:0] mem_dram [15:0] ;

使用RTL代碼的方式非常靈活,但由于少了很多的控制項(xiàng),綜合后的結(jié)果可能不是最優(yōu)的。

方法2:原語(PrimiTIve)

使用原語也可以例化MEMORY,但沒見幾個(gè)工程師這么用過,因?yàn)榻涌趯?shí)在太多了,所以實(shí)用性不高。

方法3:IP Core

這種方式應(yīng)該是使用最多的,但缺點(diǎn)也很明顯:

當(dāng)修改參數(shù)時(shí)需要重新打開IP,然后Generate;

不同版本的Vivado之間還需要進(jìn)行Update;

有時(shí)沒注意到IP中的參數(shù),導(dǎo)致結(jié)果并不是自己想要的;

最近在調(diào)試中就碰到這樣一個(gè)問題,F(xiàn)IFO中的默認(rèn)輸出延遲是1,即輸出數(shù)據(jù)比讀使能晚一拍,而且Output Registers默認(rèn)是不勾選的。但這個(gè)選項(xiàng)不知道什么時(shí)候被改了,導(dǎo)致程序最終的輸出結(jié)果一直有問題,在debug時(shí)一直檢查的是RTL代碼,直到定位到FIFO模塊時(shí)才發(fā)現(xiàn)了這個(gè)問題。如果此時(shí)我們使用的是XPM,那從代碼中很容易就能看出來錯(cuò)誤。

方法4:XPM_MEMORY

相對(duì)而言,XPM的缺點(diǎn)就不是很明顯,純代碼例化的方式更加靈活、簡(jiǎn)單。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<