過(guò)去,光刻機(jī)是延續(xù)摩爾定律的重要工具。EUV 光刻機(jī)是 7nm 時(shí)代的重大技術(shù)變革,EUV 是讓芯片突破7nm、5nm的關(guān)鍵工具。但隨著光刻機(jī)的演進(jìn),光刻機(jī)的更新速度正在減慢。那么是否有其他的技術(shù)能夠在下一代光刻機(jī)出現(xiàn)之前延續(xù)摩爾定律呢?

近日,三星表示正計(jì)劃在2 nm代工工藝中使用背面供電網(wǎng)絡(luò) (BSPDN) 技術(shù)。事實(shí)上,除了三星,英特爾和臺(tái)積電都已經(jīng)涉足這一技術(shù),BSPDN也被產(chǎn)業(yè)視作可以讓芯片突破3nm的關(guān)鍵技術(shù)之一,除了晶圓代工廠半導(dǎo)體設(shè)備廠商也已經(jīng)針對(duì)這一技術(shù)展開(kāi)了布局。那么,背面供電技術(shù)是什么?將在摩爾定律中起到什么作用?除了BSPDN技術(shù),還有哪些技術(shù)會(huì)延續(xù)摩爾定律?

背面供電工藝是什么?

背面供電是通過(guò)將供電網(wǎng)絡(luò)與邏輯 IC 中的信號(hào)金屬化方案分離,減輕線路后端的布線擁塞并提供電源性能優(yōu)勢(shì)。BSPDN 試圖解決晶體管縮放中日益嚴(yán)重的電力輸送問(wèn)題。電阻問(wèn)題是電氣工程中的一個(gè)基本問(wèn)題。電阻是材料抵抗電流強(qiáng)度的一種屬性。像銅這樣的材料的電阻從來(lái)都不是限制因素,但隨著銅線縮小,電阻開(kāi)始呈指數(shù)級(jí)上升。

通過(guò)系統(tǒng)架構(gòu)重新設(shè)計(jì)和 3D 集成技術(shù)實(shí)現(xiàn)的異構(gòu) 3D-SOC 方法已被證明是提高系統(tǒng)性能的一種有吸引力的方法。通過(guò)利用底部晶圓的背面進(jìn)行功率傳輸和/或信號(hào)路由,可以獲得額外的性能提升。當(dāng)晶體管尺寸不能變得更小時(shí),向上堆疊或許是延續(xù)摩爾定律的新路徑。連續(xù)的層會(huì)導(dǎo)致電壓降低,這會(huì)導(dǎo)致在電阻升高。目前產(chǎn)業(yè)采用的過(guò)渡解決方案是新的金屬層,例如鈷。鈷幫助這些電線保持足夠的電荷,以將信號(hào)和電力傳輸?shù)骄w管工作,但是這種關(guān)系正在達(dá)到一個(gè)基本極限。這在某種程度上阻礙了制造更小的晶體管的能力。

半導(dǎo)體中的底層對(duì)于關(guān)鍵層(實(shí)際晶體管本身)的總體設(shè)計(jì)至關(guān)重要。但在正面制作這些巨大的堆棧會(huì)帶來(lái)更大的問(wèn)題,這就是BSPDN 發(fā)揮作用的地方。拆分信號(hào)層和電源層是一個(gè)技巧,可以比從幾何特征的物理角度縮小更多地縮放晶體管尺寸,所以研究者們正在重組半導(dǎo)體結(jié)構(gòu)的內(nèi)部,通過(guò)將電源信號(hào)和信號(hào)線移除為僅一條信號(hào)線將為更多晶體管騰出空間。BSPDN 將通過(guò)將信號(hào)層放置在芯片的頂部而將電源層放置在芯片的底部來(lái)實(shí)現(xiàn)這一點(diǎn)。

BSPDN的優(yōu)勢(shì)與挑戰(zhàn)

BSPDN 的概念是在 2019 年被 IMEC 首次提出,IMEC的研究人員Dragomir Milojevic、Geert Van der Plas 和 Eric Beyne等人深入研究探討了迄今為止各種有前途的方法,他們?cè)?021年 IEEE國(guó)際電子器件會(huì)議上發(fā)表的兩篇論文中介紹了3D-SoC設(shè)計(jì)和特定電路中背面互連的優(yōu)勢(shì)。

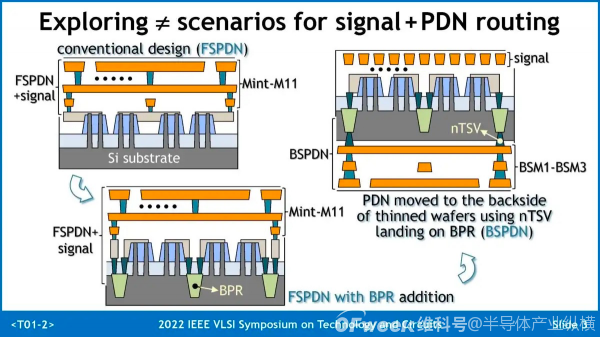

與 FSPDN 相比, BSPDN 的性能提高了 44%,而電源效率提高了 30%。利用這些芯片的‘空閑’背面進(jìn)行信號(hào)路由或直接為‘邏輯晶圓’中的晶體管供電。傳統(tǒng)上,信號(hào)網(wǎng)絡(luò)和電力傳輸都放在晶圓的正面,它們?cè)趶?fù)雜的后端(BEOL)互連方案中爭(zhēng)奪空間。在這些設(shè)計(jì)中,硅片的背面僅用作載體。

在當(dāng)今的處理器中(左),信號(hào)和功率都從上方到達(dá)硅 (淺灰色)。BSPDN將分離這些功能,節(jié)省電力并為信號(hào)路徑騰出更多空間(右),來(lái)源:IEEE Spectrum

imec 與英國(guó) Arm 合作,對(duì)背面供電方式進(jìn)行了量化評(píng)估。Arm 通過(guò)仿真實(shí)驗(yàn)顯示了在 CPU 設(shè)計(jì)中用 BSPDN 帶來(lái)的有益影響,該CPU是由IMEC開(kāi)發(fā)的3nm工藝制作的。在此設(shè)計(jì)中,位于晶圓減薄的背面上的互連金屬通過(guò)位于埋入式電源軌(BPR)上的硅通孔(TSV)與晶圓正面的3nm晶體管相連接。Arm 的研究人員發(fā)現(xiàn) BPR 本身可以構(gòu)建一個(gè)比普通前端供電網(wǎng)絡(luò)效率高 40% 的電力網(wǎng)絡(luò)。

imec 與 Cadence 合作評(píng)估和優(yōu)化了部分從背面布線的 SRAM 宏和邏輯電路設(shè)計(jì)。結(jié)果顯示,與正面布線相比,BSPDN在改善長(zhǎng)互連信號(hào)布線的延遲和電源效率方面明顯更有利。對(duì)于SRAM宏,得到高達(dá)44%的性能提升和高達(dá)30%的電源效率提升。對(duì)于邏輯單元,BSPDN使速度提高了2.5倍,能效提高了60%。

雖然優(yōu)勢(shì)明顯,但BSPDN要真正商用還有一定距離。真正的背面供電網(wǎng)絡(luò)的實(shí)現(xiàn)伴隨著額外的技術(shù)復(fù)雜性。需要一種專(zhuān)用的晶圓減薄工藝以及處理將器件晶圓背面電連接到正面的納米硅通孔 (n-TSV) 的能力。

多家半導(dǎo)體大廠開(kāi)啟BSPDN研究

英特爾和臺(tái)積電都宣布了將在 2nm 工藝中使用 BSPDN。英特爾和臺(tái)積電的競(jìng)爭(zhēng)力路線圖在很大程度上取決于 BSPDN 的實(shí)施,可以說(shuō)英特爾的整個(gè)轉(zhuǎn)變都取決于這項(xiàng)技術(shù)。

英特爾將自家的BSPDN稱(chēng)為Power Via,英特爾將通過(guò)Power Via技術(shù)和RibbonFET實(shí)現(xiàn)自己的2nm。這是 Pat Gelsinger 和英特爾對(duì)其架構(gòu)的一次大膽嘗試。對(duì)于英特爾來(lái)說(shuō),這或許是在先進(jìn)工藝上重新奪回領(lǐng)先的機(jī)遇。

相對(duì)于英特爾來(lái)說(shuō),臺(tái)積電對(duì)BSPDN技術(shù)的應(yīng)用更加保守。臺(tái)積電選擇的 BSPDN 實(shí)現(xiàn)方法是一種低復(fù)雜度的埋入式電源軌,這種技術(shù)成功率比較高,因?yàn)榭梢栽诂F(xiàn)有的工具上完成。

如果英特爾因?yàn)椴荒芨缡褂肊UV 失去了對(duì)臺(tái)積電的領(lǐng)先優(yōu)勢(shì),那么臺(tái)積電就可能會(huì)因?yàn)椴徊扇》e極的設(shè)計(jì)舉措來(lái)提高性能而失去其在晶體管密度方面的領(lǐng)先優(yōu)勢(shì)。隨著三星的加入,三家在先進(jìn)制程上競(jìng)爭(zhēng)的代工廠全部加入了BSPDN的研究,這也意味著B(niǎo)SPDN 可能會(huì)成為一個(gè)巨大的拐點(diǎn)。

除了晶圓制造公司,他們上游的設(shè)備公司也在BSPDN領(lǐng)域展開(kāi)了研究。應(yīng)用材料公司與 BESI 合作推出的Die-to-Wafer 工具,Tokyo Electron 提供的一種新Wafer to Wafer工具。這些市場(chǎng)是巨大的增量增長(zhǎng)驅(qū)動(dòng)力,背面供電的布線的設(shè)備預(yù)計(jì)將以現(xiàn)在晶圓制造的設(shè)備3 倍的增長(zhǎng)速度增長(zhǎng)。

突破3nm,還有哪些關(guān)鍵技術(shù)?

先進(jìn)制程經(jīng)歷了從平面到 FinFET、到 GAA以及最終帶有 BSPDN 的 GAA 的轉(zhuǎn)變。英特爾、臺(tái)積電、三星不約而同的選擇表明了想要突破2nm單獨(dú)在晶體管結(jié)構(gòu)上創(chuàng)新是不夠的,摩爾定律將不再依賴(lài)完全于通過(guò)光刻機(jī)實(shí)現(xiàn)晶體管尺寸縮放。那么是否還可以從哪一環(huán)節(jié)可以在更小的面積內(nèi)讓芯片的效率變得更高呢?當(dāng)制程進(jìn)入3nm,縮放問(wèn)題已經(jīng)開(kāi)始走向垂直,在這一過(guò)程中先進(jìn)封裝開(kāi)始扮演越來(lái)越重要的角色。

作為一種新技術(shù)BSPDN其實(shí)就是先進(jìn)封裝趨勢(shì)的持續(xù)延伸。傳統(tǒng)上我們只在一側(cè)制造半導(dǎo)體,但現(xiàn)在我們已經(jīng)開(kāi)始使用混合鍵合將芯片鍵合在一起。工程師們意識(shí)到我們可以將電源層粘合到芯片的底部,從而節(jié)省空間并解決電阻問(wèn)題。

無(wú)論是延續(xù)摩爾定律,還是超越摩爾定律,都離不開(kāi)先進(jìn)封裝技術(shù),先進(jìn)封裝有望成為撬動(dòng)半導(dǎo)體產(chǎn)業(yè)繼續(xù)向前的重要杠桿。傳統(tǒng)的封裝技術(shù)通常指先將晶圓切割成單個(gè)芯片,再進(jìn)行封裝的工藝形式,其包括雙排直立式封裝DIP與球格陣列封裝BGA,需要焊接線路。先進(jìn)封裝包括倒裝、凸塊、晶圓級(jí)封裝、2.5D封裝、3D封裝等封裝技術(shù),其技術(shù)并不需要用到線路焊接的方式。

先進(jìn)封裝成為了臺(tái)積電、英特爾以及三星三家代工廠新的發(fā)力點(diǎn)。在先進(jìn)封裝技術(shù)上,臺(tái)積電在 CoWoS? 和 InFO 系列封裝技術(shù)發(fā)力,以實(shí)現(xiàn)更好的性能、功率、外形和功能系統(tǒng)級(jí)集成。英特爾在先進(jìn)封裝技術(shù)領(lǐng)域,擁有包括如 EMIB 和 Foveros,以幫助芯片設(shè)計(jì)企業(yè)整合不同的計(jì)算引擎和制程技術(shù)。今年 9 月舉行的英特爾 On 技術(shù)創(chuàng)新峰會(huì)上,帕特·基辛格介紹,英特爾代工服務(wù)將開(kāi)創(chuàng)“系統(tǒng)級(jí)代工的時(shí)代”,英特爾也將提供封裝業(yè)務(wù)。三星推出了2.5D封裝技術(shù)I-Cube和3D封裝技術(shù)X-Cube,可基于TSV硅穿孔技術(shù)將不同芯片堆疊,目前已用于7nm及5nm工藝。

High-NA 將有助于解決分辨率錯(cuò)誤,但對(duì)于2nm或更先進(jìn)的節(jié)點(diǎn)來(lái)說(shuō),下一站將是制造過(guò)程中更先進(jìn)的封裝類(lèi)型創(chuàng)新。這是對(duì)半導(dǎo)體工藝的又一次長(zhǎng)期技術(shù)考驗(yàn)。三家最大晶圓廠的命運(yùn)取決于先進(jìn)封裝的策略,而不再是光刻的技術(shù)。當(dāng)光刻機(jī)成為可控變量后,這些封裝的選擇是推動(dòng)芯片制程前進(jìn)的下一條重要因素。

先進(jìn)封裝的重要性意味著后端封裝公司的重要性也日益增加。這也是設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO)成為產(chǎn)業(yè)熱門(mén)的因素之一。長(zhǎng)電科技就表示要打造有競(jìng)爭(zhēng)力的產(chǎn)品要做到產(chǎn)業(yè)鏈協(xié)同、多尺度協(xié)同設(shè)計(jì)、多物理場(chǎng)協(xié)同設(shè)計(jì)、設(shè)計(jì)與制程工藝協(xié)同。這反映了一個(gè)趨勢(shì),即延續(xù)摩爾定律將需要是各個(gè)環(huán)節(jié)的參與者的共同努力。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<