3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術(shù)研討會期間發(fā)布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產(chǎn)品的新成員。在后摩爾時代的趨勢下,F(xiàn)inFET 晶體管的體積在 TSMC 3nm 工藝下進(jìn)一步縮小,進(jìn)一步采用系統(tǒng)級封裝設(shè)計(SiP)。通過結(jié)合工藝技術(shù)的優(yōu)勢與 Cadence 業(yè)界領(lǐng)先的數(shù)字信號處理(DSP)SerDes 架構(gòu),全新的 112G-ELR SerDes IP 可以支持 45dB 插入損耗,擁有卓越的功耗、性能、面積(PPA)指標(biāo),是超大規(guī)模 ASICs,人工智能/機(jī)器學(xué)習(xí)(AI/ML)加速器,交換矩陣片上系統(tǒng)(SoCs)和 5G 基礎(chǔ)設(shè)施應(yīng)用的理想選擇。

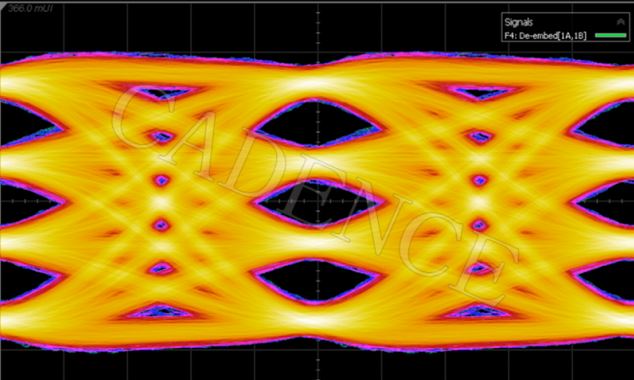

Cadence 112G-ELR SerDes 在 TSMC 3nm 工藝環(huán)境下的眼圖(106.25 Gbps PAM4)

ELR SerDes PHY 符合 IEEE 和 OIF 長距離(LR)標(biāo)準(zhǔn),在基礎(chǔ)規(guī)格之外提供了額外的性能裕度。上方圖片展示了三個張大的眼圖,它們在 PAM4 模式下具有良好的對稱性,將四個信號電平分開。3nm 演示展示了 E-10 級的卓越誤碼率(BER)性能以及 39dB bump 間通道,與 28dB Ball 間插損誤碼率小于 1E-4 的標(biāo)準(zhǔn)規(guī)格相比提供了充足的性能余量。

TSMC 3nm 工藝環(huán)境下的 Cadence 112G-ELR SerDes 測試板

112G-ELR SerDes IP 同時支持中距離(MR)和超短距離(VSR)應(yīng)用,實現(xiàn)不同信道更靈活的功耗節(jié)省。NRZ 和 PAM4 信號下的數(shù)據(jù)傳輸速率從 1G 到 112G,實現(xiàn)背板,直連線纜(DAC),芯片間以及芯片到模塊的可靠高速數(shù)據(jù)傳輸。

SerDes IP 采用領(lǐng)先的基于 DSP 的架構(gòu),通過最大可能性序列檢測(MLSD)和反射抵消技術(shù)實現(xiàn)損耗及反射信道的系統(tǒng)穩(wěn)定。MLSD 技術(shù)可以優(yōu)化 BER,提供更強(qiáng)大的突發(fā)性錯誤處理能力。通過專有的實現(xiàn)技術(shù),Cadence 能確保 MLSD 的功耗開銷最小。反射消除技術(shù)消除了具有實際走線和連接器的產(chǎn)品環(huán)境中的雜散、遠(yuǎn)距離反射,從而提供穩(wěn)健的 BER 結(jié)果。

3nm 工藝下的 Cadence 112G-ELR SerDes 解決方案進(jìn)一步強(qiáng)化了我們在高性能互聯(lián) IP 領(lǐng)域的領(lǐng)導(dǎo)力,是大規(guī)模數(shù)據(jù)中心的理想選擇,客戶也可以從 TSMC 的 3nm 工藝中獲得更顯著的功耗和性能優(yōu)化,是目前在 PPA 和晶體管領(lǐng)域最先進(jìn)的技術(shù)。

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應(yīng)用-AET<<