在汽車電氣化、智能化、網(wǎng)聯(lián)化快速發(fā)展的今天,汽車所用的芯片數(shù)量與種類也日益增多。電氣化引領了汽車電子電氣架構(gòu)的革新,催生出域控制器等集中式大算力芯片和 IGBT 等功率芯片。智能化則引入了多種類的傳感器和 AI 應用,帶動了雷達、激光雷達、攝像頭、智能座艙、5G 車聯(lián)網(wǎng)等模組、處理器、存儲芯片、以及 AI 計算芯片的發(fā)展。

與消費電子芯片相比,車規(guī)級芯片需要滿足更嚴苛的工作環(huán)境、更長久的質(zhì)量保證、更嚴格功能安全的要求。

車規(guī)級芯片的功能安全是設計出來的

功能安全要求一個安全系統(tǒng)在發(fā)生隨機的、系統(tǒng)的、常見的故障時,不會導致安全系統(tǒng)故障,也不會導致人的傷害或死亡、環(huán)境污染、設備或生產(chǎn)損失。

ISO 26262 是汽車行業(yè)廣泛接受的電子功能安全標準,提供了規(guī)范及設計指導原則,貫穿產(chǎn)品從概念開發(fā)、系統(tǒng)、硬件及軟件開發(fā)、生產(chǎn)到報廢的整個開發(fā)過程。由于芯片在汽車系統(tǒng)中扮演著越來越重要的角色,ISO 26262 2018 版本新增加了 11 章節(jié)半導體指南,規(guī)范了覆蓋故障模式、相關(guān)性失效分析 DFA、故障注入等通用技術(shù),以及對數(shù)字、模擬、存儲、可編程器件等半導體部件的具體要求。

完整的仿真、充分的驗證、自動化的過程再現(xiàn)等是 ISO 26262 標準推薦的功能安全芯片設計方法的一般準則,MATLAB 基于模型設計的方法學,能夠幫助工程師快速地自動化地實踐 ISO 26262 標準。

建立芯片最終客戶關(guān)心的應用級功能模型

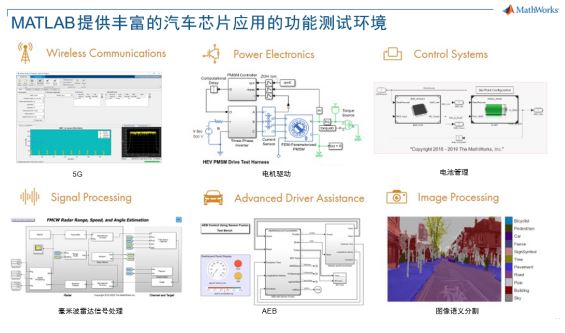

功能正確是功能安全的基礎,智能電動汽車芯片的功能專業(yè)、新穎、復雜,例如激光雷達信號處理、ADAS 視頻圖像處理、電池監(jiān)測傳感器測量與控制、高壓電機驅(qū)動器等,需要在芯片設計研發(fā)階段進行大量的功能建模仿真與分析。基于模型設計方法學的一個核心價值即是建模,建模工作不僅包含芯片內(nèi)部的功能算法模型,也包括測試這些功能所需的外部組件和環(huán)境的構(gòu)建,例如 ADAS NCAP 測試場景、被控電機模型、鋰電池組模型,還包括 SoC 芯片的架構(gòu)分析模型,例如軟硬件劃分、內(nèi)存訪問、總線競爭等等。

MATLAB & Simulink 及各種工具箱為各類智能電動汽車芯片的開發(fā)提供建模、仿真、測試支持,以滿足 ISO 26262 對硅前功能測試的要求。

應用級系統(tǒng)模型能夠幫助芯片工程師確保用來評估設計的驗證簽核(signoff)標準與芯片最終客戶最關(guān)心的標準一致。

“我們的客戶中有相當一部分是Tier 1汽車供應商,他們最關(guān)心的就是規(guī)格書中的各項性能指標,比如信噪比(SNR)和總諧波失真(THD)。他們反倒不太關(guān)心大多數(shù) IC 驗證團隊會關(guān)心的一些主要指標,比如單個組件測試結(jié)果、代碼覆蓋率結(jié)果,以及其他硬件實現(xiàn)級別的指標。另外,我們的客戶利用現(xiàn)場試驗和真實駕駛場景來評估完整的雷達系統(tǒng),而 IC 驗證團隊則使用與真實信號相去甚遠的測試圖形來評估單個射頻、模擬和數(shù)字組件。我和所在團隊定義并實現(xiàn)了流程前置方法學,使得我們驗證 IC 設計的流程與客戶評估 IC 設計的標準保持一致。我們開發(fā)用于虛擬現(xiàn)場試驗的路試駕駛場景基于許多客戶所遵循的 Euro NCAP 標準。我們生成的功能和性能指標(如 SNR)與客戶評估自己產(chǎn)品中的 IC 組件所用的指標相同。”——NXP 雷達芯片工程師。[1]

可仿真的模型不僅有助于提升公司內(nèi)部芯片的設計開發(fā)驗證、下一代產(chǎn)品的迭代優(yōu)化效率,也可以虛擬處理器(vCPU)的方式服務早期客戶,搶占市場先機。

自動化功能安全的驗證

這是一個機器人與 AI 技術(shù)開始盛行的年代,基于模型設計的研發(fā)流程和嵌入在流程中的各種自動化工具正在越來越多的被汽車工程師和芯片工程師所采用。

ISO 26262 功能安全標準要求對芯片進行功能和結(jié)構(gòu)覆蓋率驅(qū)動的驗證。而根據(jù)業(yè)內(nèi)的調(diào)研結(jié)果,芯片開發(fā)過程中驗證占用了 50%的時間。使用自動化工具提高驗證效率變得非常有意義。

芯片驗證工作通常由芯片驗證工程師完成,日常地掙扎于算法專家和 RTL實現(xiàn)工程師的溝通洪流中。基于模型設計可以顯著提高芯片驗證效率,通過將驗證前移,提高芯片算法的質(zhì)量,從而減少算法、實現(xiàn)和驗證的迭代次數(shù);同時在算法、實現(xiàn)和驗證傳遞可仿真的模型,也比傳遞文檔能夠減少許多溝通誤差。

在芯片模型上,工程師可以使用 Simulink CoverageTM 測量芯片模型和生成代碼中的測試覆蓋率,識別缺失的測試或意外的功能,并在圖表上查看覆蓋率結(jié)果;或者借助 Simulink Design VerifierTM 使用形式化方法識別芯片設計錯誤,發(fā)現(xiàn)難以發(fā)現(xiàn)的死邏輯和設計缺陷,自動生成測試向量以分析缺失的覆蓋率,形式化地證明設計符合需求。

為加快汽車顯示芯片圖像處理 IP 核的設計和實施,瑞薩工程師采用了 MATLAB? 和 Simulink? 的基于模型的設計:“與傳統(tǒng)的設計流程相比,采用基于模型的設計,我們能更早地驗證我們的算法和系統(tǒng)功能,更快地適應需求指標變更,評估更多的設計替代方案。基于模型的設計幫助在算法專家和 RTL 工程師之間架起橋梁。”[2]

快速原型及 RTL 自動化生成

為了應對日益增加的競爭壓力,芯片制造商正在縮短交貨時間表;另一方面,即使設計變得越來越復雜,客戶對質(zhì)量和性能的期望也在提高。許多公司發(fā)現(xiàn),傳統(tǒng)的設計方法——即團隊對規(guī)范進行基于文檔的驗證,并在最終生產(chǎn)版本之前生產(chǎn)多個原型已經(jīng)無法跟上行業(yè)當前的步伐。

在模型充分驗證之后,HDL Coder 可以從模型自動生成可綜合的符合行業(yè)編碼標準的VHDL 或 Verilog 代碼,自動實現(xiàn) FPGA-in-the-loop 原型驗證,也可以通過自動生成 SystemVerilog 或 UVM 測試環(huán)境以復用模型中的測試激勵和框架,從而大大提高芯片 RTL 開發(fā)效率。MathWorks ASIC/FPGA 工作流程支持 ISO 26262 功能安全標準,HDL Coder 是 ISO 26262 認證的開發(fā)工具。

“我們從 2014 年開始研究將 Simulink MBD 用于 ASIC 開發(fā)。硅驗證已證明自動生成的代碼 0 bug”來自 Allegro Microsystems 的經(jīng)驗分享。[3] Allegro 為開發(fā)高完整性汽車傳感器芯片采用了基于模型的混合信號 IC 設計流程。

確認芯片底層軟件的功能安全

芯片的運行還要有軟件支持,車規(guī)級芯片制造商需為客戶提供滿足功能安全的硬件和底層軟件。底層軟件甚至是功能安全的必要組成部分,幫助避免系統(tǒng)硬件故障以及檢測和控制隨機硬件故障,例如 FMEDA,clock monitoring,power monitoring,ECC protection of RAM/ROM。更多的情況下,低層軟件幫助汽車 OEM 和開發(fā)人員構(gòu)建符合安全認證的應用,比如 AUTOSAR MCAL,firmware,sensor drivers,safety monitoring,safety-certified library。

PolyspaceTM 可以對芯片底層軟件進行符合 ISO 26262 功能安全的驗證。Polyspace 是基于抽象解釋原理的代碼級靜態(tài)分析和驗證工具,使用形式化分析方法,無需測試用例,即能對代碼進行窮盡分析。把代碼中有問題和沒問題的計算操作通過顏色完全區(qū)分開,方便底層軟件工程師聚焦問題。

Elektrobit 開發(fā) AUTOSAR 基礎軟件,幫助橋接芯片廠商和汽車廠商。確保符合道路車輛的 ISO 26262 功能安全標準涉及證明設計滿足安全要求,架構(gòu)準確反映設計,以及架構(gòu)正確實施。Elektrobit 工程師使用 Polyspace Code ProverTM完成耗時的第三階段[4]。Polyspace 的形式化方法內(nèi)核還幫助 Elektrobit 驗證高度可配置軟件,從耗時的數(shù)千次的邊界檢查方法中解脫。他們還是用并行問題證明,減少非必要的互斥鎖,從而提高軟件的性能。

服務汽車行業(yè)客戶事半功倍

汽車行業(yè)廣泛采用基于模型的設計(Model-Based Design)開發(fā)流程,汽車芯片廠商為自家芯片提供基于 Simulink 的高效、高性能、安全認證的硬件支持包,能更好地服務客戶。典型的例如,Infineon Aurix 高性能 MCU 支持包,NXP model-based design toolbox等。這些支持包能夠?qū)?Simulink 算法生成針對芯片優(yōu)化的代碼部署到芯片上,有效地將算法裁剪為異構(gòu)硬件架構(gòu),配置和生成所有必要的底層軟件,使用處理器在環(huán) PIL 進行測試,生成啟動點以在 Synopsys Virtualizer 和硬件上測試代碼等,從而幫助汽車行業(yè)工程師縮短項目開發(fā)周期。

小結(jié)

車規(guī)級芯片需要滿足汽車功能安全標準 ISO 26262 的各項要求,MATLAB 基于模型設計方法幫助芯片開發(fā)過程符合功能安全標準的一般準則,包括完整的仿真、充分的驗證、自動化的過程再現(xiàn),并提供一系列工具提高芯片系統(tǒng)與功能建模、驗證自動化、原型和 RTL 實現(xiàn)、底層軟件驗證等過程的質(zhì)量和效率。與此同時,車規(guī)級芯片未來的客戶們——汽車行業(yè)工程師正在廣泛使用基于模型設計方法開發(fā)智能電動汽車應用。

參考文獻[1]https://ww2.mathworks.cn/company/newsletters/articles/environment-in-the-loop-verification-of-automotive-radar-ic-designs.html?s_tid=srchtitle_%25E6%2581%25A9%25E6%2599%25BA%25E6%25B5%25A6_2

[2]https://ww2.mathworks.cn/company/user_stories/renesas-designs-and-implements-image-processing-ip-core-for-asics-with-model-based-design.html

[3]https://ww2.mathworks.cn/videos/a-mixed-signal-model-based-design-flow-for-automotive-sensors-1481312986577.html?s_tid=srchtitle_allegro_1

[4] https://ww2.mathworks.cn/company/newsletters/articles/removing-run-time-errors-from-autosar-components-using-polyspace-code-verifiers.html?s_tid=srchtitle_Elektrobit_1

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應用-AET<<