最新消息,近日佳能(Canon)發(fā)布了一個名為 FPA-1200NZ2C 的納米壓印半導(dǎo)體制造設(shè)備,號稱通過納米壓印光刻(NIL)技術(shù)實現(xiàn)了目前最先進的半導(dǎo)體工藝。

官方表示,該技術(shù)采用與傳統(tǒng)投影曝光技術(shù)不同的方法形成電路圖案,未來要擴大該類半導(dǎo)體設(shè)備的陣容來覆蓋廣泛的市場需求。

據(jù)悉,NIL 技術(shù)可以形成最小線寬為 14nm 的圖案(相當于現(xiàn)在 5nm 節(jié)點工藝),而且通過進一步改進掩模,還將有可能支持 10nm 的最小線寬(相當于 2nm 節(jié)點工藝)。

大家知道,ASML 的光刻機(EUV)是通過特定光線照射在涂有光刻膠的晶圓上,從而將電路打印到芯片上,本次佳能的設(shè)備則更類似于 “印刷” 而不是 “投影”。

佳能的 NIL 設(shè)備先是通過將掩模直接壓到晶圓的抗蝕劑層上,將電路圖完整地轉(zhuǎn)移過去。

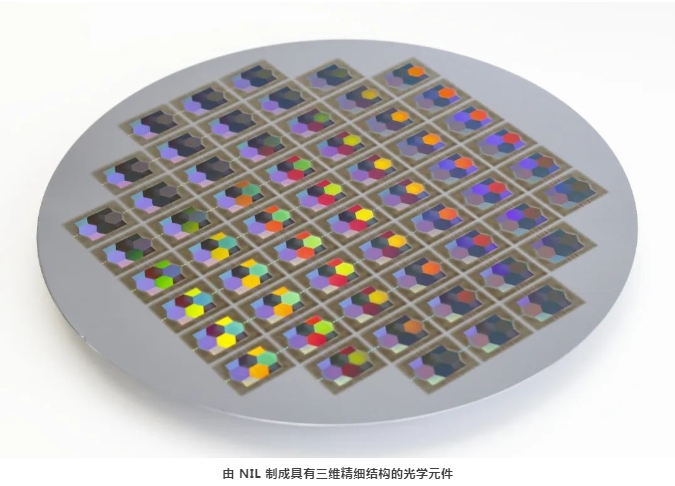

然后用自家的噴墨技術(shù)將適量的抗蝕劑添加到合適的位置,最后將掩模印在涂有抗蝕劑的晶圓上進?精準曝光。單?壓印即可形成復(fù)雜的 2D 或 3D 電路圖。

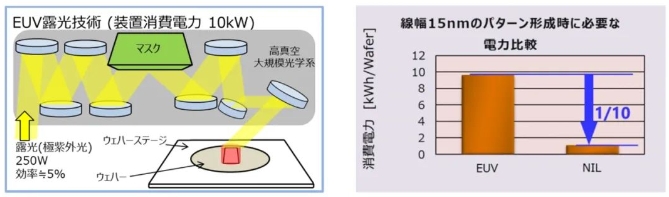

官方稱該設(shè)備結(jié)構(gòu)簡單,由于不需要 EUV 的大規(guī)模特殊波長光學(xué)系統(tǒng)和真空腔,所以基于 NIL 技術(shù)的設(shè)備得以大幅縮小體積。

此外,該設(shè)備可?更小的功率形成精細圖案,相比傳統(tǒng)的 EUV 投影曝光設(shè)備在形成圖案時對應(yīng)的功耗可降低至 1/10,同時也顯著減少了碳排放。

該設(shè)備的環(huán)境控制新技術(shù)可抑制內(nèi)部細顆粒的產(chǎn)生和污染,實現(xiàn)多層半導(dǎo)體制造所需的高精度對準,并減少由顆粒引起的缺陷,從而可以形成微小且復(fù)雜的電路,為尖端半導(dǎo)體器件的制造做出貢獻。

最后,官方稱該設(shè)備也可用于半導(dǎo)體器件以外的制造,比如用于生產(chǎn)具有數(shù)十納米微結(jié)構(gòu)的 XR 超透鏡等。

納米壓印(Nanoimprint lithography)最早出現(xiàn)于 1996 年,是一種制造納米級圖案的方法,具有低成本、高產(chǎn)量和高分辨率的特點。

鑒于荷蘭光刻機巨頭 ASML 的一家獨大,之前鎧俠等一些日本半導(dǎo)體廠商曾嘗試使用該技術(shù)來替換 EUV,但因為內(nèi)部顆粒污染、良率過低等問題沒能實現(xiàn)商業(yè)化,看來本次佳能可能解決了這些問題。

眾所周知,佳能以相機、光學(xué)設(shè)備或打印機等產(chǎn)品領(lǐng)先而聞名,但隨著半導(dǎo)體和人工智能等領(lǐng)域的發(fā)展而重新開始注重半導(dǎo)體供應(yīng)鏈。

同尼康一樣,兩者在半導(dǎo)體制造設(shè)備的市場競爭中均落后于 ASML。2004 年佳能開始進入納米壓印光刻領(lǐng)域,本次發(fā)布半導(dǎo)體設(shè)備也說明其正在尋求縮小與 ASML 的市場差距。

佳能稱該設(shè)備改進掩模后可達到 2nm 節(jié)點工藝,而值得一提的是,臺積電和三星代工都計劃將于 2025 年開始量產(chǎn)自己 2nm 工藝芯片,對于 NIL 設(shè)備究竟是否能威脅到 ASML EUV 的市場,我們將拭目以待。

更多精彩內(nèi)容歡迎點擊>>電子技術(shù)應(yīng)用<<