光刻機(jī)一直是半導(dǎo)體領(lǐng)域的一個(gè)熱門話題。

從早期的深紫外光刻機(jī)(DUV)起步,其穩(wěn)定可靠的性能為半導(dǎo)體產(chǎn)業(yè)的發(fā)展奠定了堅(jiān)實(shí)基礎(chǔ);再到后來(lái)的極紫外光刻機(jī)(EUV)以其獨(dú)特的極紫外光源和更短的波長(zhǎng),成功將光刻精度推向了新的高度;再到如今的高數(shù)值孔徑光刻機(jī)(High-NA)正式登上歷史舞臺(tái),進(jìn)一步提升了光刻的精度和效率,為制造更小、更精密的芯片提供了可能。

ASML官網(wǎng)顯示,其組裝了兩個(gè)TWINSCAN EXE:5000高數(shù)值孔徑光刻系統(tǒng)。其中一個(gè)由ASM與imec合作開(kāi)發(fā),將于2024年安裝在ASML與imec的聯(lián)合實(shí)驗(yàn)室中,預(yù)計(jì)2025年投入量產(chǎn)。另一個(gè)由英特爾在2018年訂購(gòu), 2023 年 12 月,ASML正式向英特爾交付了首個(gè)High-NA EUV 光刻系統(tǒng)——TWINSCAN EXE:5000的首批模塊。

01 首臺(tái)High-NA EUV光刻機(jī)拆箱

今年1月,ASML首臺(tái)High-NA EUV光刻機(jī)的主要組件抵達(dá)英特爾,隨后在3月初,英特爾分享了一段視頻,展示了在英特爾位于美國(guó)俄勒岡州的 D1X 工廠內(nèi),ASML 工程團(tuán)隊(duì)安裝調(diào)試的部分畫面。

ASML 發(fā)言人 Monique Mols 在公司舉行的媒體參觀活動(dòng)中表示,安裝這臺(tái)重達(dá) 150000 公斤的系統(tǒng)共計(jì)用時(shí) 6 個(gè)月,需要 250 個(gè)集裝箱和 250 名工程師。一旦組裝完成,這臺(tái)機(jī)器將高達(dá)3層樓高,這迫使英特爾建造一個(gè)新的(更高的)廠房擴(kuò)建來(lái)容納它。據(jù)估計(jì),每臺(tái)這樣的High-NA EUV光刻機(jī)的價(jià)格可能在3億至4億美元之間。

值得注意的是,英特爾也是業(yè)界首個(gè)訂購(gòu) TWINSCAN EXE:5200光刻機(jī)的公司,該訂單的下單時(shí)間在2022年1月。

根據(jù)ASML的路線圖,第一代的High-NA EUV光刻機(jī)TWINSCAN EXE:5000或許主要是被晶圓制造商用于相關(guān)實(shí)驗(yàn)與測(cè)試,以便公司更好地了解High-NA EUV設(shè)備的使用,獲得寶貴經(jīng)驗(yàn)。實(shí)際量產(chǎn)將會(huì)依賴于2024年底出貨的TWINSCAN EXE:5200。

02 為什么需要High-NA光刻機(jī)?

DUV向EUV邁進(jìn)

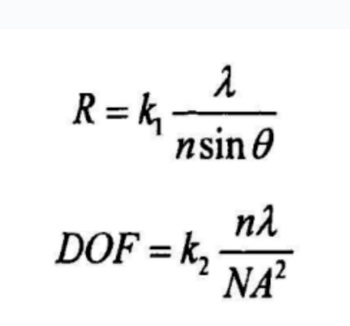

在DUV世代,科學(xué)家們一直進(jìn)行研究將DUV光刻技術(shù) 推向極限。為了減小可光刻的最小特征的尺寸(稱為臨界尺寸 (CD)),可以通過(guò)調(diào)整兩個(gè)主要的參數(shù):光的波長(zhǎng) λ 和數(shù)值孔徑 NA。

光刻分辨率(R)主要由三個(gè)因數(shù)決定,分別是光的波長(zhǎng)(λ)、光可穿過(guò)透鏡的最大角度(鏡頭孔徑角半角θ)的正弦值(sinθ)、折射率(n)以及系數(shù)k1有關(guān)。除了光刻分辨率之外,焦距深度( Depth of Focus,DOF)也至關(guān)重要,大的焦深可以增大刻蝕的清晰范圍,提高光刻的質(zhì)量,而焦距深度也可以通過(guò)提高系統(tǒng)的折射率(n)來(lái)改進(jìn)。

然而,現(xiàn)在的 DUV 系統(tǒng)中已經(jīng)沒(méi)有多少空間可以調(diào)整這些參數(shù)了。

進(jìn)入EUV世代,EUV 光刻則能夠?qū)ΣㄩL(zhǎng)參數(shù)進(jìn)行重大調(diào)整:它使用 13.5 nm 光,而最高分辨率 DUV 系統(tǒng)則使用 193 nm 光。第一個(gè)預(yù)生產(chǎn) EUV 光刻平臺(tái) NXE 于 2010 年首次發(fā)貨時(shí),它的 CD 從 DUV 的 30 nm 以上下降到 EUV 的 13 nm。

此外,EUV光刻機(jī)不僅調(diào)整了波長(zhǎng)參數(shù),還具備光源系統(tǒng)、光學(xué)鏡頭、雙工作臺(tái)系統(tǒng)等核心技術(shù),這些技術(shù)的結(jié)合使得EUV光刻機(jī)能夠?qū)崿F(xiàn)高效的投影光刻,無(wú)損傷地處理任意圖形。

EUV向High-NA EUV邁進(jìn)

ASML目前的EUV工具的數(shù)值孔徑為0.33,可實(shí)現(xiàn)13.5nm左右的分辨率,透過(guò)單次曝光,可以產(chǎn)生26nm的最小金屬間距和25-30nm尖端到尖端的近似互連空間間距,這些尺寸足以滿足4/5nm節(jié)點(diǎn)制程的生產(chǎn)需求。盡管如此,業(yè)界仍然需要更小的21-24nm間距的3nm制程工藝,這就是為什么臺(tái)積電的N3B制程技術(shù)被設(shè)計(jì)為使用標(biāo)準(zhǔn)EUV雙圖案化技術(shù)來(lái)實(shí)現(xiàn)更小的間距,但這種方法將會(huì)相當(dāng)昂貴。

改變波長(zhǎng)之后再進(jìn)一步提升EUV光刻機(jī)的分辨率就要從NA指標(biāo)上下手了。

在這里解釋一下“NA”即光學(xué)系統(tǒng)的數(shù)值孔徑,表示光線的入射角度,使用更大的NA透鏡可以打印出更小的結(jié)構(gòu),目前的EUV光刻機(jī)使用的還是NA=0.33的物鏡系統(tǒng),下一代的目標(biāo)就是NA=0.5及以上的光學(xué)系統(tǒng)。

因此,High-NA應(yīng)運(yùn)而生。目前ASML已經(jīng)開(kāi)始交付的首款High-NA EUV系統(tǒng)數(shù)值孔徑已經(jīng)由傳統(tǒng)EUV的0.33提升到了0.55,分辨率也由13.5nm提升到了8nm,可以實(shí)現(xiàn)16nm的最小金屬間距,對(duì)于2nm以下制程節(jié)點(diǎn)將非常有用。根據(jù)Imec的預(yù)計(jì),這即使對(duì)于1nm節(jié)點(diǎn)技術(shù),High-NA EUV系統(tǒng)也能提供解決方案。另外,在生產(chǎn)效率方面,High-NA EUV系統(tǒng)每小時(shí)可光刻超過(guò) 185 個(gè)晶圓,與已在大批量制造中使用的 EUV 系統(tǒng)相比還有所增加。ASML還制定了到 2025 年將新一代High-NA EUV系統(tǒng)(EXE:5200)的生產(chǎn)效率提高到每小時(shí) 220 片晶圓的路線圖。

03 High-NA EUV光刻機(jī)對(duì)英特爾來(lái)說(shuō)意味什么?

High-NA EUV被認(rèn)為是可以降低工藝復(fù)雜性和制造成本,并是制造2nm及以下的尖端制程的關(guān)鍵設(shè)備。High-NA 不僅需要新的光學(xué)器件,還需要新的光源材料,例如德國(guó)蔡司在真空中制造的一個(gè)由拋光、超光滑曲面鏡組成的光學(xué)系統(tǒng),甚至還需要新的更大的廠房來(lái)容納這種機(jī)器,這都將需要大量投資。

即便如此,為了保持半導(dǎo)體的性能、功率、面積和成本(PPAc)等方面的優(yōu)勢(shì),已經(jīng)領(lǐng)先的制造商們諸如臺(tái)積電、三星、英特爾、SK海力士等世界頭部邏輯芯片和存儲(chǔ)芯片制造商,為了率先并更多拿到ASML最先進(jìn)的光刻機(jī)已經(jīng)爭(zhēng)得不可開(kāi)交。早在 2020 ~ 2021 年,ASML 就表示已經(jīng)收到了三家客戶的 High-NA 意向訂單,共提供多達(dá) 12 套系統(tǒng)。

英特爾率先拿到該設(shè)備,無(wú)疑會(huì)極大地提升其芯片制造能力和效率,并幫助英特爾在未來(lái)先進(jìn)制程技術(shù)的競(jìng)爭(zhēng)中取得先行優(yōu)勢(shì)。通過(guò)使用這種先進(jìn)的光刻技術(shù),英特爾可以生產(chǎn)出2nm及更小、更快的芯片,從而在市場(chǎng)上獲得更大的競(jìng)爭(zhēng)優(yōu)勢(shì)。此外,隨著芯片制程的縮小,英特爾可以進(jìn)一步降低生產(chǎn)成本,提高產(chǎn)品競(jìng)爭(zhēng)力。

此外,在高數(shù)值孔徑學(xué)習(xí)方面,英特爾將領(lǐng)先于其競(jìng)爭(zhēng)對(duì)手,這將為其帶來(lái)多項(xiàng)優(yōu)勢(shì)。具體來(lái)說(shuō),由于英特爾很可能是第一家使用高數(shù)值孔徑工具啟動(dòng)大批量生產(chǎn)的公司,因此晶圓廠工具生態(tài)系統(tǒng)將不可避免地遵循其要求。上述要求可能會(huì)轉(zhuǎn)化為行業(yè)標(biāo)準(zhǔn),這可能會(huì)使英特爾比臺(tái)積電和三星更具優(yōu)勢(shì)。

目前英特爾已經(jīng)完成了英特爾 18A(1.8nm)和英特爾 20A(2nm)制造工藝的開(kāi)發(fā),其中英特爾 20A計(jì)劃于2024年上半年投入使用,而進(jìn)展良好的英特爾 18A制造技術(shù)也將提前到2024年下半年進(jìn)入大批量制造。這表明英特爾對(duì)High-NA EUV技術(shù)的應(yīng)用充滿信心,并計(jì)劃在未來(lái)幾年內(nèi)將這一技術(shù)應(yīng)用于其主要的芯片生產(chǎn)中。High-NA EUV光刻技術(shù),可以給英特爾帶來(lái)更低的生產(chǎn)成本和更高的產(chǎn)品競(jìng)爭(zhēng)力。

綜上所述,英特爾獲得的全球首臺(tái)High-NA EUV光刻機(jī)不僅標(biāo)志著該公司在半導(dǎo)體制造領(lǐng)域的一大進(jìn)步,也展示出其在推動(dòng)先進(jìn)光刻技術(shù)發(fā)展方面的決心和能力。

04 ASML的High-NA EUV光刻機(jī)產(chǎn)量

目前ASML已從英特爾和SK海力士等公司獲得了High-NA EUV光刻機(jī)的訂單,數(shù)量在10至20臺(tái)之間。與此同時(shí),ASML計(jì)劃到2028年,每年生產(chǎn)20臺(tái)High-NA EUV光刻機(jī),以滿足市場(chǎng)的需求。

根據(jù)集邦咨詢的報(bào)告顯示,ASML將在2024年生產(chǎn)最多10臺(tái)新一代High-NA EUV極紫外光刻機(jī),其中英特爾就定了多達(dá)6臺(tái)。

三星也在積極尋求獲得High-NA EUV。2022年 6 月三星電子與ASML就采購(gòu)高數(shù)值孔徑EUV達(dá)成協(xié)議。今年2月,三星電子與荷蘭設(shè)備巨頭ASML再次宣布,將在韓國(guó)共同投資設(shè)立半導(dǎo)體先進(jìn)制程研發(fā)中心,并計(jì)劃自2027年起引入High-NA EUV設(shè)備。

三星此次與ASML的合作表明了其在半導(dǎo)體技術(shù)領(lǐng)域的雄心壯志。通過(guò)共同研發(fā)和引進(jìn)High-NA EUV設(shè)備,三星將能夠進(jìn)一步提升其芯片制造工藝,并在全球半導(dǎo)體市場(chǎng)中獲得更大的競(jìng)爭(zhēng)優(yōu)勢(shì)。值得注意的是,High-NA EUV設(shè)備的引進(jìn)和應(yīng)用也面臨著挑戰(zhàn),包括設(shè)備價(jià)格高昂、良率問(wèn)題以及生產(chǎn)過(guò)程中的技術(shù)難題等。

三星負(fù)責(zé)存儲(chǔ)器生產(chǎn)的研究員Young Seog Kang曾表示:用戶最關(guān)心的是總成本問(wèn)題,前Low-NA已經(jīng)投入使用,相比High-NA EUV,芯片制造商可能更愿意使用更經(jīng)濟(jì)可行的Low-NA EUV以雙重曝光或采用先進(jìn)封裝技術(shù)作為補(bǔ)充。因此High-NA EUV可能更有利于邏輯芯片制造,存儲(chǔ)器或面臨成本問(wèn)題。

相比之下,臺(tái)積電并不急于在短期內(nèi)采用高數(shù)值孔徑 EUV,華興資本董事總經(jīng)理吳思浩說(shuō),臺(tái)積電可能需要數(shù)年時(shí)間才能在 2030 年或以后趕上這一潮流。

SemiAnalysis 和華興資本分析師指出,臺(tái)積電暫時(shí)不會(huì)跟進(jìn)采用這項(xiàng)技術(shù),主因在于,使用高數(shù)值孔徑 EUV 的成本,可能比使用 Low-NA EUV 還高,至少在初期是這樣,盡管低成本的代價(jià)是生產(chǎn)出來(lái)的晶體管密度較低。臺(tái)積電采用EUV的時(shí)間就比三星要晚幾個(gè)月,但是要比英特爾早幾年。

05 Hyper-NA EUV是未來(lái)十年的重要改變

近日,AMSL在其2023年度報(bào)告當(dāng)中還披露了其未來(lái)更為先進(jìn)的Hyper-NA EUV技術(shù)的進(jìn)展。

ASML 技術(shù)長(zhǎng)Martin van den Brink 在ASML 2023 年年度報(bào)告中表示,NA 值高于0.7 的Hyper-NA 微影曝光設(shè)備無(wú)疑的是一個(gè)發(fā)展芯片生產(chǎn)技術(shù)的機(jī)會(huì),而且從2030 年左右開(kāi)始獲得應(yīng)用。預(yù)計(jì),Hyper-NA 微影曝光設(shè)備可能與邏輯芯片最相關(guān),并且將提供比High-NA 微影光設(shè)備更實(shí)惠的解決方案。而對(duì)ASML 來(lái)說(shuō),關(guān)鍵是Hyper-NA 正在推動(dòng)整體EUV 發(fā)展平臺(tái),以改善成本和交貨時(shí)間。

未來(lái),隨著制程工藝的繼續(xù)推進(jìn),當(dāng)進(jìn)入1nm制程工藝節(jié)點(diǎn)之后,晶體管的金屬間距將需要變得更小。屆時(shí)晶圓制造商將需要比High-NA EUV光刻機(jī)更復(fù)雜的工具,這也是ASML為何計(jì)劃開(kāi)發(fā)出具有更高數(shù)值孔徑Hyper NA EUV光刻機(jī)的原因。

憑借晶體管技術(shù)以及先進(jìn)的制造工具的出現(xiàn),2030年將進(jìn)入7埃米(0.7nm)時(shí)代,2032年將有望進(jìn)化到5埃米(0.5nm),2036年將有望實(shí)現(xiàn)2埃米(0.2nm)。

增加投影光學(xué)元件的數(shù)值孔徑是一個(gè)成本高昂的決定,其中牽涉對(duì)微影曝光設(shè)備的設(shè)計(jì)需要進(jìn)行重大改變。特別是這包括機(jī)器的物理尺寸、并需要開(kāi)發(fā)許多新組件,還有成本增加的因素。ASML 最近透露,標(biāo)準(zhǔn)數(shù)值孔徑EUV Twinscan NXE 售價(jià)約為1.83 億美元,而High-NA EUV 的Twinscan EXE 的售價(jià)約為3.8 億美元或更高。

至于,接下來(lái)的Hyper-NA 微影曝光設(shè)備的成本預(yù)計(jì)將會(huì)更高的情況下,ASML 必須解決兩個(gè)問(wèn)題,就是Hyper-NA 微影曝光設(shè)備是否可以在技術(shù)上實(shí)現(xiàn),以及對(duì)于領(lǐng)先的邏輯芯片制造商來(lái)說(shuō)是否在成本上負(fù)擔(dān)得起。當(dāng)前,全球只剩下三個(gè)領(lǐng)先的邏輯芯片制造商,包括英特爾、三星和臺(tái)積電。日本的Rapidus 尚未發(fā)展成為有能力的競(jìng)爭(zhēng)對(duì)手。因此,雖然需要Hyper-NA EUV 微影曝光設(shè)備,但它必須價(jià)格合理。

Martin van den Brink 曾經(jīng)指出,Hyper-NA 微影曝光設(shè)備最終是否導(dǎo)入的決定,將取決于ASML能夠降低成本的程度。然而,在ASML 與客戶討論了Hyper-NA EUV 微影曝光設(shè)備的必要性和可行性之后,客戶使用Hyper-NA EUV 微影曝光設(shè)備來(lái)大規(guī)模生產(chǎn)邏輯和存儲(chǔ)器芯片的技術(shù)條件已經(jīng)存在,這預(yù)計(jì)將是下一個(gè)十年半導(dǎo)體產(chǎn)業(yè)的重要變化。