7月19日消息,據(jù)韓媒TheElec報(bào)道,與三星的3nm制程相比,明年即將量產(chǎn)三星2nm制程將會多出30%的極紫外(EUV)光刻層。

三星于2018 年首次開始在其 7nm 邏輯制程工藝節(jié)點(diǎn)上開始應(yīng)用 EUV,從那時起,隨著遷移到5nm,再到3nm,三星在芯片生產(chǎn)過程中的EUV光刻層的數(shù)量或EUV工藝步驟的數(shù)量也在持續(xù)增長。

報(bào)道援引消息人士的話表示,三星的2nm制程已經(jīng)增加到了 20 層的EUV光刻層。而三星的1.4nm則預(yù)計(jì)將有30多個EUV光刻層。

與此同時,三星也將EUV應(yīng)用于其DRAM生產(chǎn)。三星為其第 6 代 10nm DRAM 應(yīng)用了多達(dá) 7 個 EUV 層,而 SK 海力士則應(yīng)用了 5 個EUV光刻層。隨著越來越多的芯片制造商擴(kuò)大其EUV工藝步驟,光刻膠、空白掩模和薄膜等相關(guān)行業(yè)也有望增長。

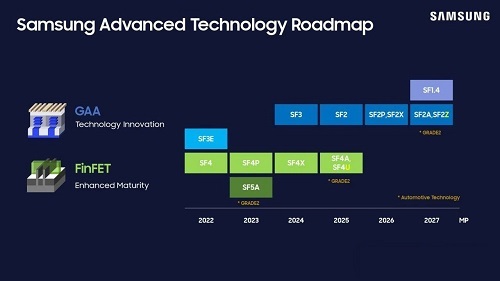

根據(jù)三星此前公布的工藝路線圖顯示,2nm SF2制程2025年推出,較第二代3GAP 3nm制程,相同運(yùn)計(jì)算頻率和復(fù)雜度情況下課降低25%功耗,相同功耗和復(fù)雜度情況下課提高12%計(jì)算性能,減少5%芯片面積。

接下來的2nm SF2Z 制程采用了優(yōu)化的背面供電網(wǎng)絡(luò) (BSPDN) 技術(shù),該技術(shù)將電源軌置于晶圓背面,以消除電源線和信號線之間的瓶頸。與第一代 2nm 節(jié)點(diǎn) SF2 相比,將 BSPDN 技術(shù)應(yīng)用于 SF2Z 不僅可以提高功率、性能和面積 (PPA),還可以顯著降低電壓降 (IR 降),從而提高 HPC 設(shè)計(jì)的性能。SF2Z 預(yù)計(jì)將于 2027 年實(shí)現(xiàn)量產(chǎn)。

三星還公布了其他 2nm 工藝的發(fā)布日期。用于移動領(lǐng)域的 SF2 和 SF2P 將分別于 2025 年和 2026 年推出。針對人工智能和高性能計(jì)算的 2nm 工藝將于 2026 年推出,早于 BSPDN 工藝。該公司還將于 2027 年推出用于汽車的 SF2A 工藝。