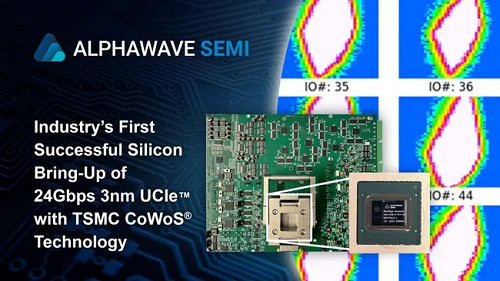

8 月 1 日消息,Alphawave Semi 公司最新研發(fā)出業(yè)界首款 3nm UCIe 芯粒(chiplet),為采用臺(tái)積電 CoWoS 封裝技術(shù)的系統(tǒng)級(jí)封裝(system-in-packages,SiP)實(shí)現(xiàn) die-to-die 連接。

該 3 納米芯粒支持 8 Tbps / mm 的帶寬密度,采用臺(tái)積電 CoWoS 2.5D 硅中介層(silicon-interposer-based)封裝,包含物理層和控制器 IP,支持 PCIe、CXL、AXI-4、AXI-S、CXS 和 CHI 等多種協(xié)議。

Alphawave Semi 的 UCIe 子系統(tǒng) IP 符合最新的 UCIe 規(guī)范 Rev 1.1,并配備了廣泛的測(cè)試和調(diào)試功能,包括 JTAG、BIST、DFT 和 Known Good Die(KGD)功能。

簡(jiǎn)要介紹下本文中涉及的相關(guān)專(zhuān)有名詞:

· Die:裸晶,是以半導(dǎo)體材料制作而成、未經(jīng)封裝的一小塊集成電路本體,該集成電路的既定功能就是在這一小片半導(dǎo)體上實(shí)現(xiàn)。

· Chiplet:芯粒是一個(gè)微型集成電路,包含明確定義的功能子集。它被設(shè)計(jì)為與單個(gè)封裝內(nèi)插器上的其他小芯片結(jié)合在一起。一組芯粒可以在混合搭配“樂(lè)高式”堆疊組件中實(shí)現(xiàn)。

· UCIe:全稱(chēng)為 Universal Chiplet Interconnect Express,譯為通用芯粒互連,是一種開(kāi)放規(guī)格,適用于芯粒之間的裸晶互連與序列總線(xiàn)。

· CoWoS:可以分成“CoW”和“WoS”來(lái)看:“CoW(Chip-on-Wafer)”是芯片堆疊;“WoS(Wafer-on-Substrate)”則是將芯片堆疊在基板上。

系統(tǒng)級(jí)封裝:一種集成電路封裝的概念,是將一個(gè)系統(tǒng)或子系統(tǒng)的全部或大部分電子功能配置在集成型襯底內(nèi),而芯片以 2D、3D 的方式接合到集成型襯底的封裝方式。