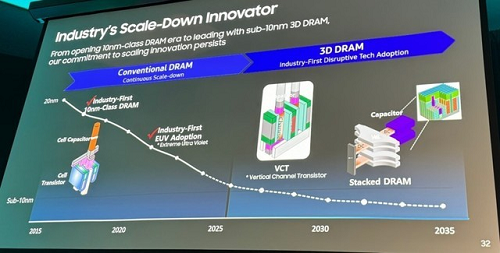

8月13日消息,據(jù)Thelec報道,SK 海力士研究員Seo Jae Wook 周一在韓國首爾舉辦的產(chǎn)業(yè)會議中指出,自從1c納米制程DRAM 商業(yè)化之后,極紫外光(EUV)光刻制程成本將快速攀升,SK海力士計劃開發(fā)3D DRAM以進(jìn)一步控制成本。

Seo Jae Wook 認(rèn)為,現(xiàn)在是確認(rèn)使用EUV制造DRAM 是否有利可圖的時刻,目前公司考慮未來DRAM 制造采用垂直柵極(VG)技術(shù),即所謂的“3D DRAM”。

所謂的垂直柵極技術(shù)是DRAM制造商內(nèi)部所稱的“4F2”結(jié)構(gòu),這是一種經(jīng)過大量研究的單元陣列結(jié)構(gòu),其中晶體管以垂直方式堆疊,也就是3D DRAM。三星將這種3D DRAM 稱為“垂直通道晶體管”(vertical channel transistor,簡稱VCT)。

4F2結(jié)構(gòu)從下而上依序為源極(source)、閘極(gate)、汲極(drain)和電容器(capacitor)。字元線(Word Line)連接到閘極,位元線(Bit Line)則連接到源極。與6F2 DRAM 相比,采用這種單元陣列可將芯片表面面積減少30%。

知情人士表示,三星和SK 海力士目標(biāo)是10nm制程以下的DRAM 應(yīng)用4F2 技術(shù)。 SK 海力士的Seo Jae Wook 認(rèn)為,采用VG 或3D DRAM 制程設(shè)計,可將EUV 制程成本降一半。

三星此前宣布成功將3D DRAM 堆疊到16 層,但表示現(xiàn)在不是量產(chǎn)階段,而是可行性驗證階段。