12月8日消息,在近日的IEDM 2024(2024年IEEE國(guó)際電子器件會(huì)議)上,英特爾代工展示了多項(xiàng)技術(shù)突破,助力推動(dòng)半導(dǎo)體行業(yè)在下一個(gè)十年及更長(zhǎng)遠(yuǎn)的發(fā)展。

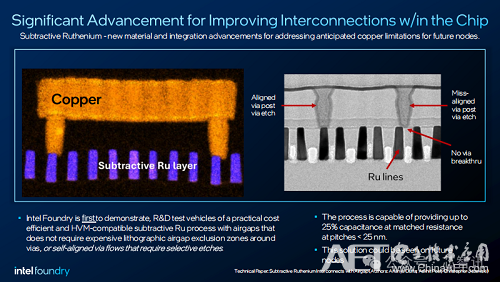

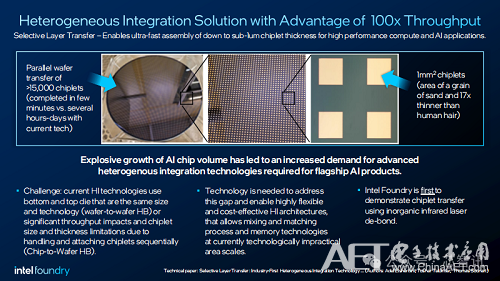

具體而言,在新材料方面,減成法釕互連技術(shù)(subtractive Ruthenium)最高可將線間電容降低25%,有助于改善芯片內(nèi)互連。英特爾代工還率先匯報(bào)了一種用于先進(jìn)封裝的異構(gòu)集成解決方案,能夠?qū)⑼掏铝刻嵘哌_(dá)100倍,實(shí)現(xiàn)超快速的芯片間封裝(chip-to-chip assembly)。

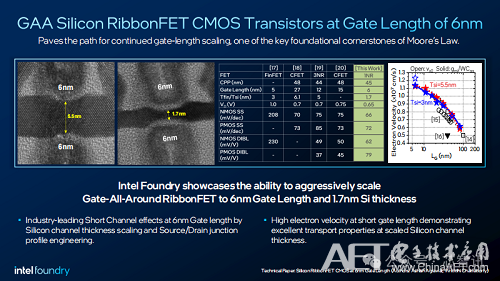

此外,為了進(jìn)一步推動(dòng)全環(huán)繞柵極(GAA)的微縮,英特爾代工展示了硅基RibbionFET CMOS (互補(bǔ)金屬氧化物半導(dǎo)體)技術(shù),以及用于微縮的2D場(chǎng)效應(yīng)晶體管(2D FETs)的柵氧化層(gate oxide)模塊,以提高設(shè)備性能。

隨著行業(yè)朝著到2030年在單個(gè)芯片上實(shí)現(xiàn)一萬(wàn)億個(gè)晶體管的目標(biāo)前進(jìn),晶體管和互連微縮技術(shù)的突破以及未來(lái)的先進(jìn)封裝能力正變得非常關(guān)鍵,以滿足人們對(duì)能效更高、性能更強(qiáng)且成本效益更高的計(jì)算應(yīng)用(如AI)的需求。

我們還需要探索新型的材料,來(lái)增強(qiáng)英特爾代工的PowerVia背面供電技術(shù)在緩解互連瓶頸,實(shí)現(xiàn)晶體管的進(jìn)一步微縮中的作用。這對(duì)于持續(xù)推進(jìn)摩爾定律、推動(dòng)面向AI時(shí)代的半導(dǎo)體創(chuàng)新至關(guān)重要。

英特爾代工已經(jīng)探索出數(shù)條路徑,以解決采用銅材料的晶體管在開(kāi)發(fā)未來(lái)制程節(jié)點(diǎn)時(shí)可預(yù)見(jiàn)的互連微縮限制,改進(jìn)現(xiàn)有封裝技術(shù),并繼續(xù)為GAA及其它相關(guān)技術(shù)定義和規(guī)劃晶體管路線圖:

·減成法釕互連技術(shù):為了提升芯片性能,改善互連,英特爾代工展示了減成法釕互連技術(shù)。通過(guò)采用釕這一新型、關(guān)鍵、替代性的金屬化材料,利用薄膜電阻率(thin film resistivity)和空氣間隙(airgap),實(shí)現(xiàn)了在互連微縮方面的重大進(jìn)步。英特爾代工率先在研發(fā)測(cè)試設(shè)備上展示了一種可行、可量產(chǎn)、具有成本效益的減成法釕互連技術(shù),該工藝引入空氣間隙,無(wú)需通孔周圍昂貴的光刻空氣間隙區(qū)域(lithographic airgap exclusion zone),也可以避免使用選擇性蝕刻的自對(duì)準(zhǔn)通孔(self-aligned via)。在間距小于或等于 25 納米時(shí),采用減成法釕互連技術(shù)實(shí)現(xiàn)的空氣間隙使線間電容最高降低 25%,這表明減成法釕互連技術(shù)作為一種金屬化方案,在緊密間距層中替代銅鑲嵌工藝的優(yōu)勢(shì)。這一解決方案有望在英特爾代工的未來(lái)制程節(jié)點(diǎn)中得以應(yīng)用。

·選擇性層轉(zhuǎn)移(Selective Layer Transfer, SLT):為了在芯片封裝中將吞吐量提升高達(dá)100倍,進(jìn)而實(shí)現(xiàn)超快速的芯片間封裝,英特爾代工首次展示了選擇性層轉(zhuǎn)移技術(shù),這是一種異構(gòu)集成解決方案,能夠以更高的靈活性集成超薄芯粒,與傳統(tǒng)的芯片到晶圓鍵合(chip-to-wafer bonding)技術(shù)相比,選擇性層轉(zhuǎn)移讓芯片的尺寸能夠變得更小,縱橫比變得更高。這項(xiàng)技術(shù)還帶來(lái)了更高的功能密度,并可結(jié)合混合鍵合(hybrid bonding)或融合鍵合(fusion bonding)工藝,提供更靈活且成本效益更高的解決方案,封裝來(lái)自不同晶圓的芯粒。該解決方案為AI應(yīng)用提供了一種更高效、更靈活的架構(gòu)。

·硅基RibbonFET CMOS晶體管:為了將RibbonFET GAA晶體管的微縮推向更高水平,英特爾代工展示了柵極長(zhǎng)度為6納米的硅基RibbonFET CMOS晶體管,在大幅縮短?hào)艠O長(zhǎng)度和減少溝道厚度的同時(shí),在對(duì)短溝道效應(yīng)的抑制和性能上達(dá)到了業(yè)界領(lǐng)先水平。這一進(jìn)展為摩爾定律的關(guān)鍵基石之一——柵極長(zhǎng)度的持續(xù)縮短——鋪平了道路。

·用于微縮的2D GAA晶體管的柵氧化層:為了在CFET(互補(bǔ)場(chǎng)效應(yīng)晶體管)之外進(jìn)一步加速GAA技術(shù)創(chuàng)新,英特爾代工展示了其在2D GAA NMOS(N 型金屬氧化物半導(dǎo)體)和PMOS(P 型金屬氧化物半導(dǎo)體)晶體管制造方面的研究,側(cè)重于柵氧化層模塊的研發(fā),將晶體管的柵極長(zhǎng)度微縮到了30納米。該研究還報(bào)告了行業(yè)在2D TMD(過(guò)渡金屬二硫化物)半導(dǎo)體領(lǐng)域的研究進(jìn)展,此類材料未來(lái)有望在先進(jìn)晶體管工藝中成為硅的替代品。

在300毫米GaN(氮化鎵)技術(shù)方面,英特爾代工也在繼續(xù)推進(jìn)其開(kāi)拓性的研究。GaN是一種新興的用于功率器件和射頻(RF)器件的材料,相較于硅,它的性能更強(qiáng),也能承受更高的電壓和溫度。在300毫米GaN-on-TRSOI(富陷阱絕緣體上硅)襯底(substrate)上,英特爾代工制造了業(yè)界領(lǐng)先的高性能微縮增強(qiáng)型GaN MOSHEMT(金屬氧化物半導(dǎo)體高電子遷移率晶體管)。GaN-on-TRSOI等工藝上較為先進(jìn)的襯底,可以通過(guò)減少信號(hào)損失,提高信號(hào)線性度和基于襯底背部處理的先進(jìn)集成方案,為功率器件和射頻器件等應(yīng)用帶來(lái)更強(qiáng)的性能。

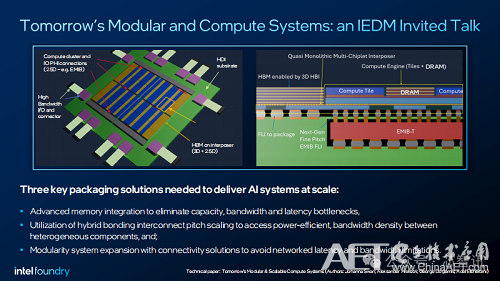

此外,在IEDM 2024上,英特爾代工還分享了對(duì)先進(jìn)封裝和晶體管微縮技術(shù)未來(lái)發(fā)展的愿景,以滿足包括AI在內(nèi)的各類應(yīng)用需求,以下三個(gè)關(guān)鍵的創(chuàng)新著力點(diǎn)將有助于AI在未來(lái)十年朝著能效更高的方向發(fā)展:

·先進(jìn)內(nèi)存集成(memory integration),以消除容量、帶寬和延遲的瓶頸;

·用于優(yōu)化互連帶寬的混合鍵合;

·模塊化系統(tǒng)(modular system)及相應(yīng)的連接解決方案

同時(shí),英特爾代工還發(fā)出了行動(dòng)號(hào)召,開(kāi)發(fā)關(guān)鍵性和突破性的創(chuàng)新,持續(xù)推進(jìn)晶體管微縮,推動(dòng)實(shí)現(xiàn)“萬(wàn)億晶體管時(shí)代”。英特爾代工概述了對(duì)能夠在超低電壓(低于300毫伏)下運(yùn)行的晶體管的研發(fā),將如何有助于解決日益嚴(yán)重的熱瓶頸,并大幅改善功耗和散熱。