12 月 12 日消息,據(jù) IBM 官方當(dāng)?shù)貢r(shí)間 9 日博客,IBM 和日本先進(jìn)芯片制造商 Rapidus 在 2024 IEEE IEDM 國(guó)際電子器件會(huì)議上展示了兩方合作的多閾值電壓 GAA 晶體管研發(fā)成果,這些技術(shù)突破有望用于 Rapidus 的 2nm 制程量產(chǎn)。

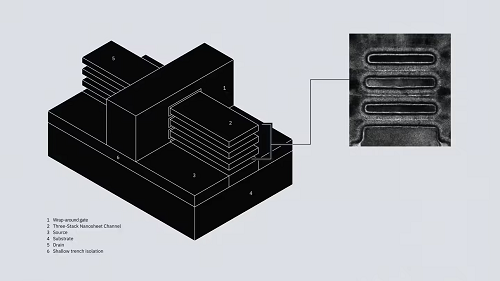

IBM 表示,先進(jìn)制程升級(jí)至 2nm 后,晶體管的結(jié)構(gòu)由使用多年的 FinFET(IT之家注:鰭式場(chǎng)效應(yīng)晶體管)轉(zhuǎn)為 GAAFET(全環(huán)繞柵極場(chǎng)效應(yīng)晶體管),這對(duì)制程迭代帶來了新的挑戰(zhàn):如何實(shí)現(xiàn)多閾值電壓(Multi Vt)從而讓芯片以較低電壓執(zhí)行復(fù)雜計(jì)算。

2nm 名義制程下 N 型和 P 型半導(dǎo)體通道之間的距離相當(dāng)狹窄,需要精確的光刻才能在實(shí)現(xiàn)多閾值電壓的同時(shí)不會(huì)對(duì)半導(dǎo)體的性能產(chǎn)生巨大影響,而 IBM、Rapidus 導(dǎo)入了兩種不同的選擇性減少層(SLR)芯片構(gòu)建工藝,成功達(dá)成了目標(biāo)效果。

IBM 研究院高級(jí)技術(shù)人員 Bao Ruqiang 表示:

與上一代 FinFET 相比,Nanosheet 納米片的結(jié)構(gòu)非常不同,而且可能更復(fù)雜。

我們提出的新生產(chǎn)工藝比以前使用的方法更簡(jiǎn)單,我們相信這將使我們的合作伙伴 Rapidus 更容易可靠地大規(guī)模使用 2 納米片技術(shù)制造芯片。