摘 要: 一種在計算機工業(yè)測控系統(tǒng)中應(yīng)用FPGA和軟IP核" title="IP核">IP核實現(xiàn)PCI總線" title="PCI總線">PCI總線接口的方法。重點介紹了本地總線讀寫狀態(tài)機的設(shè)計,3.3V FPGA兼容PCI2.2、5V規(guī)范的電氣設(shè)計及其時序和布線問題,并給出了使用嵌入式邏輯分析儀實際捕獲的信號時序。實驗證明,該結(jié)構(gòu)的PCI接口測控系統(tǒng)工作穩(wěn)定可靠。

關(guān)鍵詞: 現(xiàn)場可編程門陣列 IP核 PCI總線

PCI總線是高性能的32/64位同步總線,具有嚴(yán)格的規(guī)范保證數(shù)據(jù)傳輸?shù)目煽啃裕瑸樘幚砥髋c高集成度的外圍設(shè)備提供高速安全的接口,是迄今為止最成功的總線規(guī)范之一。

由于PCI總線協(xié)議非常復(fù)雜,目前實現(xiàn)PCI總線接口主要使用兩種方式:(1)采用專用接口芯片,如AMCC公司的S5933和PLX公司的9054、9080。使用接口芯片開發(fā)人員可以不考慮PCI接口的實現(xiàn)問題,但是在實際應(yīng)用中通常只用到接口芯片的部分功能,造成了資源的浪費。同時接口芯片占用了板卡上的有限空間,給應(yīng)用設(shè)計帶來不便。(2)使用可編程邏輯器件實現(xiàn)PCI總線控制器。使用這種方式開發(fā)難度大,消耗周期長,系統(tǒng)驗證困難,且不具備通用性。

隨著IC產(chǎn)業(yè)的迅速發(fā)展,傳統(tǒng)的、基于標(biāo)準(zhǔn)單元的數(shù)字IC設(shè)計方法已經(jīng)發(fā)展到基于IP(知識產(chǎn)權(quán))復(fù)用的SoC設(shè)計方法。根據(jù)實現(xiàn)的硬件描述級的不同,IP核分為軟核、硬核和固核。其中軟核是采用可綜合的HDL實現(xiàn)的RTL級設(shè)計,與具體實現(xiàn)工藝無關(guān),相比于固核和硬核具有較大的靈活性。在FPGA中定制PCI接口軟核實現(xiàn)PCI接口控制具有明顯的優(yōu)勢:可以在單片F(xiàn)PGA中同時完成PCI接口和用戶邏輯的設(shè)計,縮減成本,提高集成度,減少資源浪費;實現(xiàn)32/64位的PCI、PCI-X及兼容Compact PCI的PCI主設(shè)備/目標(biāo)設(shè)備接口;消除PCI接口芯片與本地通信的信號線的硬線連接,提高用戶邏輯設(shè)計的彈性,降低因硬件設(shè)計不當(dāng)造成的損失;統(tǒng)一設(shè)計工具和平臺,縮短開發(fā)周期。

本文應(yīng)用PCI接口控制IP實現(xiàn)了PCI多卡測控系統(tǒng)中PCI總線到本地總線的轉(zhuǎn)換。實際應(yīng)用表明,采用此設(shè)計方案的PCI卡運行穩(wěn)定可靠。

1 應(yīng)用背景

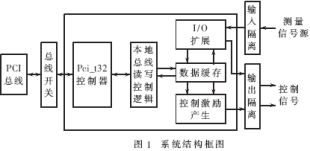

本文的應(yīng)用背景為某一工業(yè)測控系統(tǒng)。該系統(tǒng)采用FPGA實現(xiàn)測量數(shù)據(jù)的采集和控制信號的輸出,通過定制PCI接口IP實現(xiàn)一個32位目標(biāo)設(shè)備的PCI總線接口轉(zhuǎn)換。PCI核選用Altera PCI編譯器所包括的pci_t32兆核函數(shù)。FPGA選用Altera公司的Cyclone系列芯片ep1c6q240c8,以配合32位/33MHz的PCI接口的I/O標(biāo)準(zhǔn)和速度要求。在硬件設(shè)計上,為保證3.3V FPGA對PCI 2.2、5V總線的兼容性要求,在PCI總線接口與FPGA引腳間加入總線開關(guān)進(jìn)行電平轉(zhuǎn)換。由于系統(tǒng)應(yīng)用在工業(yè)生產(chǎn)控制場合,因此FPGA與外部數(shù)據(jù)的I/O接口間需加入光電隔離器件以增強系統(tǒng)的抗干擾能力。系統(tǒng)結(jié)構(gòu)如圖1所示。

2 PCI接口兆核函數(shù)

Altera的PCI編譯器(PCI Compiler)提供了使用Altera器件實現(xiàn)PCI接口設(shè)計的完全解決方案,包括4個32/64位、主/從模式PCI接口控制器兆核函數(shù)(即接口IP)及相關(guān)測試平臺。通過選擇合適的芯片速度,可以滿足運行在33MHz或66MHz PCI時鐘下的時序要求。支持Altera的Stratix Ⅱ、Stratix、Stratix GX、Cyclone、Cyclone Ⅱ和MAX Ⅱ系列器件;支持PCI配置空間讀寫、內(nèi)存方式讀寫和I/O方式讀寫;支持預(yù)先讀取模式;支持可參數(shù)化的配置寄存器,包括參數(shù)化的設(shè)備信息、6個可變長度的基址空間和一個擴展ROM空間;具有奇偶校驗檢錯;支持PCI終止、重試和斷開作業(yè)及中斷操作,并提供靈活的本地端接口。pci_t32兆核函數(shù)是32位目標(biāo)設(shè)備控制器,其結(jié)構(gòu)和總線接口信號如圖2所示。

在PCI總線端,IP核提供32位數(shù)據(jù)線和目標(biāo)設(shè)備控制信號、中斷請求信號及錯誤報告信號;本地總線端提供32位數(shù)據(jù)線和地址線、控制信號、中斷輸入信號和狀態(tài)表示信號接口。其中,本地端信號l_adi為地址/數(shù)據(jù)輸入,l_adro為地址輸出,l_dato為數(shù)據(jù)輸出,l_beno為字節(jié)使能輸出,l_cmdo為本地命令輸出。控制信號lt_abortn、lt_discn和lt_rdyn為本地端輸入,分別標(biāo)志本地設(shè)備終止、斷開和準(zhǔn)備好,lt_framen、lt_ackn和lt_dxfrn為目標(biāo)傳輸控制信號,相當(dāng)于PCI總線的frame#、devsel#和trdy#。lt_tsr為目標(biāo)作業(yè)狀態(tài)寄存器輸出。lirqn為中斷輸入信號。

可以通過PCI編譯器IP工具臺或編輯兆核函數(shù)頭文件的方式修改PCI配置空間信息。本系統(tǒng)PCI兆核函數(shù)的配置信息如下:

CLASS_CODE=24′hFF0000

DEVICE_ID=16′h1100

VENDOR_ID=16′h1172,為Altera的廠商編號

REVISION_ID=8′h01

BAR0=32′hFFFFFC00,BAR0空間為1KB,使用內(nèi)存方式讀寫

NUMBER_OF_BARS=32′h00000001

INTERRUPT_PIN_REG=8′h00,未使用中斷

3 本地總線讀寫狀態(tài)機

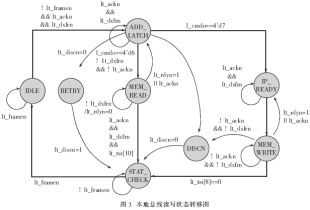

在用戶邏輯中,通過總線讀寫狀態(tài)機實現(xiàn)內(nèi)存方式單周期或迸發(fā)讀寫、I/O單周期或迸發(fā)讀寫以及在設(shè)備不能完成作業(yè)時發(fā)起(目標(biāo))或響應(yīng)(主)終止、斷開或重試等作業(yè),保證PCI作業(yè)正確結(jié)束。以帶迸發(fā)模式的內(nèi)存讀寫作業(yè)為例,作為目標(biāo)設(shè)備的本地總線讀寫狀態(tài)轉(zhuǎn)移圖如圖3所示。

IDLE為設(shè)備空閑狀態(tài)。

ADD_LATCH為地址鎖定狀態(tài)。lt_framen有效表示IP核接到一次PCI讀寫作業(yè)并啟動本地端做出響應(yīng),此時目標(biāo)設(shè)備鎖存地址l_adro及命令l_cmdo,并對命令做出解釋。l_cmdo的值為6,則進(jìn)入MEMORY_READ狀態(tài);為7,則進(jìn)入IP_READY狀態(tài);其他值,則使能lt_discn并進(jìn)入RETRY狀態(tài)。

MEM_READ為內(nèi)存讀作業(yè)狀態(tài),lt_ackn有效驅(qū)使目標(biāo)設(shè)備將數(shù)據(jù)放到總線上;如為迸發(fā)方式,則lt_rdyn和lt_dxfrn持續(xù)有效,驅(qū)使目標(biāo)設(shè)備連續(xù)將地址相連的數(shù)據(jù)輸出。如目標(biāo)設(shè)備在迸發(fā)作業(yè)中需延緩迸發(fā)作業(yè),則可使lt_rdyn無效來加入等待周期,此時狀態(tài)機回到ADD_LATCH狀態(tài),直到目標(biāo)設(shè)備再次準(zhǔn)備好,并同時使lt_rdyn有效并輸出數(shù)據(jù)。

RETRY為設(shè)備重試狀態(tài)。在作業(yè)開始,目標(biāo)設(shè)備尚未準(zhǔn)備好發(fā)送或接收數(shù)據(jù),則發(fā)起一次重試作業(yè),即在lt_framen有效后使lt_discn有效并等待主設(shè)備結(jié)束作業(yè)。

DISCN為設(shè)備斷開狀態(tài)。在迸發(fā)讀寫作業(yè)中,目標(biāo)設(shè)備檢測到地址超出有效范圍,則發(fā)起目標(biāo)斷開作業(yè);在迸發(fā)寫作業(yè)中斷開,在最后一次有效寫數(shù)據(jù)前一時鐘使lt_discn有效。在迸發(fā)讀作業(yè)中,將最后一個數(shù)據(jù)放在總線上的同時使lt_discn有效。

IP_READY為內(nèi)存寫操作IP核準(zhǔn)備傳輸數(shù)據(jù)狀態(tài)。

MEM_WRITE為內(nèi)存寫作業(yè)狀態(tài)。在同時使能lt_rdyn后等待lt_ackn和lt_dxfrn有效時讀取總線上的數(shù)據(jù)l_dato,迸發(fā)寫或加入等待周期的時序與讀作業(yè)類似。

STAT_CHECK為狀態(tài)檢測。lt_ackn和lt_dxfrn同時無效標(biāo)志著內(nèi)存單次/迸發(fā)讀作業(yè)完成,然后檢測作業(yè)狀態(tài)寄存器lt_tsr并返回IDLE狀態(tài)。

在每一次作業(yè)開始,都啟動計數(shù)器,防止操作超時。

使用SignalTap II嵌入式邏輯分析儀實際捕獲的PCI內(nèi)存讀寫作業(yè)的PCI和本地總線信號時序圖如圖4所示,采樣時鐘為PCI總線時鐘。

4 PCI電氣特性要求設(shè)計

由于目前絕大多數(shù)主板采用5V的PCI規(guī)范,而Altera的Cyclone系列FPGA的I/O口電壓只支持3.3V,因此需要在FPGA和PCI連接器間加入電平轉(zhuǎn)換電路。

實現(xiàn)電平轉(zhuǎn)換的原理是在總線間加入NMOS總線開關(guān),實現(xiàn)方式如圖5所示。

其中總線開關(guān)選用IDT公司的QS3861。首先,考慮電平轉(zhuǎn)換的實現(xiàn)方法。當(dāng)總線選通信號BE#使能,總線A的輸入電壓上升,總線B的電壓隨之上升。當(dāng)總線A的電壓超過vcc-Vt(Vt的典型值為1V)時,總線B的電壓將被箝位到vcc-Vt,而不會繼續(xù)上升。因此選擇vcc為4.3V,則能保證總線B的信號滿足3.3V標(biāo)準(zhǔn)。當(dāng)3.3V總線B驅(qū)動總線A時,由于5V PCI規(guī)范中定義的邏輯高電壓是2V~5.5V,因此也能夠保證FPGA端驅(qū)動PCI的高電壓要求。

其次,驗證是否滿足PCI時序要求。PCI2.2協(xié)議規(guī)定一個時鐘周期分為4部分:

t(30ns)=tval+tprop+tsu+tskew

其中:tval為時鐘到輸出信號有效延遲,tsu為輸入建立時間,tpro為最大總線傳輸時間,tskew為時鐘抖動時間。PCI 2.2協(xié)議規(guī)定的保持時間為0。tprop是由于PCI總線采用反射波技術(shù)引入的,典型值為10ns,tprop與tskew的和不超過12ns。PCI 2.2規(guī)范規(guī)定33MHz信號的建立時間為7ns,66MHz信號的建立時間為3ns。由QS3861引入的數(shù)據(jù)傳輸延遲為0.25ns。但由于所有PCI信號都經(jīng)過總線開關(guān)進(jìn)行電平轉(zhuǎn)換,到達(dá)FPGA的信號整體只有0.25ns的延遲,因此FPGA的建立時間仍然設(shè)置為7ns。FPGA經(jīng)過運算輸出的信號時序由時鐘到信號有效延遲tval所限定。PCI 2.2規(guī)范規(guī)定33MHz時tval最大為11ns,最小為2ns。由于電平轉(zhuǎn)換芯片在雙向數(shù)據(jù)通路的延遲累加,F(xiàn)PGA必須保證時鐘到信號最大延遲在10.5ns以內(nèi)。

最后,考慮布局布線因素。在加入總線開關(guān)后,要保證從PCI連接器到總線開關(guān)及總線開關(guān)到FPGA的所有32位信號線(除中斷輸入信號、系統(tǒng)信號和JTAG信號)的走線長度和不大于1.5英寸,時鐘線長度和為2.5±0.1英寸。

在FPGA中定制IP核實現(xiàn)PCI總線到本地總線的轉(zhuǎn)換,能夠有效節(jié)約PCI設(shè)備的成本,提高硬件資源利用率,縮短開發(fā)時間。目標(biāo)設(shè)備讀寫狀態(tài)機對本地總線進(jìn)行監(jiān)測,完成設(shè)備的內(nèi)存、I/O讀寫并提供迸發(fā)作業(yè)支持,在發(fā)生異常狀況時,及時發(fā)起重試、斷開或終止作業(yè),保證PCI總線傳輸正確結(jié)束,防止不安全的數(shù)據(jù)操作出現(xiàn)。為了滿足PCI電氣規(guī)范,在硬件設(shè)計時需要注意3.3V設(shè)備掛接5V總線的電平轉(zhuǎn)換及其帶來的時序和布線問題。

參考文獻(xiàn)

1 任愛鋒.基于FPGA的嵌入式系統(tǒng)設(shè)計.西安:西安電子科技大學(xué)出版社,2004

2 PCI Compiler User Guide(Version 3.2.0).Altera Corporation,2004

3 Connecting Altera 3.3-V PCI devices to a 5-V PCI Bus (Version 1.0).Altera Corporation,2004

4 PCI Local Bus Specification(Revision 2.2).PCI SIG,1998