0 引言

鎖相環(huán)簡稱PLL" target="_blank">PLL,是實現(xiàn)相位自動控制的一門技術(shù),早期是為了解決接收機的同步接收問題而開發(fā)的,后來應(yīng)用在電視機的掃描電路中。由于鎖相技術(shù)的發(fā)展,該技術(shù)已逐漸應(yīng)用到通信、導(dǎo)航、雷達、計算機到家用電器的各個領(lǐng)域。自從20世紀70年代起,隨著集成電路的發(fā)展,開始出現(xiàn)集成的鎖相環(huán)器件、通用和專用集成單片鎖相環(huán),使鎖相環(huán)逐漸變成一個低成本、使用簡便的多功能器件。如今,PLL技術(shù)主要應(yīng)用在調(diào)制解調(diào)、頻率合成、彩電色幅載波提取、雷達、FM立體聲解碼等各個領(lǐng)域。隨著數(shù)字技術(shù)的發(fā)展,還出現(xiàn)了各種數(shù)字PLL器件,它們在數(shù)字通信中的載波同步、位同步、相干解調(diào)等方面起著重要的作用。

隨著現(xiàn)代電子技術(shù)的飛快發(fā)展,具有高穩(wěn)定性和準確度的頻率源已經(jīng)成為科研生產(chǎn)的重要組成部分。高性能的頻率源可通過頻率合成技術(shù)獲得。隨著大規(guī)模集成電路的發(fā)展,鎖相式頻率合成技術(shù)占有越來越重要的地位。由一個或幾個高穩(wěn)定度、高準確度的參考頻率源通過數(shù)字鎖相頻率合成技術(shù)可獲得高品質(zhì)的離散頻率源。

1 鎖相環(huán)及頻率合成器的原理

1.1 鎖相環(huán)原理

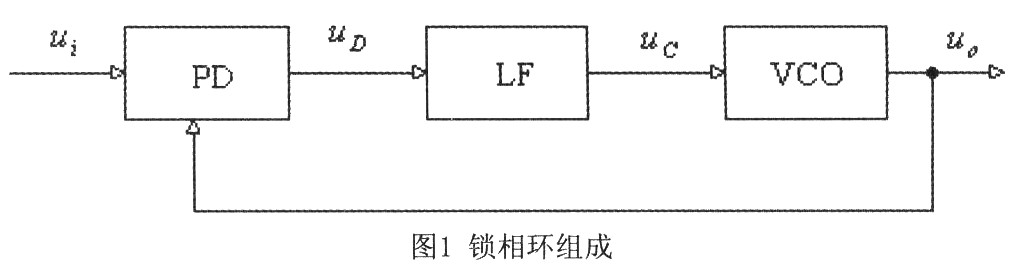

PLL是一種反饋控制電路,其特點是:利用外部輸入的參考信號控制環(huán)路內(nèi)部振蕩信號的頻率和相位。因PLL可以實現(xiàn)輸出信號頻率對輸入信號頻率的自動跟蹤,所以PLL通常用于閉環(huán)跟蹤電路。PLL在工作的過程中,當輸出信號的頻率與輸入信號的頻率相同時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是PLL名稱的由來。PLL通常由鑒相器(PD)、環(huán)路濾波器(LF)和壓控振蕩器(VCO)三部分組成,PLL組成的原理框圖如圖1所示。

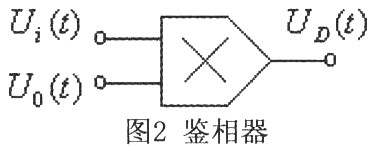

PLL中的鑒相器又稱為相位比較器,它的作用是檢測輸入信號和輸出信號的相位差,并將檢測出的相位差信號轉(zhuǎn)換成uD(t)電壓信號輸出,該信號經(jīng)低通濾波器濾波后形成壓控振蕩器的控制電壓uC(t),對振蕩器輸出信號的頻率實施控制。鑒相器通常由模擬乘法器組成,利用模擬乘法器組成的鑒相器電路如圖2所示。

鑒相器的工作原理是:設(shè)外界輸入的信號電壓和壓控振蕩器輸出的信號電壓分別為:

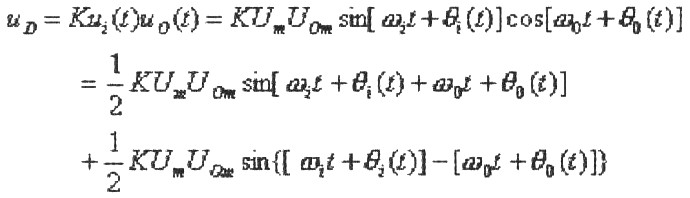

式中的ω0為壓控振蕩器在輸入控制電壓為零或為直流電壓時的振蕩角頻率,稱為電路的固有振蕩角頻率。則模擬乘法器的輸出電壓uD為:

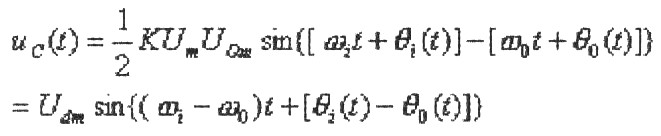

用低通濾波器LF將上式中的和頻分量濾掉,剩下的差頻分量作為壓控振蕩器的輸入控制電壓uC(t)。即uC(t)為:

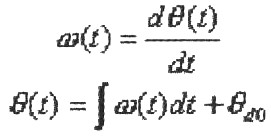

式中的ωi為輸入信號的瞬時振蕩角頻率,θ i(t)和θ 0(t)分別為輸入信號和輸出信號的瞬時位相,根據(jù)相量的關(guān)系可得瞬時頻率和瞬時位相的關(guān)系為:

即:

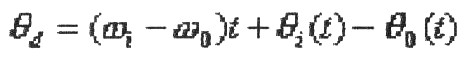

則瞬時相位差θd為:

對兩邊求微分,可得頻差的關(guān)系式為

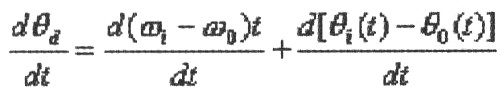

上式等于零,說明PLL進入相位鎖定狀態(tài),此時輸出和輸入信號的頻率和相位保持恒定不變的狀態(tài),uc(t)為恒定值。當上式不等于零時,說明PLL的相位還未鎖定,輸入信號和輸出信號的頻率不等,uc(t)隨時間而變。因壓控振蕩器的壓控特性如圖3所示,

該特性說明壓控振蕩器的振蕩頻率ωu以ω0為中心,隨輸入信號電壓uc(t)的變化而變化。該特性的表達式為

上式說明,當uc(t)隨時間而變時,壓控振蕩器的振蕩頻率ωu也隨時間而變,Pll進入"頻率牽引",自動跟蹤捕捉輸入信號的頻率,使PLL進入鎖定狀態(tài),并保持ω0=ω。

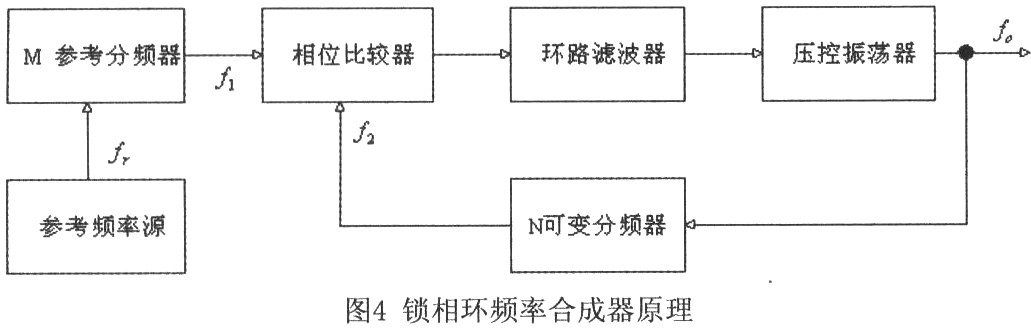

1.2 頻率合成器原理

如圖4所示,PLL頻率合成器是由參考頻率源、參考分頻器、相位比較器、環(huán)路濾波器、壓控振蕩器、可變分頻器構(gòu)成。參考分頻器對參考頻率源進行分頻,輸出信號作為相位比較器參考信號。可變分頻器對壓控振蕩器的輸出信號進行分頻,分頻之后返回到相位比較器輸入端與參考信號進行比較。當環(huán)路處于鎖定時,有f1=f2,因為f1=fr/M,f2=f0/N,所以有f0=Nfr/M。只要改變可變分頻器的分頻系數(shù)N,就可以輸出不同頻率的信號。

2 集成鎖相環(huán)CD4046電路介紹

CD4046是通用的CMOS鎖相環(huán)集成電路,其特點是電源電壓范圍寬(為3V~8V),輸入阻抗高(約100M Ω),動態(tài)功耗小,在中心頻率f0為10kHz下,功耗僅為600μW,屬微功耗器件。在電源電壓VDD=15V時最高頻率可達1.2MHz,常用在中、低頻段。CD4046內(nèi)部集成了相位比較器1、相位比較器2、壓控振蕩器以及線性放大器、源跟隨器、整形電路等。各引腳功能如下:

1腳是相位輸出端,環(huán)路人鎖時為高電平,環(huán)路失鎖時為低電平。2腳是相位比較器I的輸出端。3腳是比較信號輸入端。4腳是壓控振蕩器輸出端。5腳是禁止端,高電平時禁止,低電平時允許壓控振蕩器工作。6、7腳是外接振蕩電容端。8、16腳是電源的負端和正端。9腳是壓控振蕩器的控制端。10腳是解調(diào)輸出端,用于FM解調(diào)。11、12腳是外接振蕩電阻。13腳是相位比較器2的輸出端。14腳是信號輸入端。15腳是內(nèi)部獨立的齊納穩(wěn)壓管負極。圖5是CD4046內(nèi)部結(jié)構(gòu)圖,圖6是外圍電路連線圖。

相位比較器1采用異或門結(jié)構(gòu),使用時要求輸入信號占空比為50%。當兩路輸入信號的高低電平相異時,輸出信號為高電平,反之,輸出信號為低電平。相位比較器1的捕捉能力和濾波器有關(guān),選擇合適的濾波器可以得到較寬的捕捉范圍。相位比較器2由一個信號的上升沿控制,它對輸入信號的占空比要求不高,允許輸入非對稱波形,具有很寬的捕捉范圍。相位比較器2的輸出和兩路輸入信號的頻率高低有關(guān),當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏輯"0",反之則輸出邏輯"1"。如果兩信號的頻率相同而相位不同,當輸人信號的相位滯后于比較信號時,相位比較器2輸出的為正脈沖,當相位超前時則輸出為負脈沖。而當兩個輸入脈沖的頻率和相位均相同時,相位比較器2的輸出為高阻態(tài)。壓控振蕩器需要外接電阻R1、R2和電容C1。R1、C1是充放電元件,電阻R2起頻率補償作用。VCO的振蕩頻率不僅和R1、R以及C1的取值有關(guān),還和電源電壓有關(guān),電源電壓越高振蕩頻率越高。

3 頻率合成器外圍電路設(shè)計

3.1 參考頻率源

本設(shè)計中參考頻率源選用CMOS石英晶體多諧振蕩器-產(chǎn)生2MHz的矩形脈沖信號,電路如圖7所示。

3.2 可變分頻器

可變分頻器由集成四位二進制同步加法計數(shù)器74LS161來完成。這里采用4片74LS161通過預(yù)置數(shù)的方法來實現(xiàn)可變分頻。為提高工作速度,可采用圖8所示接法。利用同步方案最高可實現(xiàn)65536分頻。預(yù)制值=65536-N。經(jīng)過可變分頻后獲得的信號是窄脈沖信號,在輸出端可利用74LS74對該信號進行二分頻,以便獲得方波信號,從而滿足相位比較器1的占空比要求。此時實際分頻系數(shù)變?yōu)?N。電路如圖8所示。

參考分頻器與可變分頻器采用同樣的電路,目的在于通過設(shè)置不同的分頻系數(shù)M,以實現(xiàn)不同的頻率間隔的需求。

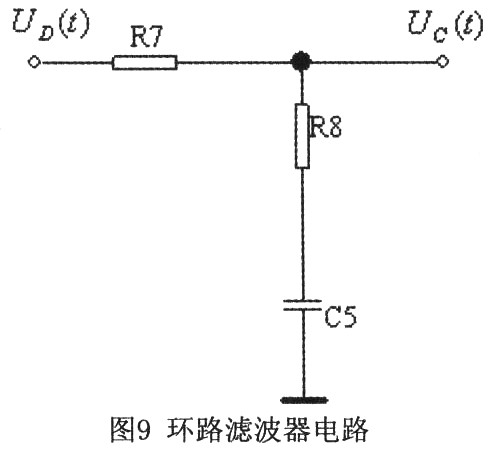

3.3 環(huán)路濾波

本設(shè)計選取無源比例積分濾波器作為環(huán)路濾波器,其時間常數(shù)T=(R7+R8)C5電路如圖9所示。

4 電路的調(diào)試

在調(diào)試的過程中需注意R1、R以及C1的選取,選取不同的R1、R、C1并合理設(shè)置可變分頻系數(shù)N就可獲得不同頻率范圍的輸出信號,同時根據(jù)所需情況選取合適的濾波器,設(shè)置不同的參考分頻系數(shù)即可改變頻率間隔。

5 結(jié)束語

本電路由于頻率范圍和頻率間隔可根據(jù)具體需要進行調(diào)節(jié),且輸出信號頻率具有高穩(wěn)定性和準確性,可廣泛作為離散信號源來使用,也可用于集成。此外,如用單片機對分頻器的置數(shù)端進行控制,可更加方便地實現(xiàn)頻率的調(diào)整。